Для магистратуры / Русские лекции по проектированию БИС / EDA_12_L-7

.pdf

56

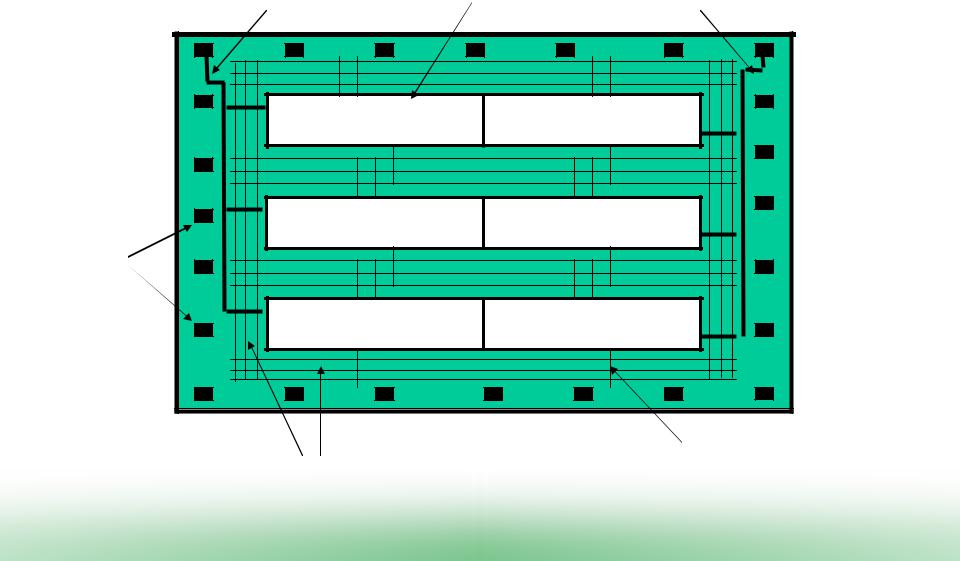

ПрограммируемаялогическаяИС |

||

Шина питания |

|

|

Ячейка |

|

Шина земли |

Блоки I/O |

|

|

Сигнальные шины |

Сигнальные шины |

|

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

|

Классификацияпредварительно |

60 |

|

|

смонтированныхматриц(prewired arrays ) |

|

По способу программирования:

На основе перемычек (fuse-based) (однократное программирование)

На энергонезависимой памяти (non-volatile EPROM based)

На основе ОЗУ (RAM based)

По реализации программируемых логических элементов

На основе матриц (Array-Based)

На основе таблиц истинности (Look-up Table)

По реализации способа межсоединений

Каналы соединений (Channel-routing)

Сети (Mesh networks)

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

Программируемыелогическиеинтегральныеьныесхемысхемы61

(ПЛИС) (Programmable Logic Device, PLD)

CPLD (Complex Pprogrammable Logic Device — сложные программируемые логические устройства) содержат относительно крупные программируемые логические блоки — макроячейки (macrocells), соединённые с внешними выводами и внутренними шинами.

Функциональность CPLD кодируется в энергонезависимой памяти, поэтому нет необходимости их перепрограммировать при включении.

Может применяться для расширения числа входов/выходов рядом с большими кристаллами, или для предобработки сигналов (например, контроллер COM-порта, USB, VGA).

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

62

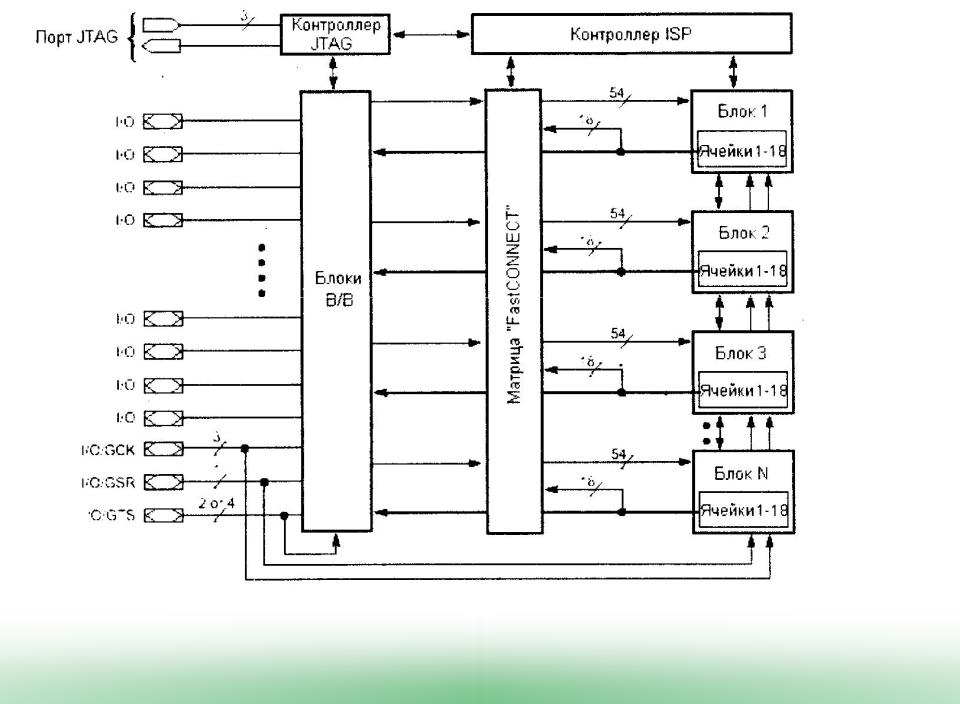

Структура ПЛИС CPLD XC9500XL

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

|

Программируемаялогическая |

интегральная схема |

59 |

|

ая схема |

||

(ПЛИС) (Programmable Logic Device, PLD)

ПЛИС широко используется для построения различных по сложности и возможностям цифровых устройств:

большое количество портов ввода-вывода (бывают ПЛИС с более чем 1000 выводов («пинов»)),

цифровая обработка сигнала (ЦОС), цифровая видеоаудиоаппаратура,

высокоскоростная передача данных, криптография,

проектирование и прототипирование ASIC,

в качестве мостов (коммутаторов) между системами с различной логикой и напряжением питания,

реализация нейрочипов.

ускорители универсальных процессоров в суперкомпьютерах

(например: Cray — XD1, SGI — Проект RASC).

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

59

Основными преимуществами ПЛИС при применении в средствах цифровой обработки сигналов (ЦОС) являются:

высокое быстродействие (достигло 250 –300 МГц, что позволяет реализовывать многие алгоритмы в радиодиапазоне) ;

возможность реализации сложных параллельных алгоритмов;

наличие средств САПР, позволяющих провести полное моделирование системы;

возможность программирования или изменения конфигурации непосредственно в системе;

совместимость при переводе алгоритмов на уровне языков описания аппаратуры (VHDL, AHDL, Verilog и др.)

совместимость по уровням и возможность реализации стандартного интерфейса.

наличие библиотек мегафункций, описывающих сложные алгоритмы;

архитектурные особенности ПЛИС как нельзя лучше приспособлены для реализации таких операций, как умножение, свертка и т.п.

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

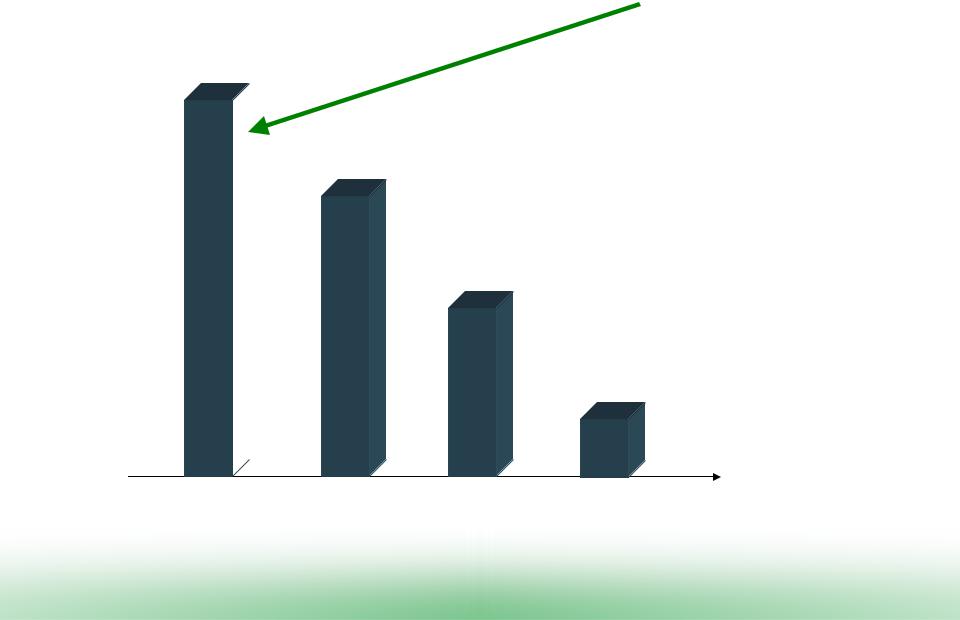

Альтернативы ПЛИС : |

58 |

|

|

БМК -> |

|

-> (требуют заводского производственного процесса для |

|

программирования); |

|

Заказные ASIC — специализированные СБИС -> |

|

-> (при мелкосерийном и единичном производстве |

|

существенно дороже); |

|

Полузаказные ASIC СБИС на основе библиотек стандартных

элементов -> -> (при мелкосерийном и единичном производстве намного

дороже)

Специализированные компьютеры, процессоры (например,

цифровой сигнальный процессор) или микроконтроллеры ->,

-> (которые из-за программного способа реализации алгоритмов существенно медленнее ПЛИС)

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

ВыборвариантареализацииТЗ:

Эффективность исп. энергии (MOPS/mW)

100-1000

Заказная (ASIC)микросхема

нет

|

приложений |

|

|

10-100 |

Процессор для |

(напр., ЦСП) |

|

структураКонфигурируемая |

|||

1-10 |

|||

|

|||

|

средняя |

|

|

Встроенный микропроцессор

0.1-1

полная

3

Application-Specific

Integrated Circuit -

проблемноориентированная (специализированная) интегральная микросхема, заказная ИС, ay-sic.

Гибкость настройки применений

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

44

Реализациинаосновематриц

ИС на матрицах

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вентильные |

|

|

программируемые |

|

||

|

|

|

|

||||

|

(с предварительной |

|

|

(с предварительным |

|

||

|

диффузией) |

|

|

монтажом) |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

46

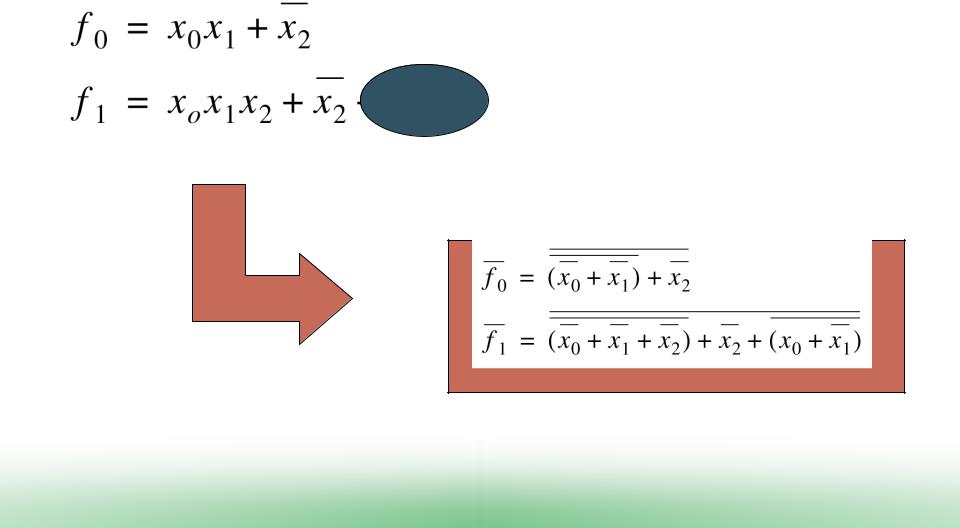

Двухуровневаякомбинационнаялогикагика

Любая логическая функция может быть представлена как сумма произведений (и реализована в базисе НЕ -ИЛИ)

minterm

minterm

обратный формат

(NOR-NOR) – м.б.

более эффективным

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |