Для магистратуры / Русские лекции по проектированию БИС / EDA_12_L-7

.pdf

Карты Карно: 4-х разрядное устройство для |

34 |

||||||||||

обнаружения простых чисел, пример минимизации: |

|

||||||||||

|

При заданной 4-х разрядной двоичной комбинации N=N3N2N1N0 на входе |

|

|||||||||

|

схема вырабатывает на выходе |

1, если N=1,2,3,5,7,11,13 и |

|

||||||||

|

|

|

|

|

|

|

|

0 – при остальных сигналах на входе |

|

||

|

№ |

N3 |

N2 |

N1 |

N0 |

F |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

1 |

Каноническая сумма (СДНФ): |

|

||||

|

|

|

|

|

|

|

|

||||

2 |

0 |

0 |

1 |

0 |

1 |

|

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

1 |

1 |

F=(~N3)(~N2)(~N1)N0+(~N3)(~N2)N1(~N0)+ |

|

||||

|

|

|

|

|

|

|

|

||||

0 |

0 |

1 |

0 |

0 |

0 |

|

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

1 |

1 |

+(~N3)(~N2)N1N0+(~N3)N2(~N1)N0+ |

|

||||

|

|

|

|

|

|

|

|

||||

6 |

0 |

1 |

1 |

0 |

0 |

|

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

+(~N3)N2N1N0+N3(~N2)N1N0+ N3N2(~N1)N0 |

|

|||

8 |

1 |

0 |

0 |

0 |

0 |

|

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

… |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

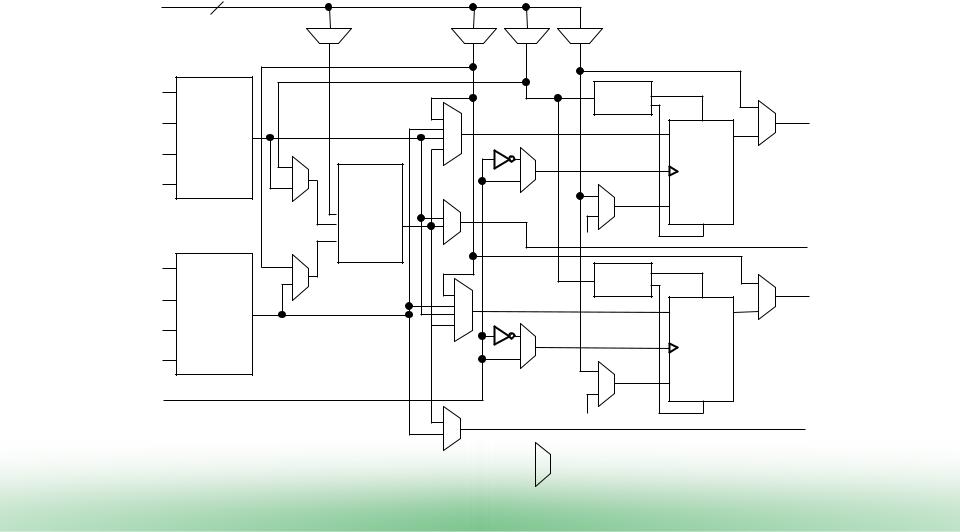

Логическая схема: |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

… |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

4НЕ + 4 (4И) + 7 ИЛИ (? ?) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

1 |

1 |

0 |

1 |

1 |

|

|

||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

… |

|

|

|

|

|

|

|

|

|

|

МГТУ МИРЭАДополнения. Центрк САПРпроектирования(ликбез по информатикеИС, УН)и2012МСг. доц. ПевцовСовременныеЕ.Ф. САПР

66

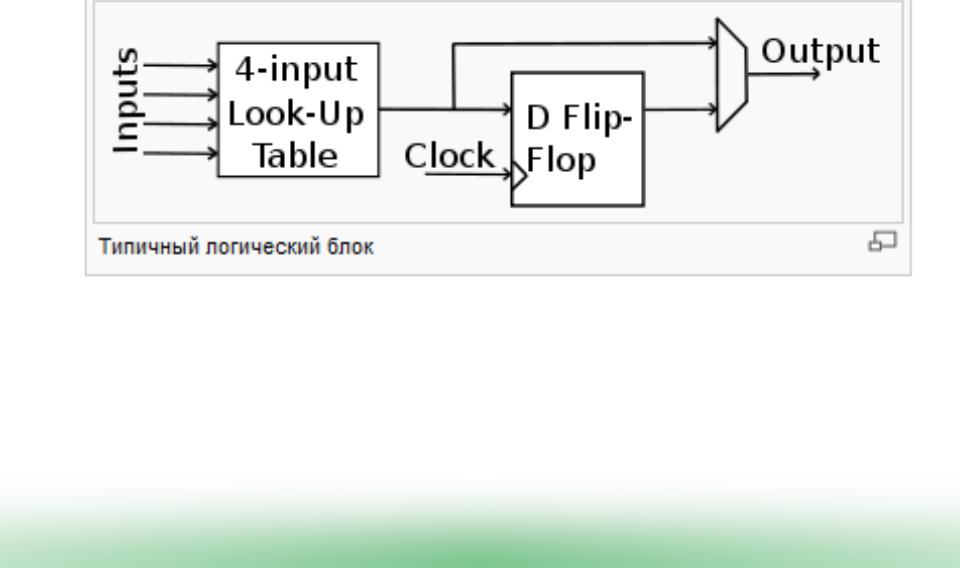

Логический блок (логический элемент, LE) классической ППВМ состоит из таблицы поиска на 4 входа и триггера:

Логический блок имеет таблицу поиска на 4 входа и вход синхронизации (clock). Выход блока только один, это может быть регистровая или нерегистровая выходная таблица поиска.

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

Таблица истинности – LUT

Триггер

Двухвходовой

мультиплексор

Выход (OUT LE)

Выход LUT Выход триггера

Коммутатор входов LE

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

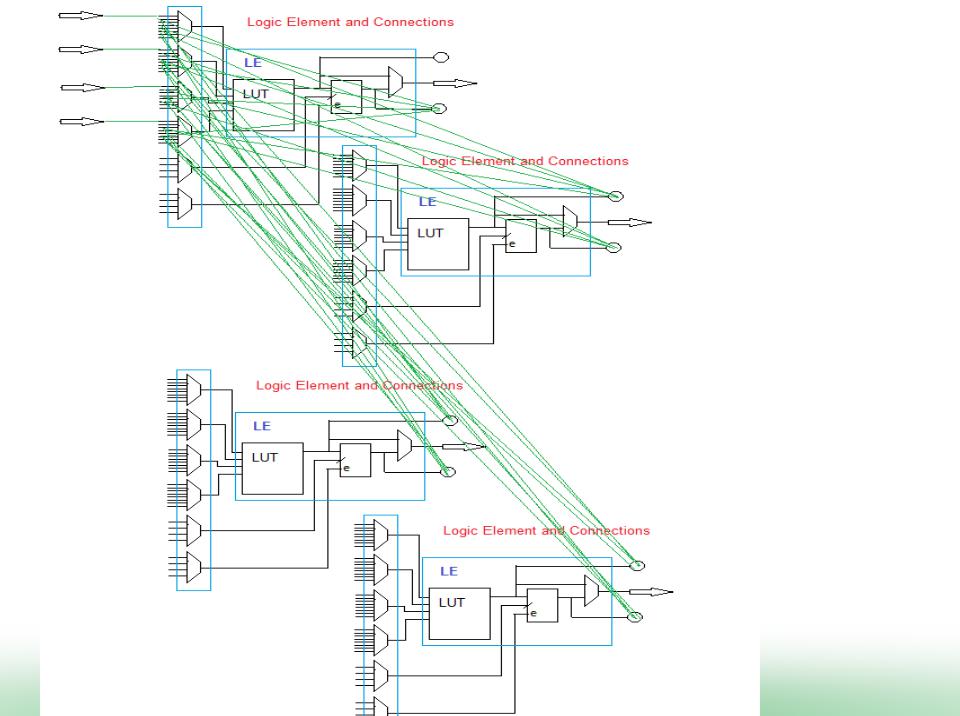

Каждый вход LUT имеет коммутатор с 8-ю входами, который позволяет подключить к нему:

-либо любой из выходов

любого триггера любого Логического Элемента,

-либо выход LUT любого

логического элемента (кроме выхода своего LUT)

-

- либо один из входов ПЛИС.

САПР

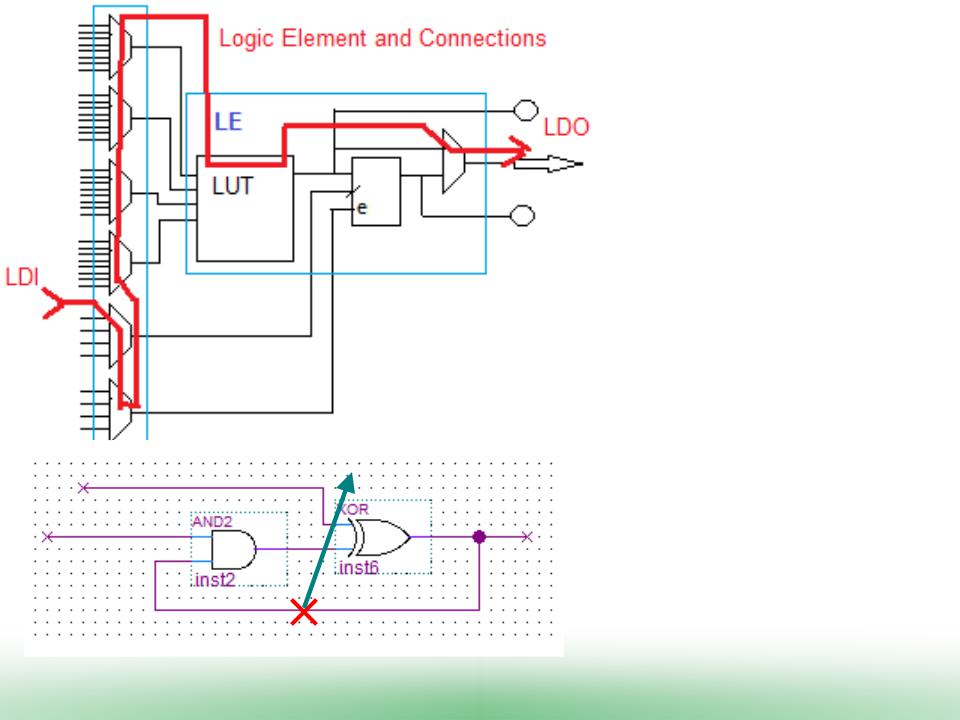

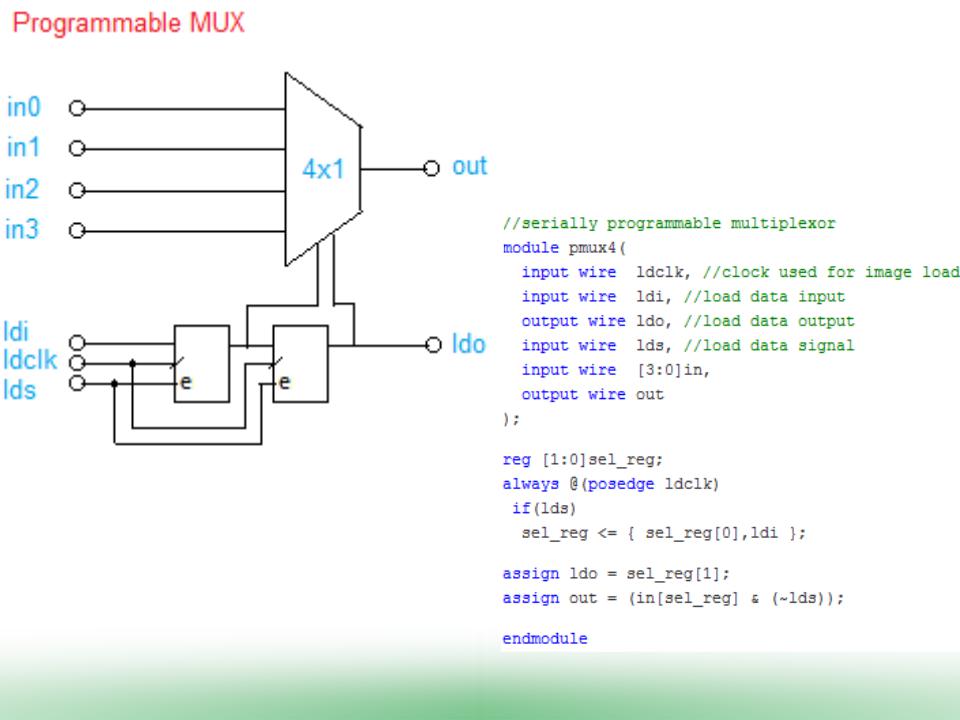

принудительное подавление выходных сигналов мультиплексоров в ноль во время активного сигнала lds

Как реализовать начальную загрузку таблицы LUT? Каждая LUT и каждый программируемый мультиплексор используют для загрузки (начальной инициализации) сигналы ldi, ldclk, lds и ldo.

Выход ldo одного модуля соединен со входом ldi следующего и так далее. Т.е. все компоненты ПЛИС объединены в один очень длинный последовательный регистр, содержащий образ пользовательского проекта – «прошивку».

Нужно на вход lds подать единицу, на вход ldi последовательно задвигать образ проекта синхронно с тактовой частотой ldclk. Образ проекта пройдет «насквозь» все модули и выйдет на выход ldo последнего модуля.

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

На входе расположен программируемый мультиплексор / коммутатор

(пример кода с 4-мя входами) :

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

Объединены две таблицы соответствий (на основе памяти) с 4-мя входами выходы к-рых |

||||||||||

подаются на таблицу соответствий с 3-мя входами. Кроме того, ячейка содержит два триггера, |

||||||||||

входами к-рых могут быть любые выходы таблицы соответствий F, G, H, атакже |

||||||||||

дополнительный внешний вход Din. Выходы триггеров снимаются с выходных контактов XQ и YQ. |

||||||||||

Имеются также 4-ре дополнительных входа, С1…С4, которые можно использовать как входы, |

||||||||||

сигналя установки/сброса или запуска синхронизатора триггеров. |

|

|

|

|

||||||

C ....C |

4 |

|

|

|

|

|

|

|

|

|

1 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

H1 |

|

D /H |

S/R/H EC |

|

|

|

|

|

|

|

|

|

in 2 |

0 |

|

|

|

|

|

G4 |

Logic |

|

|

|

S/R |

|

|

|

Bypass |

|

G3 |

|

|

Din |

control |

D SDQ |

YQ |

|||

|

function |

|

|

G’ |

|

|||||

|

|

|

F’ |

|

|

|||||

|

G2 |

of |

|

|

H’ |

|

|

|

|

|

|

G1…G4 |

|

|

|

|

|

|

|

|

|

|

G1 |

Logic |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

function |

G’ |

|

ECRD |

|

|||

|

|

|

of |

H’ |

H’ |

1 |

|

|

|

|

|

|

|

|

|

|

|

Y |

|||

|

|

|

F’,G’,H1 |

|

|

|

|

|||

|

F4 |

|

|

|

|

|

|

|||

|

|

|

S/R |

|

|

|

Bypass |

|||

|

|

|

|

|

|

|

|

|||

|

F |

Logic |

|

|

|

|

|

|

||

|

|

|

Din |

control |

|

SD |

|

XQ |

||

|

3 |

function |

|

|

G’ |

|

D |

Q |

|

|

|

F2 |

|

|

F’ |

|

|

|

|||

|

of |

|

|

H’ |

|

|

|

|

|

|

|

F1 |

F1…F4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

|

|

|

|

ECRD |

|

||

|

(Clock) |

|

|

H’ |

1 |

|

|

|

X |

|

|

|

|

|

|

F’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Xilinx 4000 Series |

|

|

|

Мультиплексоры управляются |

||||||

|

|

|

программой конфигурирования ПЛИС |

|||||||

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

|||||||||

БВВ :

Пример схемы конфигурируемого блока ввода-вывода в FPGA

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

67

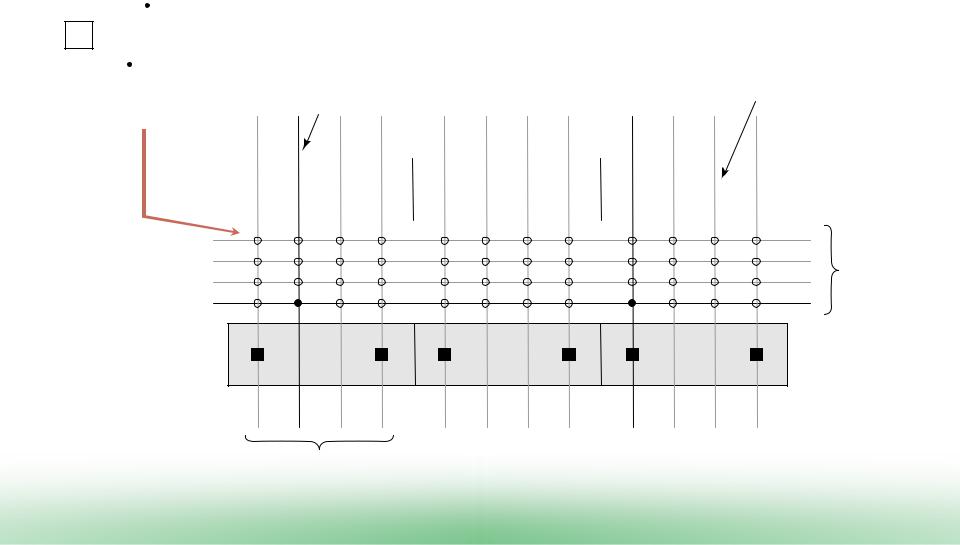

Программирование соединений: В месте пересечения вертикальных и горизонтальных каналов создаются переключательные блоки. Для каждого проводника, входящего в переключательный блок, существуют три программируемых переключателя, которые позволяют ему подключаться к трём другим проводникам в смежных сегментах канала (в узле – 5 переключателей).

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |

|

Разводка, программируемая как матрица соединений: Замыкаются |

68 |

|||||||||||||||||||||||

|

|

||||||||||||||||||||||||

|

накоротко точки пересечения некоторых вертикальных и горизонтальных |

|

|||||||||||||||||||||||

|

проводников. Ключом служит проходной транзистор. |

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Точка |

Как правило сетку делают неполной |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

M |

|

|

|

|

|

|

|

|

соединений |

(архитектура типа «сеть»). |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Программирование межсоединений |

|

Входной/выходной |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

контакт |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ячейка |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Горизонт. шины

Вертикальные шины

МГТУ МИРЭА. Центр проектирования ИС, УН и МС |

Современные САПР |