- •Контрольная работа

- •Выбор варианта задания

- •Методические указания к заданию 1

- •Задание 2

- •Методические указания к заданию 2

- •Решение

- •Задание 3

- •Код обмена информацией кои-7

- •Методические указания к заданию 3

- •Пример кодирования сообщения в кои-7

- •Задание 4

- •Методические указания к заданию 4

- •75 2

- •Задание 5

- •Выбор варианта задания

- •Методические указания к заданию 5

- •Задание 6

- •Методические указания к заданию 6

- •Решение

- •Экзаменационные вопросы

- •Литература

Задание 5

Вычислить для трех случаев физический адрес на 20-ти младших линиях шины адреса МПС на базе микропроцессора Ix86 в реальном режиме, если логический адрес в формате «сегмент: смещение» представлен в табл. 5. Номер варианта выбрать по последней цифре номера зачетной книжки.

Таблица 5

Выбор варианта задания

|

Вариант |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

0 |

|

1) |

3A48: 0100 |

2C09: 0070 |

45D7: 0005 |

A234: 0000 |

7890: 6000 |

0040: 07DF |

A050: 0587 |

0C58: 0450 |

B400: 67B6 |

9ABC: 59EB |

|

2) |

D2C7: 8E59 |

0204: E56A |

C55F: 92AD |

B2C7: 9F6B |

15F9: F35A |

0BCD: F123 |

4DE8: 6BC4 |

7B7E: 89BC |

8DEF: A6C9 |

4D7B: 78F7 |

|

3) |

0015: FB20 |

BC38: 5678 |

000C: 70B4 |

89E2: 6E58 |

D70B: 7CE2 |

E58C: 6F8A |

67FA: 4321 |

B3DA: 95F7 |

B2C7: 9876 |

DC67: 2479 |

Методические указания к заданию 5

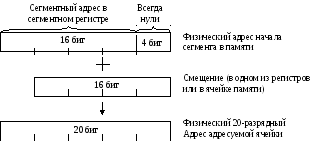

В реальном режиме микропроцессоров Ix86 используется сегментная адресация. Суть ее заключается в следующем. Физический 20-разрядный адрес любой ячейки памяти вычисляется процессором путем сложения 20-разрядного начального адреса сегмента памяти, в котором располагается эта ячейка, с 16-разрядным смещением к ней (в байтах) от начала сегмента (рис.2).

Рис. 2. Образование физического адреса из сегментного адреса и смещения

Начальный адрес сегмента без четырех младших бит, т. е. деленный на 16, хранится в одном из сегментных регистров. Эта величина называется сегментным адресом. Каждый раз при загрузке в сегментный регистр сегментного адреса процессор автоматически умножает его на 10h = 16 и полученный таким образом базовый адрес сегмента сохраняет в одном из своих внутренних регистров. При необходимости обратиться к той или иной ячейке памяти процессор прибавляет к этому базовому адресу смещение ячейки, в результате чего образуется физический адрес ячейки в памяти. Умножение 16-разрядного сегментного адреса - 64 Кбайт на 16 увеличивает диапазон адресуемых ячеек до величины 1 Мбайт.

Задание 6

Одна из основных функций средств отладки – сбор информации о поведении тестируемой системы и представление собранной информации в виде, удобном для того, кто ведет отладку: схемотехника, программиста, системотехника.

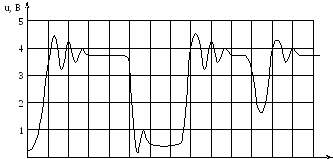

Данное задание моделирует процесс ввода информации из одной контролируемой точки МПС в логический анализатор в режиме анализа временных диаграмм. Обратите внимание, как зависит полученная информация от выбора уровня компарации и периода синхросигнала.

1. Определить значения сигналов на выходе компаратора уровней логического анализатора. Форма сигнала на входе логического анализатора показана на рис. 3, а.

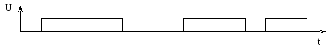

2. Определить данные, которые будут записаны в память логического анализатора.

а)

0 0,1 0,2 0,3 0,4 0,5 0,6 0,7 0,8 0,9 1,0 1,1 1,2 1,3 1,4 t, мкс

б)

Рис. 3. Сигнал на входе логического анализатора (а)

и сигнал на выходе компаратора уровней (б)

Период синхросигнала и уровень компарации выбрать в соответствии с номером зачетной книжки по табл. 6.

Таблица 6

Выбор условий компарации

|

Предпоследняя цифра книжки |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

Период синхросигнала, мкс |

0,025 |

0,05 |

0,1 |

0,15 |

0,025 |

0,05 |

0,1 |

0,15 |

0,025 |

0,05 |

|

Последняя цифра книжки |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

Уровень компарации, В |

1 |

2,5 |

0,3 |

0,8 |

1,5 |

2 |

3 |

3,4 |

3,9 |

4,1 |