___МЕТОДИЧКИ_2013 / Пособие по ОСМПС (pdf) / 12_N-проводные отладчики

.pdf12. НОВЫЕ МЕТОДЫ: N-ПРОВОДНЫЕ ОТЛАДЧИКИ

Одна из проблем, связанная с использованием новых эмуляторов, это компоновка целевого устройства. Микросхемы с двухрядным размещением выводов сейчас используются лишь в самых недорогих проектах. Наиболее распространенная ныне практика - поверхностный монтаж микросхем с множеством близко расположенных выводов, что требует применения сложных, дорогих и "капризных", с механической и электрической точки зрения, адаптеров.

В стремлении к стандартизации методов отладки и избавления от многочисленных дополнительных кабелей, изобретались различные схемные приспособления. Как правило, эти схемы подключаются к весьма небольшому числу выводов (три-пять)

процессора, установленного в стандартное гнездо. И хотя в большинстве случаев они способны отобразить происходящее внутри процессора, состязаться с полнофункциональным эмулятором в части полноты оперативной информации они не в состоянии. В некоторых случаях реализуемый такими схемами сервис крайне ограничен.

12.1. СИСТЕМА JTAG

Система JTAG это 5-проводная диагностическая система, являющаяся частью стандарта IEEE 1149. Она реализует метод периферийного сканирования, то есть получения последовательности состояний выводов исследуемого устройства. В системе есть порт TAP (Test Acces Port), посредством которого можно выполнять ограниченное число команд. Поскольку информация вводится в отлаживаемое устройство и выводится из него в последовательном виде, метод JTAG не может похвастаться оперативностью и служить заменой полнофункциональному эмулятору, так как не в состоянии отразить текущее состояние внутренних шин.

Вместе с тем JTAG широко используется для отладки реальных устройств, поскольку не требует никакой оперативной памяти и дополнительных портов. Тестируемая программа может быть той окончательной версией, которая будет поставляться. Другое достоинство JTAG заключается в том, что этот метод позволяет одновременно тестировать несколько устройств на плате, выступая в этом случае в роли псевдоэмулятора.

Учитывая то, что JATG сейчас является де-факто стандартным интерфейсом для отладки, разработчики новых стандартов стремились сделать их электрически совместимыми с существующим решением. В настоящее время предлагается две альтернативные реализации: так называемый улучшенный JTAG (EJTAG) от фирмы MIPS и интер-

фейс NEXUS.

12.2. ОТЛАДОЧНЫЙ ИНТЕРФЕЙС NEXUS

Стандарт IEEE-ISTO 5001-1999, или Nexus 5001, ранее называвшийся GEPDISC (Global Embedded Processor Debug Interface Consortium), был задуман как стандартный отладочный интерфейс для встроенных применений. По начальной спецификации он должен обеспечивать:

отладку в режиме реального времени; слежение в реальном времени за исполняемым кодом и данными; калибровку (изменение данных "на лету"); анализ логики исполнения; быструю отладку опытных образцов.

Почему назрела необходимость в разработке нового стандарта?

Отладочные средства, встроенные в процессоры, нужны уже сегодня (и тем более в будущем), поскольку без такой поддержки невозможно либо технически, либо экономически разрабатывать и применять традиционные средства отладки, учитывая все увеличивающиеся скорости работы микросхем. Вот некоторые основные причины:

хранение кода программы в памяти, расположенной в той же микросхеме, что и процессор, крайне затрудняет (или даже делает невозможным) применение традиционных внешних устройств, таких как логические анализаторы или эмуляторы для определения исполняемых инструкций, поскольку просто не существует доступа к шине снаружи;

очень высокие скорости работы микропроцессоров означают, что отладчики не в состоянии корректно устанавливать точки останова, поскольку временные интервалы слишком малы для обеспечения режима работы "остановка-перед-исполнением";

использование на кристаллах очередей команд, RISC-архитектур и кэш-памяти крайне затрудняет выявление выполняемых в данный момент инструкций;

растущая популярность систем-на-кристалле (SOC), многие из которых включают более одного процессора и ориентируются на решение конкретных задач, означает что, для того чтобы избежать переделки отладочных средств для каждого нового SOCкристалла, необходимо наличие встроенного единообразного отладочного интерфейса;

поскольку сроки разработки новых продуктов стремительно сокращаются, для выхода продукта на рынок в установленные сроки, необходимо наличие надежного и эффективного механизма отладки.

Перечислим основные свойства интерфейса NEXUS.

Управление процессором в режиме исполнения. Это базовое свойство всех от-

ладочных средств является стандартом для всех внутрисхемных отладчиков. Оно позволяет запускать и останавливать процессор, модифицировать регистры и обеспечивать пошаговое исполнение инструкций.

Интерфейс NEXUS обеспечивает доступ к памяти во время работы микропроцессора ("на лету"). Это свойство позволяет отладочным средствам читать и модифицировать содержимое ячеек памяти во время работы процессора без влияния на исполняемые инструкции. Доступ "на лету" очень привлекательное средство для отладки систем реального времени, где остановка системы при проведении тестов просто невозможна.

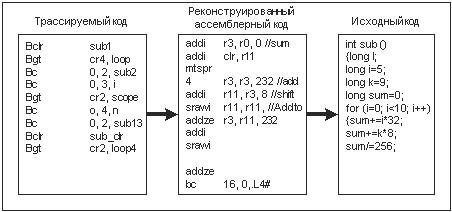

Точки останова. В интерфейсе NEXUS используется техника "Переход-Запись" (Branch-trace) для компрессирования информации, необходимой для отслеживания процесса исполнения программы. Адрес исполняемого кода выдается в интерфейс NEXUS только для команд перехода или исключений, отладочные средства потом интерполируют (восстанавливают) ход исполнения программы путем добавления последовательных (не переходы) инструкций на основании образа программы на диске. Это позволяет полностью восстановить ход исполнения программы. Пример приведен на рис. 3:

Рис. 3. Стандартизация отладочной спецификации Nexus 5001 упрощает трассируемость кода программы, благодаря передаче сообщений

оветвлениях и ассемблированию кода во время его исполнения

вреальном времени на встроенном процессоре целевого устройства.

Трассировка данных. Это свойство позволяет записывать в реальном времени адреса, по которым производилось обращение к данным. Регистрация может производиться по специфическим адресам памяти (начальный и конечный адрес региона) и по типу доступа (запись чтение).

Контроль владельца. Благодаря этому свойству операционные системы реального времени (ОСРВ) могут идентифицировать исполняемый процесс или поток. ОСВР просто производит запись в специально отведенный в стандарте IEEE-ISTO 5001 -1999 регистр, вызывая тем самым выдачу сообщения "Ownership Trace" в NEXUS-порт. Сообщение содержит параметр, который идентифицирует отлаживаемый процесс или поток.

Замена портов ввода-вывода или области памяти. Это свойство позволяет ото-

бражать доступ к внутренней памяти или портам через дополнительный NEXUS-порт. Например, оно может использоваться для изменения ПЗУ, когда вместо чтения ПЗУ на кристалле, средство отладки просто обращается к нему через дополнительный NEXUSпорт. Замена портов, например, полезна, когда относительно медленные контакты имеют дополнительную функцию. Это позволяет отладочному средству эмулировать их основную функцию.

Сбор данных. Это свойство было добавлено для поддержки быстрой отладки систем, оно позволяет осуществлять быстрый обмен произвольными массивами данных через дополнительный порт. Этот обмен использует более эффективный протокол, чем при трассировке данных.

Программный интерфейс. Это низкоуровневый интерфейс программирования (API) который скрывает специфику целевых систем, такую как механизм связи с хостЭВМ, и специфические регистры процессора. Такой интерфейс разрабатывается совместно производителем средств отладки и поставщиком микросхем.

Классы IEEE-ISTO 5001 –1999.

Отладочный интерфейс NEXUS является масштабируемым стандартом; в настоящее время существует 4 класса, определяющих функциональность, от базового Класса 1 (JTAG) до Класса 4.

Класс 1 поддерживает управление процессором (останов, запуск, запись-чтение памяти при остановленном процессоре, чтение или запись в регистры), используя интерфейс JTAG. Режим обмена - полудуплекс, полоса пропускания ограничена. Трассировка не поддерживается.

В классе 2 добавляются контроль владельца, трассировка программного кода и возможность использования дополнительного порта для ввода-вывода.

Класс 3 добавляет возможность трассировки записи данных и чтения/записи памяти "на лету", без остановки процессора. Трассировка чтения/записи данных, использование дополнительного порта для быстрого обмена данными и эмуляции шин данных/адреса являются опциональными.

Класс 4 добавляет эмуляцию памяти через дополнительный NEXUS-порт и возможность старта трассировки с помощью точки останова. Запуск эмуляции памяти по точке останова является опциональным свойством для Класса 4.

Примерами микропроцессоров, уже поддерживающих данный стандарт, являются процессоры M-CORE (M340) и MPC565 от компании Моторола.

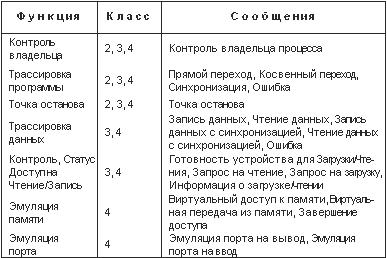

Для поддержки функциональности, определенной в различных классах, используется концепция общедоступных сообщений (Public Messages). Они представляют собой набор пакетов для передачи информации, ассоциированной с каждой особенностью отладки, представленной в стандарте. Общедоступное сообщение (Public Message) включает в себя передачу классификатора или TCODE, идентификационного номера процессора и ассоциированных данных. Основное требование к реализации общедоступных сообщений их эффективность, вследствие этого пакеты могут иметь различную длину в зависимости от TCODE. Каждая конкретная функция NEXUS может требовать генерации нескольких сообщений для передачи необходимой информации. В таблице 1 приведены функции в соответствии с классами и типами используемых сообщений.

Таблица 1. Функции в соответствии с классами и типами сообщений

12.3. ИНТЕРФЕЙС EJTAG

Консорциум поставщиков средств отладки для RISC-процессоров MIPS (консорциум MIPS RISC) совместно с компанией MIPS Technologies Inc. разработали альтернативную реализацию интерфейса отладки на кристалле, называемую EJTAG (Enhanced JTAG). В настоящее время она воплощена в нескольких процессорах, включая

TinyRISC от LSI Logic, семейство TX49 от Toshiba и 32-разрядный процессор JADE от

MIPS Technologies, Inc. Для упрощения физической реализации, снижения стоимости и обеспечения совместимости в EJTAG используется интерфейс, аналогичный JTAG. Дополнительная логика, размещенная на кристалле, обеспечивает управление, установку точек останова в данных и коде, трассировку счетчика инструкций в реальном времени.

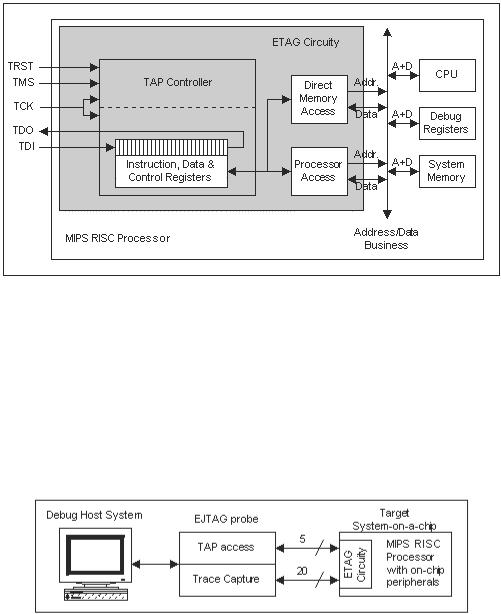

Рис. 4. Внутренняя архитектура отладочного средства EJTAG

Для обмена данными со средствами отладки в EJTAG используются те же 5 контактов IEEE 1149.1. На рис.4 изображена внутренняя архитектура EJTAG:

Передача данных через TAP-порт происходит в последовательном виде с частотой до 40 Мгц и выше. Контроль работы EJTAG осуществляется с помощью набора внутренних 32-разрядных регистров, которые используются для определения ресурсов, необходимых для отладки и сбора статусной информации.

Работа EJTAG контролируется с помощью EJTAG-адаптера, служащего интерфейсом между хост-ЭВМ и целевым устройством, как показано на рис.5:

Рис. 5. Схема отладки микроконтроллера с помощью технологии EJTAG

Возможности отладки ЦП

Средства отладки EJTAG требуют высокой степени интеграции с процессором. Для обеспечения процесса отладки блок центрального процессора (ЦП) должен поддерживать специальный режим отладки, регистры и инструкции. Одна из наиболее важных особенностей наличие специального отладочного исключения, приоритет которого выше приоритетов всех других исключений. Оно возникает в том случае, когда установлена программная точка останова, выдана инструкция пошагового исполнения или зарегистрировано отладочное событие JtagBrk в EJTAG. Инструкция программной точки останова (SDBBP) определена в наборе команд архитектуры MIPS. Для простых точек останова отладчик может подменять инструкции приложения на программные точки останова для генерации отладочного исключения.

Когда исключение возникает, ЦП переходит в специальный отладочный режим, в котором нет ограничений на доступ к сопроцессорам и памяти, и обычные исключения, такие как ошибка адреса или прерывание, замаскированы.

Обработчик исключения обеспечивается отладочной системой и может запускаться через EJTAG-порт, используя интерфейс доступа к процессору, или включается в код приложения по выбору разработчика.

Специальные отладочные регистры DEBUG, DEPC и DESAVE содержат отладочную информацию. Регистр DEBUG показывает источник отладочного исключения и других стандартных исключений, которые могут возникать одновременно. Он также используется для установки пошагового режима. Регистр DEPC (Debug Exception Program Counter) содержит адрес точки возникновения исключения. Он используется для возврата в исполняемую программу после завершения режима отладки. Регистр

DESAVE (Debug Exception Save Register) может хранить дополнительную информа-

цию, освобождая 32-разрядные регистры процессора общего назначения от задачи сохранения обработчика исключения. В этом случае обработчик исключения не затрагивает содержимое регистров процессора общего назначения.

В спецификации EJTAG существуют несколько типов аппаратных точек останова. Они останавливают нормальную работу ЦП и переводят его в отладочный режим. Останов возникает в том случае, когда на шинах адреса, данных или управления ЦП происходят определенные операции. Отладочное исключение возникает до выполнения операции, сохраняя тем самым содержимое регистров или памяти. Аппаратные точки останова, в отличие от программных, могут ассоциироваться с определенным адресом на шине, так что могут использоваться для доступа к любой области памяти.

Всего определено три типа аппаратных точек останова: по команде, по данным и по шине процессора.

Одной из самых больших проблем в отладке с использованием высокопроизводительных ЦП, снабжённых кэш-памятью, является доступ в реальном времени к счетчику команд. Режим EJTAG RPCT (Real Time Counter Trace) позволяет отслеживать счетчик в реальном времени, но, тем не менее, требует дополнительных контактов в интерфейсе. Число контактов зависит от скорости процессора. В зависимости от числа контактов и тактовой частоты для вывода данных, процессор может работать на полной скорости, либо приостанавливаться для ожидания завершения передачи. Например, в ядрах JADE 32 от MIPS Technologies процессор может использовать от 4 до 11 контактов для передачи данных в реальном времени. При использовании 4 контактов до останова процессора может быть зарегистрировано около 40% данных, при использовании 11 контактов, достигается 100-процентная передача данных без остановки процессора.

Состояние счетчика передается лишь в некоторых случаях. Пока происходит последовательное исполнение команд, нет нужды в передаче содержимого счетчика. Только когда происходит переход, ветвление или исключение, новое значение должно быть зафиксировано. В случае исключения передается также информация о его типе. Такой подход позволяет значительно сокращать количество интерфейсных контактов.

12.4. ДРУГИЕ ОТЛАДОЧНЫЕ СИСТЕМЫ

Система BDM (Motorola)

Отладочное средство BDM (Background Debug Mode отладка в фоновом режиме) это 10-проводная система отладки, используемая в основном компанией Motorola. Система позволяет считывать и записывать данные в отдельные ячейки памяти и регистры, читать и записывать данные в непрерывные блоки памяти, а также останавливать и возобновлять исполнение программы с указанного адреса (который может быть исход-

ным или модифицированным значением регистра счетчика команд). При своей активизации BDM полностью останавливает текущую работу микропроцессора. Заменить внутрисхемный эмулятор метод BDM не может, хотя всё же и дает разработчику динамически загружаемый ПЗУ-монитор (правда, с базовыми функциями). Основным достоинством этого метода является то, что отладка может осуществляться из программ, работающих на хост-ПК.

Хотя система BDM и не всесильна, её можно считать бесплатной в том смысле, что она вообще не требует никаких ресурсов и во всех случаях присутствует на кристалле. Современные BDM-адаптеры и программное обеспечение хост-ПК относительно недороги.

AMDeBug

Недавно компания AMD объявила о создании специальной, встроенной в кристалл диагностической системы для своих процессоров семейства Е86, в состав которой входит буфер трассировки и которая обеспечивает работу с буфером через последовательный (разъем JTAG) или параллельный порт. Вариант с параллельным портом требует применения диагностической версии микропроцессора.

Концепция эмуляции Enhanced Hooks

Некоторые производители микросхем воспользовались концепцией эмуляции

Enhanced Hooks, разработанной компанией Metalink Corporation. В частности, Siemens

применяет ее для контроля исполнения машинных команд и сбора сведений о внутренних операциях в микроконтроллерных устройствах семейства С500 и С166.

Концепцией предусмотрена также возможность использования программ, записанных в ПЗУ на кристалле. Внутри каждого производимого интегрального устройства есть встроенные логические схемы, обеспечивающие поддержку концепции Enhanced Hooks, вследствие чего в процессе эмуляции не нужны дорогостоящие диагностические варианты кристаллов. Кроме того, подобное решение гарантирует полную идентичность эмулируемой и производимой микросхем. Технология Enhanced Hooks, требующая наличия в С500 встроенной логики, обеспечивает работу этого процессора вместе с интегральной схемой Enhanced Hooks аналогично работе одной диагностической микросхемы. Благодаря этому упрощается конструкция и снижается стоимость всей системы эмуляции.

Системы ICE-Connect

Для отладки устройств типа 8051 и С166, которые не являются однокристальными и в которых порты 0 и 2 используются в качестве внешней шины, могут применяться системы ICE-Connect. Особенно они полезны для эмуляции систем с высокой степенью интеграции, где необходимо протестировать покрытие кода в окончательной версии программы и с окончательным составом технических средств.

Эмулятор подключается к отлаживаемой системе посредством 30 - или 56 - контактного переходника (в зависимости от разрядности восьмиили 16-разрядная система), однако вместо дорогостоящей диагностической модификации процессора используется его реальный рабочий вариант. Из дополнительного оборудования для целевой платы нужен лишь переходник ICE-Connect, который экономичен даже в серийном производстве плат. Этот недорогой разъем может быть установлен на любой плате, благодаря чему новые программы могут тестироваться на реальном оборудовании с применением тестов анализа использования кода и расчета времени исполнения, что делает системы ICE-Connect почти обязательными для отладки устройств высокой степени интеграции.

12.5. ВСТРОЕННЫЕ В КРИСТАЛЛ СРЕДСТВА ОТЛАДКИ

Устройства Tricore компании Siemens оснащены дополнительными отладочными средствами. Подключиться к ним можно через интерфейс JTAG по обычному соединительному кабелю. В архитектуре Tricore реализовано два уровня поддержки внутрикристальных средств отладки OCDS (On-Chip Debug Support), обеспечивающих реализацию чрезвычайно мощных инструментальных средств. Оба уровня отличаются гораздо более широкими возможностями, чем может предложить обычный JTAG-коннектор. Интегрированные схемы отладки не требуют выделения никаких ресурсов целевой системы (например, коммуникационных интерфейсов или памяти), а ошибки в прикладной программе на работу управляющего монитора никакого влияния не оказывают.

OCDS-средства уровня 1

При обнаружении ошибки программа может быть остановлена, хотя возможна всего лишь выдача соответствующих сигналов внешнему тестовому оборудованию с продолжением работы программы. Кроме того, присвоив отладочному прерыванию определенный уровень приоритета, можно организовывать постоянную обработку более приоритетных прерываний в критичных ко времени программных секциях, пока приостановлено исполнение отлаживаемых кодов более низкого приоритета. Другое достоинство OCDS-средств возможность операций чтения/записи по внутренним шинам Tricore с обращением в процессе исполнения программы к любому допустимому адресу (включая внутренние регистры) с крайне незначительным ухудшением оперативности. Таким образом, возможен доступ к любым переменным и параметрам программы "на лету".

OCDS-средства уровня 2

Этот уровень отличается дополнительной поддержкой в виде специализированной эмулирующей микросхемы, снабженной добавочными контактами, что значительно облегчает трассировку исполнения программы и поиск трудно выявляемых ошибок. Отладка на этом уровне требует прямого соединения с целевым контроллером и подключения дополнительного оборудования для регистрации сведений о ходе исполнения программы.

Основная проблема, связанная с описанными N-проводными системами, - их ориентация на микросхемы определенной архитектуры или определенного поставщика. Вместе с тем ориентация на разные архитектуры характерна и для эмуляторов, симуляторов и ПЗУ-мониторов, и большим недостатком обычно не выглядит. Да и вряд ли можно серьезно предполагать, что кто-нибудь будет пользоваться для отладки систем х86 средствами, рассчитанными на архитектуру 68К. Как правило, разработчики специализируются на одном-двух типах микропроцессорных устройств, и желание приобрести универсальный ВСЭ для всех типов архитектур так и останется розовой мечтой (по крайней мере, в обозримом будущем).

Заключение

N-проводные отладочные системы, в частности, система JTAG, – это мощные инструментальные средства для проектирования, предназначенные для использования функций встроенных в кристалл систем отладки. Управление отладочной системой осуществляет специальная программа, устанавливаемая на главном компьютере. Например, возможностями отладки AVR микроконтроллеров семейства ATMEGA с помощью интерфейса JTAG обладает интегрированная среда разработки AVR Studio, начиная с версии 4. Аналогичные возможности имеет IDE MPLAB фирмы Microchip.

Внутрисхемный эмулятор JTAG AVR представляет сравнительно простое устройство на базе микроконтроллера ATMEGA16, которое включается между ПК и целевой микропроцессорной системой. ВСЭ JTAG и пользовательский интерфейс AVR Studio

дают пользователю полное управление всеми ресурсами микроконтроллера, тем самым сокращая цикл проектирования за счет более простой отладки. ВСЭ JTAG выполняет реально-временную эмуляцию микроконтроллера будучи запущенным непосредственно на плате целевой системы. Он обеспечивает возможность эмуляции при более выгодной стоимости по сравнению с традиционными внутрисхемными эмуляторами.

ВСЭ JTAG автоматически обновляется при инсталляции новых версий AVR Studio для поддержки новых устройств с поддержкой JTAG интерфейса. Все ресурсы микроконтроллера могут быть отображены на экране: флэш-память, ЭППЗУ, статическое ОЗУ, регистры, программный счетчик, биты защиты и конфигурации, а также все модули ввода-вывода. ВСЭ JTAG также предлагает расширенную поддержку встроенной эмуляции для выполнения условий прерывания, в т.ч. прерывание по изменению потока памяти программ, прерывания по одиночному адресу или диапазону адресов памяти программ и прерывания по одиночному адресу или диапазону адресов памяти данных.

Вопросы для самоконтроля

1.Какие проблемы возникают при использовании традиционных ВСЭ?

2.Что представляет собой система JTAG? Приведите примеры ее использования.

3.Опишите возможности отладочного интерфейса NEXUS.

4.Охарактеризуйте параметры и возможности интерфейса EJTAG. Как подключается целевая система при отладке?

5.Какие проблемы возникают при использовании N – проводных отладчиков?

6.Расскажите, какие еще существуют отладочные системы.