- •Нижегородский государственный университет им. Н.И.Лобачевского

- •Содержание

- •Введение

- •Несколько вопросов

- •Сопроцессор Intel Xeon Phi…

- •Сопроцессор Intel Xeon Phi…

- •Сопроцессор Intel Xeon Phi

- •Intel Xeon Phi в суперкомпьютерах

- •Развитие архитектуры Intel Xeon Phi

- •Введение в архитектуру Intel Xeon Phi

- •Архитектура Intel Xeon Phi

- •Исполнительное ядро Intel Xeon Phi

- •Конвейер ядра Intel Xeon Phi…

- •Конвейер ядра Intel Xeon Phi…

- •Теоретическая производительность

- •Векторные операции

- •Векторные операции…

- •Векторные вычисления

- •Автовекторизация

- •Иерархия памяти Intel Xeon Phi

- •Иерархия памяти Intel Xeon Phi…

- •Иерархия памяти Intel Xeon Phi…

- •Иерархия памяти Intel Xeon Phi…

- •Иерархия памяти Intel Xeon Phi

- •Иерархия памяти Intel Xeon Phi

- •Программное обеспечение сопроцессора Intel Xeon Phi

- •Программное обеспечение сопроцессора Intel Xeon Phi

- •Операционная система сопроцессора Intel

- •Операционная система сопроцессора Intel

- •Модели использования сопроцессора Intel Xeon Phi

- •Режимы и модели использования

- •Исполнение в режиме Offload на одном

- •Режим выполнения Offload

- •Режим MPI

- •Исполнение в режиме MPI на одном узле

- •Режимы и модели использования

- •Модель симметричного выполнения

- •Модель использования только

- •Инструменты разработчика

- •Инструменты разработчика

- •Инструменты разработчика

- •Итоги

- •Требования к приложению, портируемому

- •Противопоказания

- •Замечания для повышения

- •Литература

Режимы и модели использования

сопроцессора Intel Xeon Phi…

Режим Offload

– Сопроцессор Xeon Phi или основной процессор используется в качестве ускорителя вычислений

Режим MPI

– Сопроцессор Xeon Phi и основной процессор исполняют равноправные MPI-процессы

MIC Offload |

Host Offload |

– MPI-процессы |

– MPI-процессы |

выполняются только |

выполняются только |

на основных ЦП |

на сопроцессорах |

– Сопроцессоры |

Xeon Phi |

Xeon Phi |

– Основные ЦП |

используются в |

используются в |

качестве |

качестве |

ускорителей |

ускорителей |

|

Не поддерживается |

Co-processor-only

–MPI-процессы выполняются только на сопроцессорах Xeon Phi

–MPI-пересылки - между сопроцессо- рами Xeon Phi через основные ЦП

–Поддерживается

многопоточность

Symmetric

–MPI-процессы выполняются на основных ЦП и сопро- цессорах Xeon Phi

–MPI-пересылки - между основными ЦП и сопроцессорами Xeon Phi

–Поддерживается

многопоточность

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

31 |

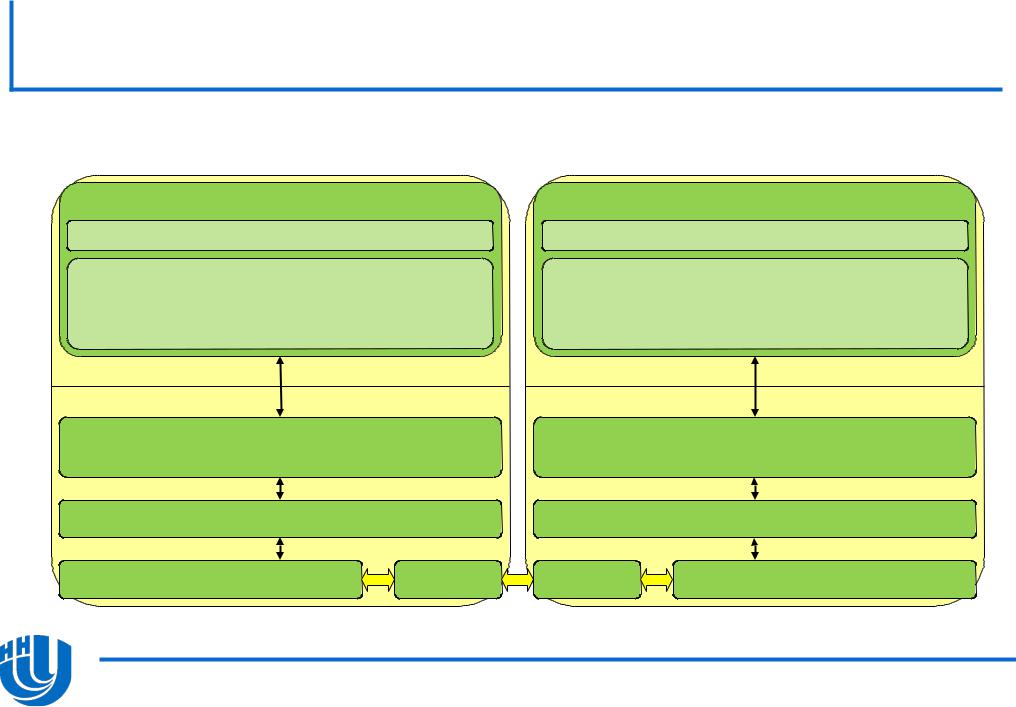

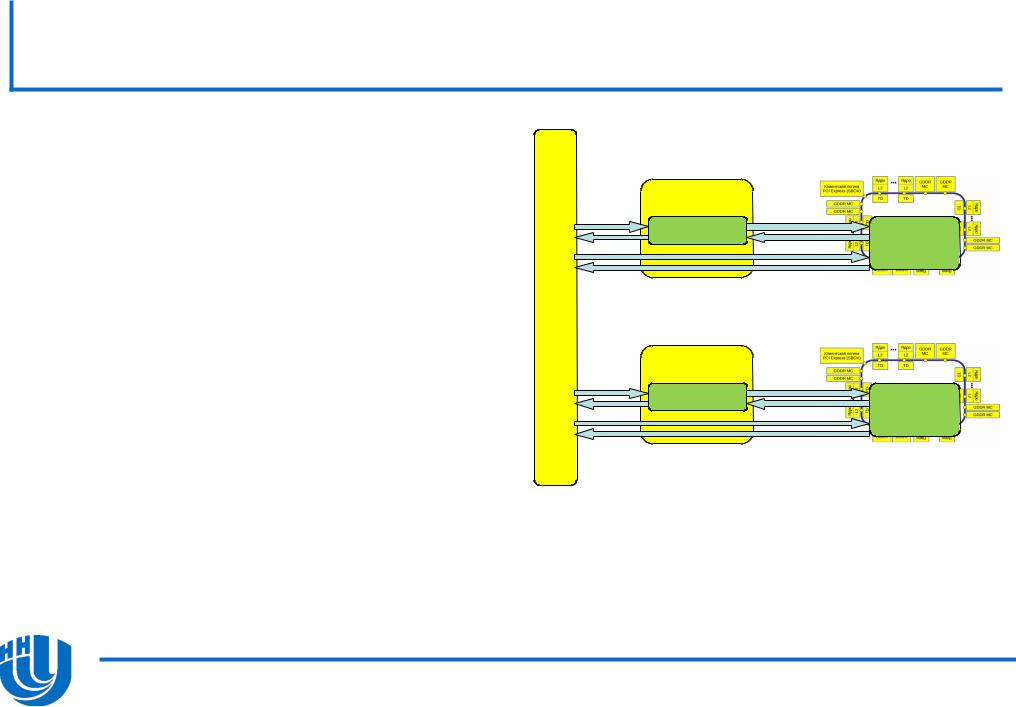

Исполнение в режиме Offload на одном

узле

Центральный процессор

Offload-приложение на стороне хоста Пользовательский код

Библиотека поддержки offload, драйвер пользовательского уровня, библиотеки (ОС или сторонние)

Уровень пользователя

Уровень ядра

Драйверы, библиотеки и утилиты поддержки Intel Xeon Phi

ОС Linux/Windows

Центральный процессор |

PCIe |

Сопроцессор Intel Xeon Phi

Offload-приложение на Xeon Phi Пользовательский код

Библиотека поддержки offload, библиотеки (ОС или сторонние)

Уровень пользователя

Уровень ядра

Драйверы, библиотеки и утилиты поддержки Intel Xeon Phi

ОС Linux

PCIe |

Сопроцессор Xeon Phi |

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

32 |

Режим выполнения Offload

MPI-процессы выполняются на процессорах базовой системы

Для использования вычислительных возможностей Xeon Phi используется

выгрузка |

и |

выполнение |

функций |

на сопроцессоре

–вызов функций MPI в выгруженном коде не поддерживается

Сеть передачи данных

MPI |

ЦП |

offload |

|

||

|

Данные |

|

MPI ЦП offload

Данные

MIC

MIC

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

33 |

Режим MPI

В режиме MPI базовая система и каждый сопроцессор Intel Xeon Phi рассматриваются как отдельные равноправные узлы, и процессы MPI могут выполняться на процессорах Xeon базовых систем и сопроцессорах Xeon Phi в произвольных сочетаниях

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

34 |

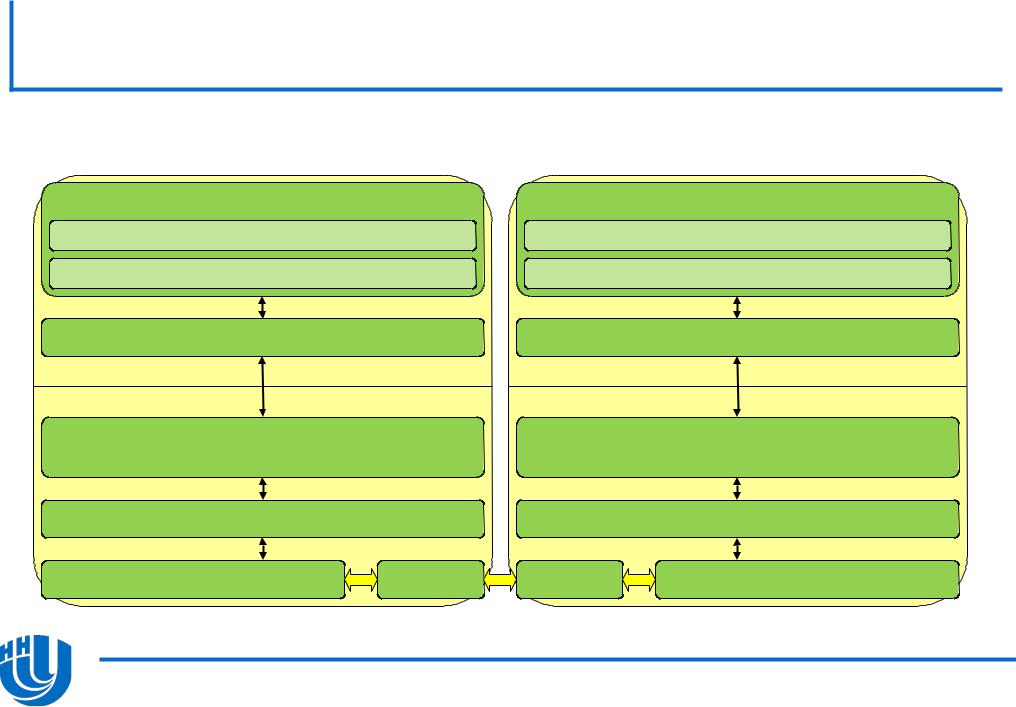

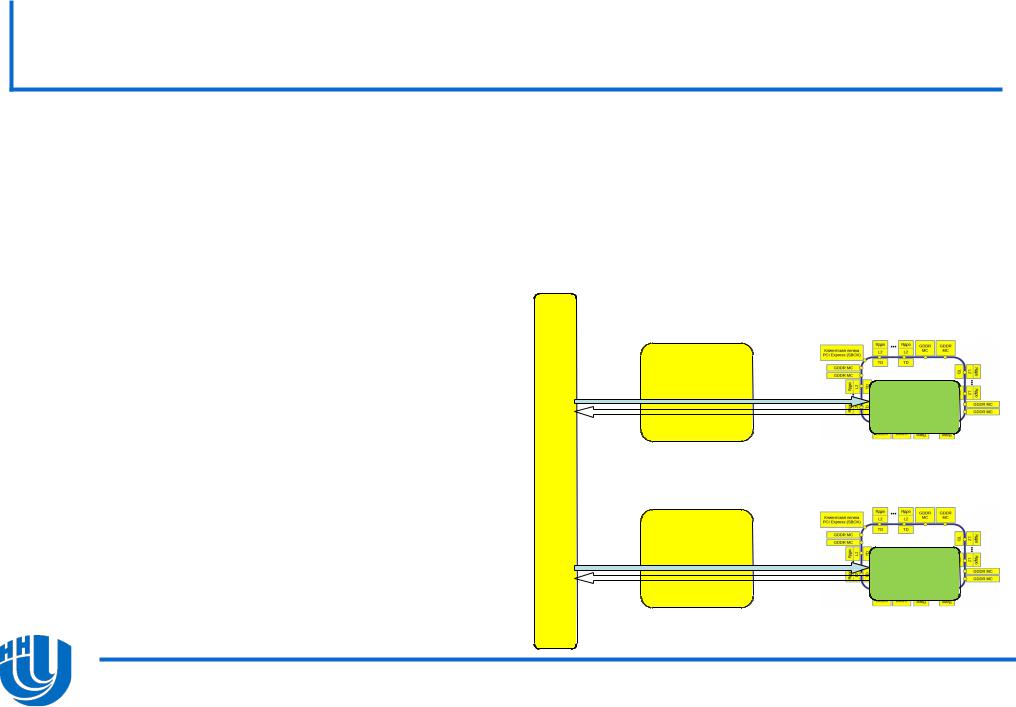

Исполнение в режиме MPI на одном узле

Центральный процессор |

|

Сопроцессор Intel Xeon Phi |

|

MPI-приложение на основном ЦП |

|

MPI-приложение на Xeon Phi |

|

Пользовательский код |

|

|

Пользовательский код |

Библиотеки (ОС или сторонние) |

Библиотеки (ОС или сторонние) |

||

ssh-сервер |

|

|

ssh-сервер |

Уровень пользователя |

|

Уровень пользователя |

|

Уровень ядра |

|

Уровень ядра |

|

Драйверы, библиотеки и утилиты |

Драйверы, библиотеки и утилиты |

||

поддержки Intel Xeon Phi |

|

|

поддержки Intel Xeon Phi |

ОС Linux/Windows |

|

|

ОС Linux |

Центральный процессор |

PCIe |

PCIe |

Сопроцессор Xeon Phi |

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

35 |

Режимы и модели использования

сопроцессора Intel Xeon Phi…

Три основные модели выполнения в режиме MPI

–Модель симметричного выполнения (Symmetric model)

•MPI-процессы выполняются как на процессорах базовой системы, так и на сопроцессорах

–Модель использования только сопроцессоров (Coprocessor-only model)

•Все MPI-процессы выполняются на сопроцессорах

–Модель использования только процессоров базовой системы (Host-only model)

•MPI-процессы выполняются на процессорах базовой системы, сопроцессоры не используются

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

36 |

Модель симметричного выполнения

MPI-процессы выполняются как на процессорах базовой системы, так и на данных сопроцессорах

Передача сообщений между процессорами базовой системы, в пределах передачи сопроцессора и между сопроцессором и процессорами базовой Сеть системы может выполняться через механизмы разделяемой памяти или протокола tcp

–по умолчанию tcp

–I_MPI_SSHM_SCIF= {enable|yes|on|1}

Данные |

MPI |

MIC |

MPI ЦП |

|

|

|

|

Данные |

|

MPI |

|

Данные |

MPI |

MIC |

MPI ЦП |

|

|

|

|

Данные |

|

MPI |

|

mpiexec.hydra –host $(hostname) -n 4 –env OMP_NUM_THREADS 4 ./test.exe.host -host mic0 –n 2 –env OMP_NUM_THREADS 16 –wdir /tmp /tmp/test.exe.mic

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

37 |

Модель использования только

сопроцессоров

Native model для Xeon Phi

Приложение, библиотека MPI и другие необходимые библиотеки загружаются на сопроцессор для выполнения

Запуск приложения может быть произведен как из базовой ОС, так и из ОС сопроцессора

Сеть передачи данных

ЦП MIC

Данные MPI

Данные MPI

ЦП MIC

Данные MPI

Данные MPI

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

38 |

Инструменты разработчика

Средства разработки:

–Intel Parallel Studio XE 2015

–Intel Cluster Studio XE 2015

–Intel SDK for OpenCL Applications / Intel INDE

–gcc

–…

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

39 |

Инструменты разработчика

Библиотеки:

–Intel Math Kernel Library (Intel MKL)

–Intel Threading Building Blocks (Intel TBB)

–Intel Integrated Performance Primitive (Intel IPP)

–Intel MPI for Linux

–MPICH2

–Boost

–…

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

40 |