- •Нижегородский государственный университет им. Н.И.Лобачевского

- •Содержание

- •Введение

- •Несколько вопросов

- •Сопроцессор Intel Xeon Phi…

- •Сопроцессор Intel Xeon Phi…

- •Сопроцессор Intel Xeon Phi

- •Intel Xeon Phi в суперкомпьютерах

- •Развитие архитектуры Intel Xeon Phi

- •Введение в архитектуру Intel Xeon Phi

- •Архитектура Intel Xeon Phi

- •Исполнительное ядро Intel Xeon Phi

- •Конвейер ядра Intel Xeon Phi…

- •Конвейер ядра Intel Xeon Phi…

- •Теоретическая производительность

- •Векторные операции

- •Векторные операции…

- •Векторные вычисления

- •Автовекторизация

- •Иерархия памяти Intel Xeon Phi

- •Иерархия памяти Intel Xeon Phi…

- •Иерархия памяти Intel Xeon Phi…

- •Иерархия памяти Intel Xeon Phi…

- •Иерархия памяти Intel Xeon Phi

- •Иерархия памяти Intel Xeon Phi

- •Программное обеспечение сопроцессора Intel Xeon Phi

- •Программное обеспечение сопроцессора Intel Xeon Phi

- •Операционная система сопроцессора Intel

- •Операционная система сопроцессора Intel

- •Модели использования сопроцессора Intel Xeon Phi

- •Режимы и модели использования

- •Исполнение в режиме Offload на одном

- •Режим выполнения Offload

- •Режим MPI

- •Исполнение в режиме MPI на одном узле

- •Режимы и модели использования

- •Модель симметричного выполнения

- •Модель использования только

- •Инструменты разработчика

- •Инструменты разработчика

- •Инструменты разработчика

- •Итоги

- •Требования к приложению, портируемому

- •Противопоказания

- •Замечания для повышения

- •Литература

Иерархия памяти Intel Xeon Phi…

Все ядра совместно используют оперативную память сопроцессора

Каждое ядро сопроцессора Intel Xeon Phi имеет собственные кеши L1 и L2

Кеши L1 и L2 являются инклюзивными

–все данные, хранящиеся в кэше L1, хранятся также в кэше L2

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

21 |

Иерархия памяти Intel Xeon Phi…

Кеши первого уровня - кеш инструкций L1 I-Cache и кеш данных L1 D-Cache

–размер - по 32 Кб

–размер строки - 64 байта

–степень ассоциативности – 8

–«чистая» латентность - 1 такт

–средняя латентность доступа - 3 такта

–load-to-use латентность - 1 такт (целочисленное значение, загруженное на текущем такте из кеша, может быть использовано на следующем такте целочисленной инструкцией, для векторных инструкций может быть больше)

–обслуживает до ~38 одновременных запросов на ядро

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

22 |

Иерархия памяти Intel Xeon Phi…

Кеш второго уровня L2

–размер - 512 Кб

–размер строки - 64 байта

–степень ассоциативности – 8

–32 Гб кешируемых адресов (размер адреса 35 бит)

–«чистая» латентность доступа - 11 тактов

–средняя латентность доступа - 14-15 тактов

–имеет аппаратное потоковое устройство предвыборки, способное выполнять избирательную предвыборку инструкций для исполнения и данных для операций чтения и записи

•может инициировать до 4 составных запросов предвыборки, позволяет инициировать параллельную предвыборку до 4 Кб данных

–обслуживает до ~38 одновременных запросов на ядро

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

23 |

Иерархия памяти Intel Xeon Phi

Оперативная память

–8 встроенных контроллеров памяти, каждый обслуживает по два 32-битных канала GDDR5

–суммарная производительность - 5,5 GT/s (миллиардов пересылок в секунду)

–суммарная пропускная способность - 352 GB/s

–латентность доступа - более 300 тактов

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

24 |

Иерархия памяти Intel Xeon Phi

Компонент сопроцессора, реализующий клиентскую логику PCI Express, также обеспечивает работу механизма прямого доступа к памяти (DMA). 8 независимых каналов DMA, работающих на той же частоте, что и ядра сопроцессора, могут выполнять следующие типы передачи данных:

–из GDDR5-памяти сопроцессора в оперативную память хоста

–из оперативной памяти хоста в GDDR5-память сопроцессора

–из GDDR5-памяти в GDDR5-память в пределах сопроцессора

–Выполнение операции передачи данных может быть запрошено как со стороны центрального процессора хоста, так и со стороны сопроцессора

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

25 |

Программное обеспечение сопроцессора Intel Xeon Phi

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

26 |

Программное обеспечение сопроцессора Intel Xeon Phi

Архитектура и состав программного обеспечения для сопроцессора Intel Xeon Phi ориентированы на выполнение высокопроизводительных приложений, способных максимально использовать возможность одновременного выполнения сотен потоков

Встроенное ПО позволяет использовать его в системах с шиной PCI Express, работающих под управлением операционных систем Linux или Windows*

* На текущий момент только в режиме отдельного MPI узла

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

27 |

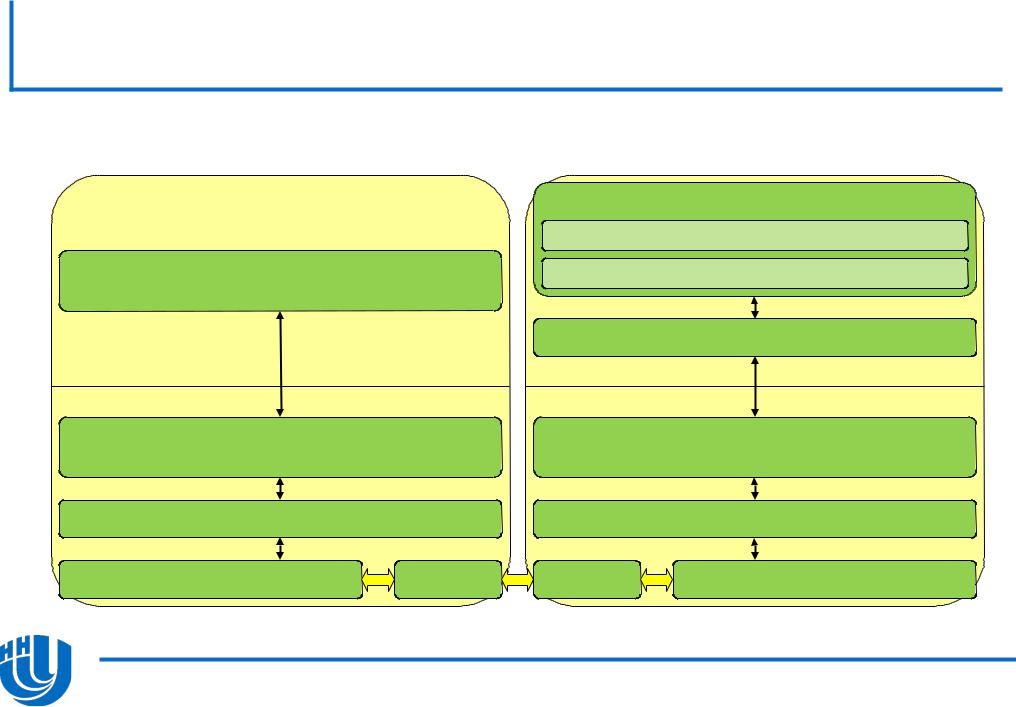

Операционная система сопроцессора Intel

Xeon Phi…

С точки зрения базовой ОС сопроцессор представляет собой отдельный вычислительный SMP-домен, работающий под управлением собственной операционной системы и слабо связанный с основными процессорами системы

ОС сопроцессора базируется на стандартном ядре Linux, в которое были внесены минимально возможные изменения, требуемые для поддержки новой архитектуры

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

28 |

Операционная система сопроцессора Intel

Xeon Phi…

Центральный процессор |

|

Сопроцессор Intel Xeon Phi |

|

|

|

|

Приложение Xeon Phi |

|

|

|

Пользовательский код |

ssh-клиент |

|

Библиотеки (ОС или сторонние) |

|

(например, ssh mic0) |

|

||

|

|

|

|

|

|

|

ssh-сервер |

Уровень пользователя |

|

Уровень пользователя |

|

Уровень ядра |

|

Уровень ядра |

|

Драйверы, библиотеки и утилиты |

Драйверы, библиотеки и утилиты |

||

поддержки Intel Xeon Phi |

|

|

поддержки Intel Xeon Phi |

ОС Linux/Windows |

|

|

ОС Linux |

Центральный процессор |

PCIe |

PCIe |

Сопроцессор Xeon Phi |

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

29 |

Модели использования сопроцессора Intel Xeon Phi

Нижний Новгород, 2015 |

Введение в архитектуру Intel Xeon Phi |

30 |