- •Министерство образования московской области

- •Содержание

- •Лабораторная работа №1. Изучение полупроводникового диода и стабилитрона

- •2. Полевые транзисторы

- •Лабораторная работа №2. Изучение полевого транзистора с управляющим p-n переходом

- •3. Биполярные транзисторы

- •Лабораторная работа №3. Изучение биполярного транзистора

- •4. Электронные усилители

- •Лабораторная работа №4. Изучение резисторного усилителя напряжения

- •5. Логические элементы цифровых устройств

- •Лабораторная работа №5. Изучение основных логических элементов

- •6. Триггеры

- •Лабораторная работа №6. Изучение триггеров rs, d и т типов

- •7. Регистры

- •Что такое регистр? Каково его назначение?

- •Инструкции по эксплуатации используемых приборов Генератор сигналов г3-33

- •Осциллограф универсальный с1-67

- •Развертка

- •Синхронизация

- •Измерение временных интервалов.

- •Измерение частоты.

- •Измерение амплитуды исследуемых сигналов.

- •Стенд универсальный оавт

- •Литература

6. Триггеры

Триггер - это устройство последовательностного типа имеющее два устойчивых состояния равновесия. Из одного устойчивого состояния в другое триггер переключается под действием входных сигналов. При этом напряжение на его выходах изменяется скачкообразно. Эта особенность позволяет использовать триггеры для записи и хранения 1 бита информации (логического 0 или логической 1).

По способу записи

информации триггеры делятся на асинхронные

и синхронные.

В асинхронные триггеры информация

записываться в любой момент времени

под действием информационных сигналов,

действующих на его входах. В синхронные

(тактируемые) триггеры информация с

информационных входов записывается

только в момент действия, так называемого

синхронизирующего сигнала. Записанная

информация появляется на выходах: прямом

Q

и инверсном

.

Состояние триггера определяется по

прямому выходуQ.

.

Состояние триггера определяется по

прямому выходуQ.

В цифровых устройствах наибольшее распространение получили RS-триггер, синхронный D-триггер и счетный Т-триггер.

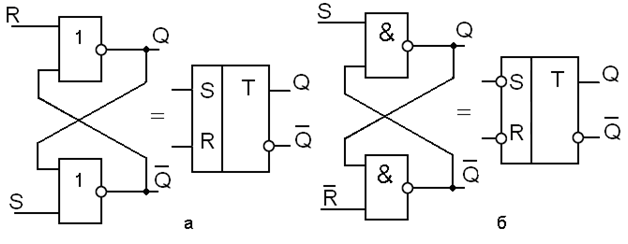

Асинхронный RS-триггер. RS-триггер имеет два входа: S (от англ. Set – установка) и R (от англ. Reset – сброс). RS-триггеры бывают с прямыми и инверсными входами. RS-триггер с прямыми входами построен на двух логических элементах ИЛИ-НЕ. Его структурная схема и условное графическое обозначение представлены на рисунке 1,а. Для получения такого триггера нужно выход каждого из элементов подключить к одному из входов другого элемента. RS-триггер с инверсными входами построен на двух логических элементах И-НЕ, структура аналогична (рис. 1,б).

Рис. 1

Уровень входного сигнала, однозначно определяющий логический уровень выходного сигнала триггера называется активным уровнем. Для RS-триггера с прямыми входами активным является высокий уровень, а для RS-триггера с инверсными входами – низкий уровень. Уровни сигналов, подача которых на один из входов не приводит к изменению логического уровня на выходе элемента, называют пассивным.

Из рисунка 1,а для триггера с прямыми входами следует:

,

,

.

.

При S=1 и R=0 происходит

установка триггера в устойчивое состояние

с Q=1 и

=0

(режим записи логической 1). При S = 0 и R =

1 происходит установка триггера в

устойчивое состояние с Q=0 и

=0

(режим записи логической 1). При S = 0 и R =

1 происходит установка триггера в

устойчивое состояние с Q=0 и =1

(режим записи логического 0). При S=R=0

триггер сохраняет предыдущее состояние

(режим хранения логической 1 или

логического 0). При S=R=1 логические уровни

на выходах триггера одинаковы Q=

=1

(режим записи логического 0). При S=R=0

триггер сохраняет предыдущее состояние

(режим хранения логической 1 или

логического 0). При S=R=1 логические уровни

на выходах триггера одинаковы Q= =0.

Такое состояние является неопределенным,

так как после окончания действия входных

сигналов триггер может равновероятно

принять любое из устойчивых состояний.

И поэтому такая комбинация входных

сигналов является запрещенной и в работе

триггера не используется. В исходный

момент времени состояние триггера –

величина случайная.

=0.

Такое состояние является неопределенным,

так как после окончания действия входных

сигналов триггер может равновероятно

принять любое из устойчивых состояний.

И поэтому такая комбинация входных

сигналов является запрещенной и в работе

триггера не используется. В исходный

момент времени состояние триггера –

величина случайная.

Из рисунка 1,б для триггера с инверсными входами следует:

,

,

.

.

При

=0,

=0, =1

происходит установка триггера в

устойчивое состояние с Q=1 и

=1

происходит установка триггера в

устойчивое состояние с Q=1 и =0

(режим записи логической 1). При

=0

(режим записи логической 1). При =1,

=1, =0

происходит установка триггера в

устойчивое состояние с Q=0 и

=0

происходит установка триггера в

устойчивое состояние с Q=0 и =1

(режим записи логического 0). При

=1

(режим записи логического 0). При =

= =1

триггер сохраняет предыдущее

состояние(режим хранения логической 1

или логического 0). Комбинация входных

сигналов

=1

триггер сохраняет предыдущее

состояние(режим хранения логической 1

или логического 0). Комбинация входных

сигналов =

= =0

является запрещенной.

=0

является запрещенной.

Основными недостатками RS-триггера являются:

входная информация подается по двум отдельным входам (R, S);

существует запрещенная комбинация входных сигналов;

обладает низкой помехоустойчивостью.

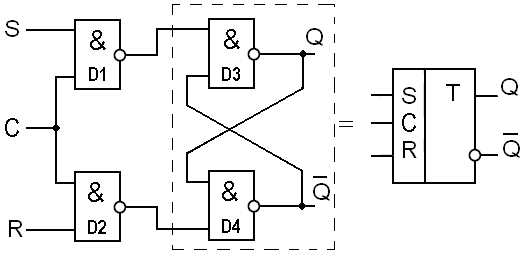

Синхронный RS-триггер строится из четырех логических элементов И-НЕ (рис. 2, а). Переключение триггера из одного устойчивого состояния в другое под действием сигналов на входах S и R происходит только при наличии сигнала высокого уровня на входе С (С=1).

а б Рис. 2

При С=1 элементы

D1

и D2

будут инвертировать информацию

поступающую по входам S

и R.

При С=0 на выходах элементов D1

и D2

будут уровни логической 1, что для

следующего за элементами D1

и D2

асинхронного RS–триггера

с инверсными входами на элементах D3

и D4

задаст режим хранения ранее записанной

информации. При С=1, S=0

и R=0

триггер также будет находится в режиме

хранения информации, так как на выходах

входных элементов D1

и D2

будут уровни логической единицы. При

С=1, S=1

и R=0

произойдет установка триггера в

устойчивое состояние с Q=1 и

=0

(режим записи логической 1). При С=1,S=0

и R=1

произойдет установка триггера в

устойчивое состояние с Q=0 и

=0

(режим записи логической 1). При С=1,S=0

и R=1

произойдет установка триггера в

устойчивое состояние с Q=0 и

=1

(режим записи логического 0). При С=1,S=1

и R=1

логические уровни на выходах триггера

будут одинаковы Q=

=1

(режим записи логического 0). При С=1,S=1

и R=1

логические уровни на выходах триггера

будут одинаковы Q= =1

– запрещенный режим.

=1

– запрещенный режим.

Синхронный D-триггер. D-триггер (от англ. Delay - задержка) имеет информационный вход D (от англ. Data – данные) и вход синхронизации С (от англ. Clock – тактовая последовательность).

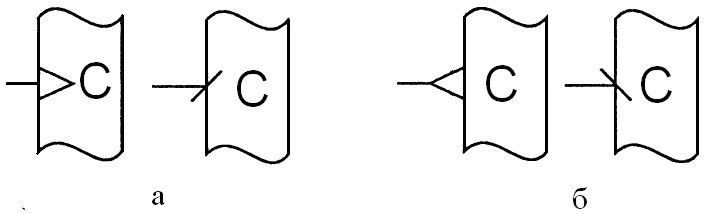

Синхронные D-триггеры могут быть с потенциальным (статический D-триггер) и динамическим (динамический D-триггер) управлением. В статический D-триггер информация записывается в течение времени, при котором на входе синхронизации С высокий уровень сигнала (С=1). В динамический D-триггер информация записывается либо при положительном перепаде напряжения от 0 к 1 на входе синхронизации С (по фронту синхронизирующего импульса), либо при отрицательном перепаде напряжения от 1 к 0 (по срезу синхронизирующего импульса). Если триггер срабатывает по фронту синхронизирующего импульса то вход С изображают, как показано на рисунке 3,а, если по срезу – рис. 3,б.

Рис. 3

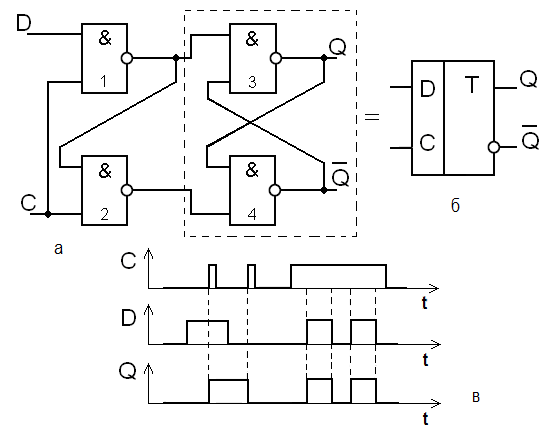

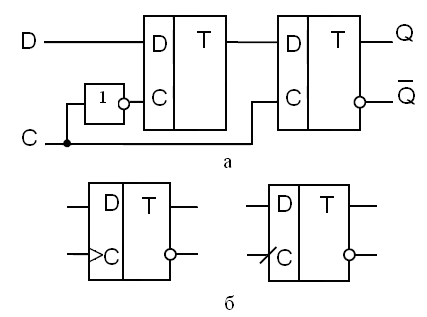

Статический D-триггер. На рисунке 4 изображены одна из возможных структурных схем статического D-триггера и его условное графическое обозначение.

При низком уровне

сигнала на входе С (C=0) триггер находится

в режиме хранения информации и не

реагирует на сигналы на информационном

входе D. При этом на входы RS-триггера с

инверсными входами (элементы D3 и D4)

поступают пассивные уровни ( =

= =1).

При подаче на вход синхронизации сигнала

высокого уровня (С=1) инфоpмация

на пpямом

выходе Q

будет повторять информацию, поступающую

на вход D (режим записи) (рис. 4,в).

=1).

При подаче на вход синхронизации сигнала

высокого уровня (С=1) инфоpмация

на пpямом

выходе Q

будет повторять информацию, поступающую

на вход D (режим записи) (рис. 4,в).

Рис. 4

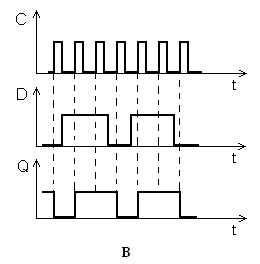

Динамический D-триггер тактируемый фронтом тактового импульса, можно выполнить из двух статических D-триггеров по схеме, показанной на рис. 5,а.

Рис. 5

При С=0 первый триггер повторяет сигнал D, второй триггер находится в режиме хранения и не реагирует на сигналы на его входе D. При переходе к С=1 первый триггер перейдет в режим хранения, записанной в него информации, а второй повторит ее на своем выходе. Таким образом, рассмотренная схема по фронту тактового импульса записывает информацию с входа D и сохраняет его до следующего фронта. Триггеры с динамическим управлением необходимы для построения счетчиков и регистров.

На рисунке 5,б изображены временные диаграммы динамического D-триггера. После записи информация в таком триггере хранится до следующего положительного перепада напряжения на входе синхронизации. Если входная информация не изменяется, то после положительного перепада напряжения на С - входе и выходная информация не изменится.

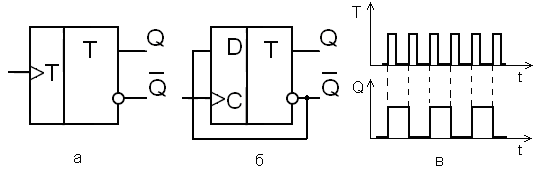

Счетный Т-триггер

(от

англ. Toggle – переключатель)

имеет один управляющий вход Т и два

выхода Q и

(рис. 6,а). Т-триггер может быть собран на

базе динамического D-триггера, для этого

необходимо его инфоpмационный

вход D соeдинить

с инвеpсным

выхoдом

(рис 6,б). Если в начальный момент времени

на выходе Q

был уровень логического 0, то на входе

D

был уровень логической 1 (т.к.

(рис. 6,а). Т-триггер может быть собран на

базе динамического D-триггера, для этого

необходимо его инфоpмационный

вход D соeдинить

с инвеpсным

выхoдом

(рис 6,б). Если в начальный момент времени

на выходе Q

был уровень логического 0, то на входе

D

был уровень логической 1 (т.к.

=1).

По фронту синхроимпульса единица сD-входа

перепишется на выход Q,

на входе

=1).

По фронту синхроимпульса единица сD-входа

перепишется на выход Q,

на входе

и входеD

появится нулевой уровень. В следующем

такте на выходе Q

появится уровень логического 0 и т.д.

Таким образом триггер будет изменять

свое состояние на противоположное при

каждом положительном перепаде напряжения

на Т-входе.

и входеD

появится нулевой уровень. В следующем

такте на выходе Q

появится уровень логического 0 и т.д.

Таким образом триггер будет изменять

свое состояние на противоположное при

каждом положительном перепаде напряжения

на Т-входе.

Из временной диаграммы изображенной на рисунке 6,в видно, что частота сигнaла на выхoде Т-триггера в два раза ниже частоты сигнала на входе. Это позволяет использовать триггер в качестве делителя частоты и двоичного счетчика.

Рис. 6

Контрольные вопросы.

Что называется триггером?

Какие триггеры называются асинхронными, а какие синхронными?

Какие выходы бывают у триггеров, как их обозначают?

Какие входы бывают у триггеров, как их обозначают?

Опишите структуру RS-триггера с прямыми входами.

При каких входных сигналах RS-триггер с прямыми входами будет находится в режиме записи; в режиме хранения; в запрещенном режиме?

Опишите структуру RS-триггера с инверсными входами.

При каких входных сигналах RS-триггер с инверсными входами будет находится в режиме записи; в режиме хранения; в запрещенном режиме?

Почему RS-триггер на элементах ИЛИ-НЕ называется триггером с прямыми входами?

Почему RS-триггер на элементах И-НЕ называется триггером с инверсными входами?

Назовите основные недостатки асинхронного RS-триггера

Опишите устройство и принцип действия синхронного RS-триггера.

Опишите устройство и принцип действия статического D-триггера.

Опишите устройство и принцип действия динамического D-триггера.

Как получить Т-триггер, имея в наличии D-триггер?