1_avr8_interfaces_USART

.pdf

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

1 USART

Загальні відомості про інтерфейс USART

Універсальний синхронний та асинхронний приймач-передавач (Universal Synchronous and Asynchronous serial Receiver and Transmitter, або скорочено USART) – це гнучкий інтерфейс мікроконтролерів AVR, який забезпечує двосторонню передачу даних з широкими можливостями вибору параметрів зв’язку. Інтерфейсом USART оснащені більшість 8-розрядних мікроконтролерів AVR, в т.ч. і усе сімейство ATmega. Інтерфейс USART є послідовним, тобто біти інформації передаються по одній лінії. Якщо передавання даних здійснюється в обох напрямках, використовується дві лінії – для приймання та передавання даних (виводи RxD та TxD відповідно).

При використанні USART можна вибрати режим асинхронного або синхронного передавання даних. При асинхронному передаванні даних передавач та приймач працюють незалежно один від одного і тому при цьому не потрібно окремої лінії синхронізації. Звичайно ж, приймач і передавач повинні мати однакові налаштування, тому "незалежність" не слід розуміти занадто буквально. Мається на увазі те, що при асинхронному передаванні немає спільного тактування передавач та приймача, згідно якого передається кожен біт. Передавання здійснюється кадрами, кожен з яких починається стартовим бітом та закінчується одним або двома стоповими бітами. Приймач постійно опитує лінію даних і по наявності стартового біту робить висновок про початок передавання кадру, а при виявленні стопового біту робить висновок, що передавання кадру завершено. При використанні синхронного режиму додатково використовується ще одна лінія синхронізації (вивід XCK).

Інтерфейс USART є досить гнучким, оскільки крім вибору асинхронного чи синхронного режиму, він дозволяє в широким межах встановлювати швидкість передачі, використовувати різну кількість бітів в кадрі та застосовувати перевірку цілісності даних. За протоколом передачі даних інтерфейс USART сумісний з інтерфейсом RS-232, по якому передаються дані через послідовний порт персонального комп’ютера. Але напруги, які визначають рівні логічного нуля та одиниці, не співпадають, тому необхідно використовувати перетворювачі рівнів.

Як працює USART

Апаратно інтерфейс USART поділяється на три блоки: генератор тактового сигналу, передавач та приймач, що зображено на рис. 1.1. Генератор тактового сигналу здійснює тактування приймача та передавача. Зрозуміло, що швидкість обміну даними також залежить і від частоти сигналу, що виробляється системним тактовим генератором. Власне тактовий сигнал виробляє контролер швидкості передачі даних (baud rate generator). Його основу складає лічильник зворотного рахунку, який тактується системним тактовим сигналом. Початкове завантаження лічильника здійснюється з 16-розрядного регістру швидкості передачі даних UBBR[H:L]. Як тільки лічильник дорахує до нуля, на виході лічильника з’являється імпульс, а лічильник знову завантажується з регістру UBBR. В залежності від режиму роботи частота імпульсів лічильника ділиться на 16, 8 або 2. Записуючи різні значення в UBBR, можна встановлювати бажану швидкість обміну даними. Вирази для обчислення значення, яке потрібно завантажити в регістр UBBR для отримання бажаної швидкості передачі (і навпаки), приведені в таблиці 1.1.

Таблиця 1.1 – Вирази для обчислення швидкості передачі сигналу

|

|

Обчислення |

швидкості |

Обчислення |

|

значення |

|||||||

|

|

передачі даних |

UBRR |

|

|

|

|

||||||

Нормальний асинхронний |

BAUD = |

|

FOSC |

UBRR = |

FOSC |

|

|

−1 |

|||||

режим |

|

|

|

|

|

|

|

|

|||||

|

|

16(UBRR +1) |

|

16BAUD |

|||||||||

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||

Асинхронний |

режим з |

BAUD = |

|

|

FOSC |

|

UBRR = |

FOSC |

|

−1 |

|||

подвоєною швидкістю |

8(UBRR +1) |

8BAUD |

|||||||||||

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|||||

Синхронний |

режим |

BAUD = |

|

|

FOSC |

UBRR = |

FOSC |

|

−1 |

||||

Master |

|

|

|

|

|

2BAUD |

|

||||||

|

|

|

2(UBRR +1) |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В таблиці 1.1 швидкість передачі даних (BAUD) визначається в бітах на секунду. Максимальне значення, яке можна записати в регістр UBBR, становить 4095, оскільки використовуються лише 12 бітів з 16. В таблиці 60

1

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

на с.159 технічного опису ATmega8 представлено приклади значень UBBR для деяких значень частоти системного тактового генератора.

В синхронному режимі робота генератора тактового сигналу залежить від того, чи МК знаходиться в режимі Master, чи Slave. Якщо МК працює в режимі Master, то генератор тактового сигналу відповідальний за формування тактового сигналу для підлеглого пристрою (пристроїв) Slave на виводі XCK. Якщо ж МК є підлеглим, він сам отримує сигнал синхронізації через вивід XCK від пристрою Master, який використовується для тактування блоків приймача і передавача. В асинхронному режимі лінія XCK не використовується, і усі пристрої на шині USART тактуються незалежно, кожен від свого внутрішнього генератора.

Рисунок 1.1 – Структурна будова інтерфейсу USART

Передавання даних здійснюється наступним чином. Дані для передавання заносяться в буферний регістр UDR. Якщо робота передавача дозволена, команда запису в регістр UDR автоматично ініціює початок передавання кадру. Дані з буферу UDR заносяться в регістр зсуву передавача, а він по черзі "виштовхує" усі біти на лінію TxD. Кожен біт передається по надходженню тактового імпульсу з блоку генератора тактового сигналу. Як видно з рис. 1.1, тактовий сигнал поступає або з контролера швидкості передачі даних (в асинхронному режимі чи в синхронному режимі Master), або з лінії XCK (синхронний режим Slave). Таким чином, для передавання кадру необхідно лише записати дані в буферний регістр UDR, далі модуль USART усе зробить автоматично. Після закінчення передавання кадру встановлюється прапорець закінчення передавання, а також може генеруватись переривання. Якщо встановлено відповідну опцію, до складу кадру додається біт паритету. Біт паритету встановлюється чи скидається в залежності від того, парною чи непарною є кількість бітів даних в кадрі, які дорівнюють одиниці, і дозволяє здійснити перевірку цілісності прийнятих даних (детальніше про обчислення біту паритету трохи пізніше).

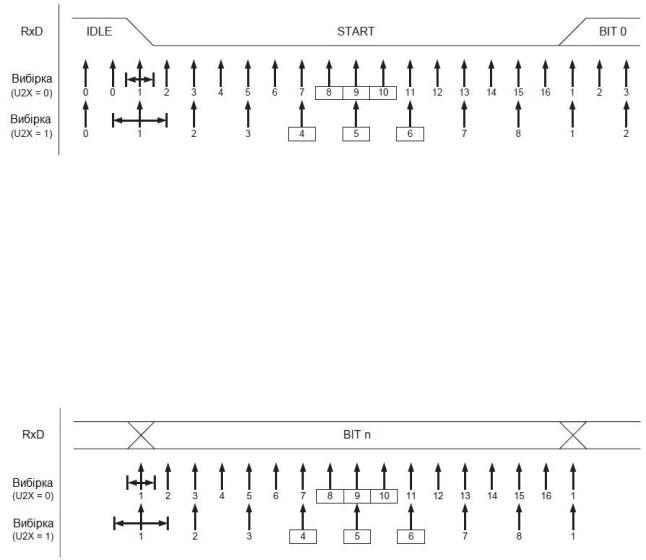

Тепер про роботу приймача. Зосередимо увагу на роботі приймача в асинхронному режимі, оскільки в усіх пропонованих нижче прикладах використовується лише він. Нехай лінія знаходиться в стані очікування (високий рівень). Блок отримання тактового сигналу постійно опитує стан виводу RxD, і як тільки він виявить перепад з високого в низький логічний рівень, ініціюється послідовність виявлення стартового біту (рис.

2

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

1.2). При цьому фактично здійснюється дискретизація сигналу на лінії RxD, частота дискретизації в 16 разів більша за швидкість передачі даних в нормальному режимі, та у 8 разів в режимі подвоєної швидкості. Горизонтальні стрілки показують відхилення синхронізації під час здійснення вибірки. Зауважте, що в режимі з подвоєною швидкістю відхилення синхронізації більше. Відліки, позначені як “0” отримані коли лінія RxD знаходилась в стані очікування.

Рисунок 1.2 – Вибірка стартового біта в асинхронному режимі

Нехай відлік 1 це перший відлік з нульовим рівнем, як показано на рисунку. Блок отримання тактового сигналу використовує відліки 8, 9 та 10 в нормальному режимі, та 4, 5 та 6 в режимі з подвоєною швидкістю (ці відліки показані на рисунку в рамках), для того, що визначати, чи прийнятий стартовий біт є дійсним. Якщо два чи більше з цих трьох відліків мають високий логічний рівень (тобто більшість з трьох), стартовий біт відкидається як імпульсна завада і приймач починає виявлення наступного переключення лінії з високого в низький логічний рівень. Якщо виявлено дійсний стартовий біт (два або більше вищезгаданих відліків мають нульове значення), синхронізація блоку отримання тактового сигналу успішно завершується і може починатись отримання даних. Процес синхронізації повторюється для стартового біту кожного наступного кадру.

Коли приймач синхронізований по стартовому біту, можна починати отримання даних. Вибірка бітів даних та біту паритету зображена на рис. 1.3.

Рисунок 1.3 – Вибірка бітів даних в асинхронному режимі

Визначення логічного рівня прийнятого біту здійснюється по логічному рівню більшості з трьох відліків в середині вибірки прийнятого біту (номери цих відліків на рисунку обведені рамками). Якщо два або усі три відліки мають високий логічний рівень, прийнятий біт реєструється як такий, що має рівень логічної одиниці. Якщо два або усі три відліки мають низький логічний рівень, прийнятий біт реєструється як такий, що має рівень логічного нуля. Цей процес оцінювання рівня сигналу по значенню більшості відліків (majority voting process) діє як фільтр низьких частот для вхідного сигналу на виводі RxD. Процес повторюється, поки не буде прийнято цілий кадр, включно із першим стоповим бітом. Зауважте, що приймач використовує лише перший стоповий біт кадру.

Процес вибірки стопового біту зображено на рис. 1.4. Для виявлення стопового біту використовується той самий принцип підрахунку кількості відліків з однаковим рівнем, що і при оцінюванні бітів даних та біту парності. Якщо стоповий біт реєструється як такий, що має рівень логічного нуля, встановлюється прапорець помилки кадру FE (Frame Error) в регістрі UCSRA. Новий перехід від високого до низького рівня сигналізує про можливість появи нового кадру після останнього зареєстрованого біту.

3

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

Рисунок 1.4 – Вибірка стопового біту

Усі прийняті біти даних кадру послідовно згідно тактового сигналу заносяться в регістр зсуву приймача. Коли останній біт кадру прийнято, вміст регістру зсуву переноситься в буферний регістр приймача UDR і встановлюється прапорець закінчення приймання. Для отримання прийнятих даних необхідно просто зчитати вміст регістру UDR.

Буферний регістр є дворівневим і таким чином разом з регістром зсуву приймач може утримувати три прийнятих кадри. Якщо в такій ситуації буде виявлено стартовий біт наступного кадру до того, як буде хоча б раз прочитаний буферний регістр UDR, відбудеться втрата даних, при цьому встановлюється прапорець переповнення даних DOR (Data OverRun) в регістрі UCSRA.

Також є нюанси із зчитуванням буферу UDR, коли здійснюється контроль прапорців помилок. Значення прапорців помилок для кожного прийнятого кадру буферизуються разом з самим кадром, і зчитувати прапорці помилок треба до зчитування регістру UDR, тому що після цього вони будуть втрачені (для того кадру, який був щойно зчитаний з регістру UDR). Річ в тому, що операція зчитування буферного регістру UDR дає команду мікроконтролеру записати на його місце наступний прийнятий кадр, і прапорці помилок будуть відображати вже його статус.

Аналогічна ситуація виникає, коли використовується формат кадру з 9 бітами даних. При цьому вісім молодших бітів даних кадру зчитуються з буферного регістру UDR, а дев’ятий біт заноситься приймачем в біт RXB8 регістру UCSRB. Послідовність зчитування бітів даних повинна бути такою: спочатку зчитується старший біт даних кадру з біту RXB8 регістру UCSRB, а потім молодші біти даних кадру з регістру UDR, інакше старший біт буде втрачено (детальніше про формат кадру з 9 бітами даних див. в технічному описі ATmega8).

Формати кадру при передаванні даних по інтерфейсу USART

До складу кадру входить один символ, який складається з кількох бітів даних, бітів синхронізації (стартта стоп-біти), та опціально – біту паритету для перевірки помилок. USART підтримує усі 30 можливих комбінацій формату кадру:

•1 старт-біт

•5, 6, 7, 8 або 9 бітів даних

•Біт паритету (парності/непарності) або відсутність цього біту

•1 або 2 стопових біти

Кадр (рис. 1.5) починається з стартового біту, після чого іде наймолодший значущий біт даних. Далі ідуть наступні біти даних (максимальна кількість 9). Після цього, перед стоповими бітами, може іти біт паритету. Після передавання повного кадру одразу може здійснюватись передавання наступного кадру, або лінія зв’язку може бути встановлена в стан очікування (високий рівень напруги). Біти в квадратних дужках є опціальними.

Рисунок 1.5 – Структура кадру при передачі даних через USART: IDLE – лінія в режимі очікування (високий рівень); St – старт-біт; 0...8 – біти даних; Sp1, Sp2 – стоп-біти

4

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

Використання біту паритету

Для перевірки цілісності прийнятих даних використовується біт паритету. При цьому може використовуватись перевірка або на парність, або на непарність. Якщо використовується перевірка на парність, підраховується кількість встановлених в одиницю бітів даних, і якщо кількість одиничних бітів парна, біт паритету встановлюється в одиницю, інакше – встановлюється в нуль. Насправді при цьому біт паритету Peven обчислюється виконанням операції “виключне АБО” для усіх бітів даних:

PEVEN = DN−1 K D3 D2 D1 D0 0

Справедливість даного виразу нескладно підтвердити експериментально. Якщо використовується перевірка на непарність, то біт паритету встановлюється в одиницю, коли кількість одиничних бітів даних є непарною. При цьому біт паритету Podd також обчислюється виконанням операції “виключне АБО” для усіх бітів даних, але результат інвертується:

PODD = DN−1 K D3 D2 D1 D0 1

Якщо встановлено режим перевірки паритету (за це відповідають біти UPM1:0 в регістрі UCSRC), передавач для кожного кадру обчислює біт паритету (парності або непарності, в залежності від налаштувань бітів UPM1:0) і додає його до вмісту кадру (див. формат кадру на рис. 1.5). Після приймання кадру приймач також обчислює біт паритету і порівнює його із бітом паритету з прийнятого кадру. Якщо значення прийнятого та обчисленого бітів не співпадають, це свідчить про помилку даних, при цьому встановлюється прапорець помилки паритету PE в регістрі UCSRA.

Прапорці стану приймача та передавача USART

Приймач USART має прапорець RXC в регістрі UCSRA, який показує, чи є непрочитані дані в буфері приймання. Цей прапорець дорівнює одиниці, якщо в буфері приймання є непрочитані дані, і дорівнює нулю, якщо буфер приймання порожній (тобто не містить непрочитаних даних). При відключеному приймачі (біт RXEN в регістрі UCSRB дорівнює нулю) буфер приймання буде скинуто і прапорець RXC буде зчитуватись як нуль. Якщо встановлено прапорець дозволу переривання завершення приймання RXCIE в регістрі UCSRB, переривання завершення приймання USART буде викликатись увесь час, поки встановлений прапорець RXC (якщо є глобальний дозвіл на переривання). Якщо використовується приймання даних по перериванню, підпрограма завершення приймання повинна зчитати дані з регістру UDR для того щоб скинути прапорець RXС, інакше нове переривання виникне одразу після виходу з даної підпрограми.

Передавач USART має два прапорці, які показують його стан: прапорець спустошення регістру даних UDRE в регістрі UCSRA та прапорець закінчення передавання TXC (також в регістрі UCSRA). Обидва прапорці можуть генерувати переривання.

Прапорець спустошення регістру даних UDRE показує чи готовий буфер передавача отримати нові дані. Цей біт встановлюється, коли буфер передавача пустий, та скидається, коли буфер передавача містить дані, які ще не були переміщені в регістр зсуву. Для сумісності з наступними моделями МК завжди записуйте в цей біт нуль при записі в регістр UCSRA.

Якщо біт дозволу переривання по спустошенню регістру даних UDRIE в регістрі UCSRB встановлений в одиницю, тоді після встановлення прапорця UDRE та при глобально дозволених перериваннях генерується переривання спустошення регістру даних. Після запису в UDR біт UDRE скидається. Якщо використовується передавання даних по перериванню, підпрограма обробки переривання спустошення регістру даних може записувати нові дані в UDR для того, щоб очистити UDRE або заборонити переривання по спустошенню регістру даних, інакше після виходу з підпрограми оброки переривання виникне нове переривання.

Прапорець закінчення передавання TXC встановлюється, якщо з регістру зсуву передавача був переміщений цілий кадр, і в буфері передавача немає даних для передавання. Прапорець ТХС автоматично скидається при переході до обробки відповідного переривання, або може бути очищений програмно записом в нього логічної одиниці. Прапорець ТХС корисний при повнодуплексному зв’язку (наприклад стандарт RS485), де передаюча сторона повинна перейти до режиму приймання і звільнити шину одразу після закінчення передавання.

Якщо встановлюється прапорець TXCIE дозволу переривання по закінченню передавання в регістрі UCSRB і якщо в регістрі SREG встановлений біт глобального дозволу переривань, при встановленні прапорця TXC буде згенеровано переривання. Якщо використовується переривання по закінченню передавання,

5

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

підпрограма обробки переривання не повинна скидати прапорець TXC, це здійсниться автоматично після закінчення роботи підпрограми.

Приклади роботи з USART

Перед початком роботи модуль USART необхідно ініціалізувати. В першу чергу, в регістр UDRR необхідно записати значення, яке визначає швидкість обміну даними (як його обчислити, ми вже розглянули). Далі потрібно встановити режим роботи USART шляхом встановлення бітів в трьох регістрах керування: UCSRA, UCSRB та UCSRC. Нижче представлено зведений перелік бітів керування режимами роботи USART (детальний опис бітів див. в технічному описі ATmega8):

•Біт UMSEL в регістрі UCSRC встановлює асинхронний (UMSEL = 0) чи синхронний (UMSEL = 1) режим роботи

•Біти TXEN та RXEN в регістрі UCSRB дозволяють роботу передавача та приймача

•Біти UCSZ2 (в регістрі UCSRB) та UCSZ1, UCSZ0 (в регістрі UCSRC) визначають кількість бітів даних в кадрі

•Біт U2X в регістрі UCSRA визначає режим передачі з нормальною або подвоєною швидкістю

•Біти UPM1, UPM0 в регістрі UCSRC визначають режим перевірки паритету

•Біт USBS в регістрі UCSRC встановлює кількість стопових бітів (1 або 2)

•Біт UCPOL в регістрі UCSRC налаштовує полярність тактового сигналу (тільки для синхронного режиму)

•Біти TXCIE, RXCIE та UDRIE в регістрі UCSRB дозволяють переривання відповідно при закінченні передавання кадру, при закінченні приймання кадру та при готовності буфера до запису нового кадру для передавання.

•Біт MPCM встановлює мультипроцесорний режим зв’язку (опис мультипроцесорного режиму див. на стор. 151 технічного опису ATmega8)

Ось приклад налаштування USART на асинхронне передавання даних (UMSEL = 0) із швидкістю 9600 біт/с (UBRR = 25), без подвоєння швидкості (U2X = 0), 8 бітів даних в кадрі (UCSZ2 = 0, UCSZ1 = 1, UCSZ0 = 1), один стоп-біт (USBS = 0), без біту паритету (UPM1 = 0, UPM0 = 0), без використання переривань (TXCIE = 0, RXCIE = 0, UDRIE = 0) , при частоті системного тактового сигналу 4 МГц:

ldi r17, 0 ldi r16, 25

out UBRRH, r17 out UBRRL, r16 ldi r16, 1<<TXEN out UCSRB, r16

ldi r16, (1<<URSEL)|(1<<UCSZ1)|(1<<UCSZ0) out UCSRC, r16

Кілька коментарів до вищенаведеного фрагменту коду. Значення для запису в регістр UBRRH:UBRRL отримується по формулі з таблиці 1.1 із заокругленням до цілого (швидкість 9600 біт/с, тактова частота 4 МГц): UBRR = 4000000/ 16 х 9600 – 1 = 25,04 ≈ 25. Оскільки отримане значення менше за 256, в старшу половину UBRR записуємо нуль. Також можна було б скористатись таблицею 61 в технічному описі ATmega, в якій представлено значення для запису в регістр UBRR для різних швидкостей передачі та різних частот використовуваних резонаторів. Якщо значення, яке потрібно записати в UBRR, більше за 255, необхідно виділяти з нього старший та молодший байт макросами HIGH та LOW і здійснювати запис відповідно в старшу та молодшу половину регістру UBRR. Як вже згадувалось вище, максимальне значення, яке можна записати в регістр UBBR, становить 4095. До речі, при передаванні даних через USART тактування МК бажано здійснювати від зовнішнього кварцового резонатора, що збільшує точність генерування внутрішнього тактового сигналу модуля USART.

Досить часто обчислення константи для завантаження регістру UBRR програмісти "доручають" асемблеру, спочатку оголошуючи як константи тактову частоту роботи мікроконтролера та бажану швидкість передачі даних, а потім оголошуючи константу для завантаження регістру UBRR, значення якої обчислюється асемблером з двох попередніх констант безпосередньо в процесі генерації коду:

6

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

|

USART |

|

|

П.Штогрин |

|

|

|

|

|

... |

|

|

|

|

|

|

.equ |

FCLK = 4000000 |

; тактова частота |

|

.equ |

BAUD = 9600 |

; швидкість передачі даних ч-з USART |

|

.equ |

_UBRR = FCLK/(16*BAUD)-1 |

; константа для завантаження UBRR |

|

...

ldi r17, high(_UBRR) ldi r16, low(_UBRR) out UBRRH, r17

out UBRRL, r16

...

Насправді ми вже використовували цю можливість асемблера, коли оголошували константи для завантаження лічильних регістрів таймерів, наприклад для 16-розрядного таймера 1: .equ T = 65536 – 1000:

...

.equ T = 65536-1000

...

ldi r17, high(T) ldi r16, low(T) out TCNT1, r17 out TCNT1, r16

...

Тепер про особливості запису до регістру UCSRC. Річ в тому, що цей регістр разом з регістром UBRRH використовує одну і ту саму адресу в пам’яті В/В. Для того, щоб вказати мікроконтролеру, до якого регістру ми здійснюємо доступ при записі в цю комірку пам’яті, використовується біт URSEL – таке ім’я мають обидва найстарші біти в регістрах UBRR та UCSRC. Якщо він встановлюється в одиницю, буде здійснено запис в регістр UCSRC, якщо він в момент запису буде мати нульове значення, буде здійснено запис до регістру UBRRH.

Тепер розглянемо приклад закінченої програми, яка здійснює вивід даних через USART, а саме після включення МК (або після скидання) виводить через USART текстовий рядок.

; Fclk = 4 МГц |

|

|

.include "m8def.inc" |

Приклад №1 |

|

.equ |

FCLK = 4000000 |

; тактова частота |

.equ |

BAUD = 9600 |

; швидкість передачі даних ч-з USART |

.equ |

_UBRR = FCLK/(16*BAUD)-1 |

; константа для завантаження UBRR |

|

|

|

.def |

buffer = r16 |

; буферний регістр |

.MACRO PRINT_TO_USART |

; макрос для передачі ч-з USART |

|

|

ldi ZH, high(@0<<1) |

; рядка тексту з ПЗП |

|

ldi ZL, low(@0<<1) |

|

|

rcall string_to_USART |

|

.ENDMACRO |

|

|

;================================ |

|

|

init: |

|

|

|

ldi r16, low(RAMEND) |

; ініціалізація стеку |

|

ldi r17, high(RAMEND) |

|

|

out SPH, r17 |

|

|

out SPL, r16 |

|

; ініціалізація USART

; встановлення швидкості передачі ldi r17, high(_UBRR)

7

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

ldi r16, low(_UBRR) out UBRRH, r17

out UBRRL, r16

;дозвіл передавання ldi r16, 1<<TXEN

out UCSRB, r16

;режим передавання

;8 біт даних, 1 стоп-біт, без біту паритету ldi r16, (1<<URSEL)|(1<<UCSZ1)|(1<<UCSZ0) out UCSRC, r16

;================================ |

|

|

main: |

ldi buffer, '*' |

|

|

rcall char_to_USART |

; виводимо через USART один символ |

|

PRINT_TO_USART text_1 ; виводимо рядок тексту ч-з USART |

|

|

rjmp PC |

|

;================================ |

|

|

char_to_USART: |

; підпрограма виводу одного символу |

|

|

sbis UCSRA,UDRE |

; перевіряємо готовність буферу UDR |

|

rjmp char_to_USART |

|

|

out UDR, buffer |

; запис символу в бефер передавача UDR |

|

ret |

|

|

|

|

string_to_USART: |

; підпрограма виводу текстового рядка з ПЗП |

|

|

lpm buffer, Z+ |

; перед викликом в Z повинен бути адреса рядка |

|

cpi buffer, 0 |

; перевірка на закінчення масиву |

|

breq exit |

; |

|

rcall char_to_USART |

; виводимо черговий символ |

|

rjmp string_to_USART |

|

exit: ret ;================================

text_1:

;масив повинен закінчуватись нулем

;0x0D, 0x0A символи переходу на новий рядок

.db "HELLO!!!", 0x0D, 0x0A, "I am ATmega8", 0x0D, 0x0A, 0 ;================================

Налаштування USART в цій програмі такі самі, як і у вищенаведеному прикладі ініціалізації: швидкість передачі 9600 біт/с, 8 бітів даних, 1 стоп-біт, без контролю паритету, тому на розділі ініціалізації зупинятись змісту немає.

Перейдемо до "корисного навантаження": виводу даних через USART. Спочатку виводиться символ "*". Вивід символу здійснює підпрограма char_to_USART. Перед викликом підпрограми символ, який необхідно вивести, записується в регістр з псевдонімом buffer. Алгоритм виводу байту через USART простий:

1)Постійно опитуючи прапорець UDRE в регістрі UCSRA, дочекатись, поки в ньому буде одиниця, що свідчитиме про те, що буферний регістр UDR готовий прийняти дані для передавання.

2)Завантажити символ в буферний регістр UDR, що автоматично ініціює його передавання.

Власне це і робить підпрограма char_to_USART. Тепер подивимось, як через USART виводиться текстовий рядок, який "зашитий" в ПЗП мікроконтролера. Це здійснює підпрограма string_to_USART, яка для зручності "обгорнута" в макрос PRINT_TO_USART, оголошення якого є в розділі ініціалізації. Єдиним параметром макросу є вказівник на текстовий рядок в ПЗП. Використання макросу в даному випадку зручне тим, що якщо нам треба буде виводити кілька текстових рядків в різний час або в різній послідовності, не потрібно буде кожного разу прописувати команди завантаження до вказівного регістру Z адреси початку рядка: макрос це зробить за нас, ми лише передаємо в параметрі макросу мітку, яка вказує на перший байт рядка (про використання макросів див. в главі "Вивід даних на індикатор" в 1 розділі, або в електронній довідці по асемблеру AVR http://www.mymcu.ru/Articles/Atmel11.htm).

Отже, макрос лише вставляє в програму команди завантаження адреси рядка та викликає підпрограму string_to_USART, а вона в циклі завантажує коди символів з ПЗП, перевіряє їх на рівність нулю (ознака

8

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

закінчення рядка) і відправляє в підпрограму char_to_USART, яка по одному виводить їх в через USART. Як тільки з ПЗП завантажується байт з нульовим значенням, вивід припиняється. Зверніть увагу на пару символів 0x0D, 0x0A, яка двічі зустрічається в текстовому рядку. Це символи переходу на новий рядок, якщо символи, що передаються через USART, призначені для виводу на екран.

Перейдемо до того, як перевірити роботу програми. Тут є дві можливості: скористатись симулятором Proteus, або ж підключити мікроконтролер до комп’ютера через термінальну програму.

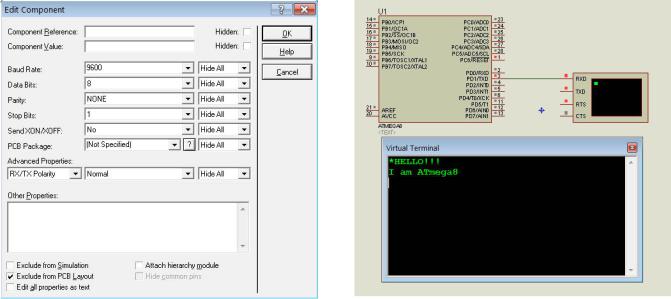

Розглянемо спочатку перший варіант. В симуляторі Proteus є інструмент Virtual Terminal, який призначений для симуляції відсилання та приймання з подальшим відображенням асинхронних даних через порт RS232. Створіть в Proteus проект, з’єднайте вивід TxD мікроконтролера з виводом RxD віртуального терміналу, виберіть в його контекстному меню пункт "Edit Propeties", встановіть ті ж самі параметри з’єднання, що і в програмі для інтерфейсу USART (рис. 1.6). Тепер після старту симуляції на екрані віртуального терміналу повинен з’явитись прийнятий від ATmega8 по RS-232 рядок (рис. 1.7):

Рисунок 1.6 – Налаштування параметрів зв’язку у |

Рисунок 1.7 – Відображення відісланого через USART |

властивостях віртуального терміналу |

текстового рядка на екрані віртуального терміналу |

Якщо під час симуляції викликати контекстне меню екрану віртуального терміналу, і вибрати пункт "Hex Display Mode", прийняті символи будуть виводитись на екран в шістнадцяткових кодах. Цю опцію необхідно вибирати тоді, коли інформацію, яка виводиться через USART, треба інтерпретувати як числові дані, а не текстові символи.

Тепер займемося підключенням мікроконтролера до послідовного порту комп’ютера. Для обміну даними між МК та ПК необхідно лише дві лінії: TxD та RxD. Але безпосередньо підключити ці виводи МК до відповідних ліній послідовного порту не вийде, оскільки напруги логічних рівнів МК та послідовного порту не співпадають, про що вже зазначалось вище. В мікроконтролерах AVR рівню логічного нуля відповідає напруга (– 0,5 Vcc ... 0,2 Vcc), а рівню логічної одиниці – напруга (0,6 Vcc ... Vcc + 0,5 В). В інтерфейсі RS-232 рівні логічних нуля та одиниці мають різну полярність: для встановлення рівня логічного нуля використовується позитивна полярність напруга, а для логічної одиниці – негативна. Також абсолютні значення рівнів напруг можуть бути значно більшими за 5 В (до 15 В для передавача і до 25 В для приймача). Тому безпосередньо підключати послідовний порт AVR до послідовного порту комп’ютера не можна. Необхідно використовувати перетворювачі рівнів. Їх можна реалізувати на транзисторах або можна використати спеціалізовану мікросхему MAX232 або аналогічну. На рис. 1.8 зображено підключення МК до СОМ-порту через транзисторний перетворювач, а на рис. 1.9 – через перетворювач на мікросхемі MAX202.

9

Інтерфейси мікроконтролерів AVR |

(test) |

23.03.2011 |

USART |

|

П.Штогрин |

Рисунок 1.8 – Підключення мікроконтролера з інтерфейсом USART до послідовного порту ПК через перетворювач рівнів на транзисторах

Рисунок 1.9 – Підключення мікроконтролера з інтерфейсом USART до послідовного порту ПК через перетворювач рівнів на спеціалізованій мікросхемі

Для того, щоб побачити символи, які надсилає в послідовний порт комп’ютера мікроконтролер, можна скористатись однією з термінальних програм, наприклад вільно розповсюджуваною Terminal V1.9 (рис. 1.10). Завантажте в МК код з прикладу №1 та підключіть МК до послідовного порту комп’ютера. Запустіть програму Terminal V1.9, виберіть номер COM-порту, до якого підключений МК, встановіть параметри зв’язку (кількість бітів даних у кадрі, кількість стоп-бітів, наявність чи відсутність біту паритету, спосіб керування потоком (вибрати "None"). Тепер натисніть кнопку "Connect", включіть живлення МК, або, якщо він вже включений, натисніть на платі МК кнопку скидання, і на екрані термінальної програми у вікні "Receive" повинен з’явитись відісланий мікроконтролером через USART текстовий рядок. Якщо кілька разів поспіль натиснути кнопку скидання МК, кожного разу через USART буде відіслано рядок (а правильніше – два, оскільки всередині послідовності символів, яка передається, є символи переходу на новий рядок.

10