- •1. Типові вузли, що використовуються для створення 24-розрядного регістра

- •1.1. Загальна характеристика регістрів

- •1.2. Установлювальні мікрооперації. Однофазний і парафазний спосіб записування інформації

- •1.3. Записування інформації від двох джерел

- •1.4. Зчитування інформації

- •1.5. Логічні мікрооперації в регістрах

- •1.6. Мікрооперації зсуву

- •1.7. Перетворення послідовного коду в паралельний і навпаки

- •2. Проектування структурної пристрою

- •3. Проектування функціональної схеми пристрою

- •5. Моделювання спроектованої схеми в пакеті multisim

- •6 .Розробка друкованої плати, 3d-моделі та збірного креслення

- •Висновки

1.7. Перетворення послідовного коду в паралельний і навпаки

Схема чотирирозрядного регістра зсуву вправо на JK-тригерах, яка забезпечує перетворення кодів, показана на рис.4.8, а. Старший розряд регістра за допомогою інвертора на К-вході працює в режимі D-тригера. Нехай від накопичувачів на магнітних дисках або стрічках на вхід регістра по лінії D поступає послідовний код слова А=1101 в напрямку від молодших розрядів до старших. Значення розрядів слова поступає одночасно із синхроімпульсами, які забезпечують як приймання коду в старший розряд, так і одночасний зсув вмісту регістра вправо (рис.4.8, б). Після приходу чотирьох синхроімпульсів на виходах регістра Q4 – Q1 встановлюється код 1101. Таким чином здійснюється перетворення послідовного коду в паралельний, яке часто називають послідовним введенням слова в регістр.

Рис.1.8

Регістр зсуву : а – схема ; б,в –

перетворення послідовного коду в

паралельний і навпаки

Рис.1.8

Регістр зсуву : а – схема ; б,в –

перетворення послідовного коду в

паралельний і навпаки

Перетворення паралельного коду в послідовний також відбувається зсувом слова, яке зберігається. Процес перетворення паралельного коду слова А=1101 в послідовний в напрямку від молодших розрядів до старших за допомогою зсуву вправо показаний на рис.4.8, в.

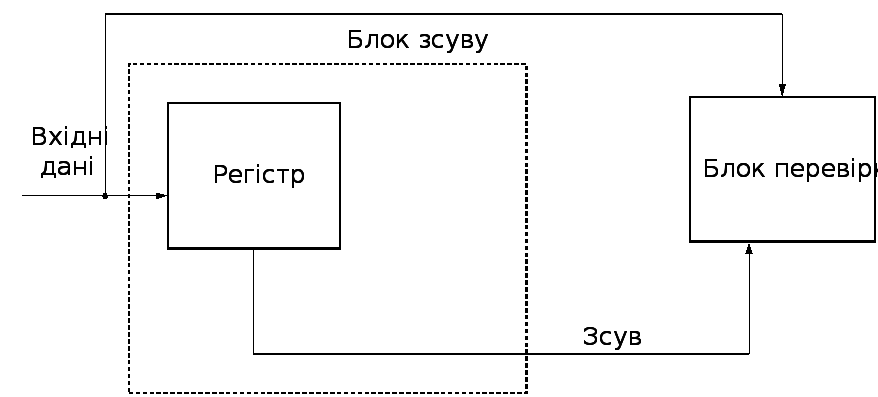

2. Проектування структурної пристрою

Структурна схема 24-розрядного регістру зсуву вліво на два родряди

має дві ланки:

Блок зсуву;

Блок перевірки.

Рис. 2.1 Структурна схема пристрою

Блок сумування побудований на основі шести 8-розрядних регістрів К1533ИР33.

Для перевірки на непарність коду використовуються елементи сумування за модулем 2 М530ЛП5, на які подаються, як і початковий вхідний сигнал, так і зсунутий сигнал. Якщо на виході ми отримаємо одиницю то код непарний, якщо нуль то код парний.

3. Проектування функціональної схеми пристрою

3.1. Перелік вибраних мікросхем

У нас в країні обширна номенклатура інтегральних мікросхем, що випускаються. Для побудови пристроїв автоматики і обчислювальної техніки широке вживання знаходять цифрові мікросхеми серії К155, К555, К1531, К1533, які працюють на ТТЛ(ТТЛШ) логіці. При всіх своїх перевагах – високій швидкодії, обширній номенклатурі, хорошій завадостійкості – ці мікросхеми володіють великою споживаною потужністю.

В даній схемі було використано мікросхеми:

К1533ИР33

К155ЛИ1

КР1533ЛЛ4

М530ЛП5

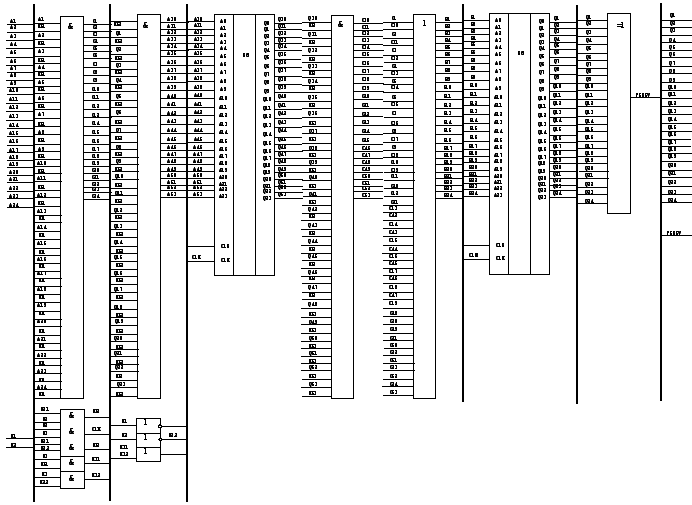

3.2 Функціональна схема пристрою

На рисунку 3.1 зображена функціональна схема 24-розрядного регістру зсуву вліво на два родряди.

На вхід подається 24-розрядний код, що проходить по лініям А1-А24, з ліній Q1-Q24 ми отримуємо вихідний зсунутий код.

Рис. 3.1 Функціональна схема пристрою

4. ПРОЕКТУВАННЯ ЕЛЕКТРИЧНОЇ ПРИНЦИПОВОЇ СХЕМИ ПРИСТРОЮ

4.1. Схема зсуву

За допомогою розробленої схеми можливо виконувати зсув коду на 2 розряди вліво.

Вхідний код уводиться паралельно, за допомогою перемикачав ми встановлюєм рівень логічного нуля чи одиниці. З виходу код також отримується паралельно.

Для зсуву коду було використано два додаткових ключа. Перший ключ при замиканні дозволяє проходити вхідному сигналу. Другий ключ зсуває код на 2 розряди, тобто ключ можна перемикати до тих пір поки код не зсунеться повністю і замість початкового коду будуть нулі.

4.2. Схема перевірки

Окрім зсуву коду дана схема виконує також контроль за непарністю у процесі передачі данних.Для цього в схемі використовуються елементи виключного АБО.

Результат перевірки полягає в сумуванні коду вцілому, якщо на виході отримується одиниця то код непарний, якщо нуль то код парний.

Перевірка виконується в двох місцях, спочатку перевіряється вхідний код, потім коли ми виконали зсув то перевіряється вже вихідний код.

4.2. Принципова схема

На рисунку 4.1 зображено умовне графічне позначення регістра зсуву серії К1533ИР33 [1, 313-315].

Рис. 4.1 Умовне графічне позначення регістра

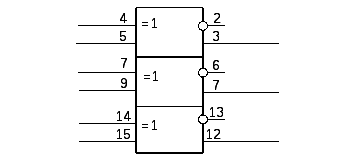

На рисунку 4.2 зображено умовне графічне позначення елементу Виключне АБО КР1531ЛП5 [1, 316-318].

Рис. 4.2 Умовне графічне позначення виключного АБО

На рисунку 4.3 зображено умовне графічне позначення елементу АБО (КР1533ЛЛ4)

Рис. 4.3 Умовне графічне позначення АБО

Якщо хочаб на одному із входів буде 1 то на виході ми одержимо логічну 1, якщо ж на вході будуть подаватись 0 то і на виході ми одержимо 0.