- •1. Типові вузли, що використовуються для створення 24-розрядного регістра

- •1.1. Загальна характеристика регістрів

- •1.2. Установлювальні мікрооперації. Однофазний і парафазний спосіб записування інформації

- •1.3. Записування інформації від двох джерел

- •1.4. Зчитування інформації

- •1.5. Логічні мікрооперації в регістрах

- •1.6. Мікрооперації зсуву

- •1.7. Перетворення послідовного коду в паралельний і навпаки

- •2. Проектування структурної пристрою

- •3. Проектування функціональної схеми пристрою

- •5. Моделювання спроектованої схеми в пакеті multisim

- •6 .Розробка друкованої плати, 3d-моделі та збірного креслення

- •Висновки

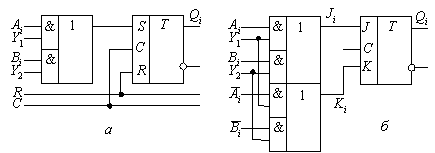

1.3. Записування інформації від двох джерел

Для записування інформації від декількох джерел (напрямків) на вході кожного тригера ставлять додаткові комбінаційні схеми, які створюють вхідну логіку регістра. Кожний напрямок має свою сукупність електричних ліній (шину), по яких передаються сигнали, що відображають значення розрядів слова. Якщо n-розрядне слово передається однофазним кодом, то шина має n ліній зв'язку, а якщо парафазним кодом – то 2n ліній. Записування кожного слова ініціюється відповідним керуючим сигналом Y1, Y2 та ін.

Для

записування в регістр на RS-тригерах

однофазним кодом слів А і В потрібно

реалізувати такі порозрядні функції

збудження входу Si:

Si

= Y1АіÚ

Y2Ві

, (1.1)де Аі і Ві

– двійкові розряди слів А і В; Y1

і Y2

– сигнали керування приймання слів А

і В відповідно. Схема

вхідної логіки і-го розряду регістра

на основі рівняння (1.1)

показана на рис.4.4, а.

Для записування

в регістр на JK-тригерах парафазним кодом

слів А і В потрібно реалізувати такі

порозрядні функції збудження входів

Ji i Ki:

Ji = Y1АіÚ Y2Ві ; Кi = Y1 ![]() Ú

Y2

Ú

Y2![]() (1.2)

(1.2)

Схема вхідної логіки і-го розряду регістра на основі рівнянь (1.2) показана на рис.1.4, б.

Рис.

1.4

Схеми розряду регістра із записом слів

від двох джерел: а – однофазним кодом;

б – парафазним кодом

Рис.

1.4

Схеми розряду регістра із записом слів

від двох джерел: а – однофазним кодом;

б – парафазним кодом

1.4. Зчитування інформації

Інформація,

яка зберігається в регістрах, може

передаватися у зовнішні схеми однофазним

або парафазним способом у прямому або

оберненому коді. Для реалізації

мікрооперацій зчитування до виходів

кожного тригера підключаються комбінаційні

схеми, які створюють вихідну логіку

регістра.

Схеми вихідної логіки

будуються на основі таких порозрядних

логічних рівнянь:

для

зчитування однофазним прямим або

оберненим кодом

Ші = YпрQі Ú

Yоб![]() ;

( 1.3)

для

зчитування парафазним прямим або

оберненим

кодом:

Шi*

= YпрQі Ú Yпр

;

( 1.3)

для

зчитування парафазним прямим або

оберненим

кодом:

Шi*

= YпрQі Ú Yпр![]() ;

; ![]() =

Yоб

=

Yоб ![]() Ú

YобQі ; (1.4)

де

Yпр і Yоб – керуючі сигнали видачі

відповідно прямого або оберненого коду;

Qі і

Ú

YобQі ; (1.4)

де

Yпр і Yоб – керуючі сигнали видачі

відповідно прямого або оберненого коду;

Qі і ![]() –

пряме та інверсне значення

виходу і-го розряду регістра;

Ші – розряд однофазної шини даних;

Шi* і

–

пряме та інверсне значення

виходу і-го розряду регістра;

Ші – розряд однофазної шини даних;

Шi* і ![]() –

розряди парафазної шини даних.

–

розряди парафазної шини даних.

Очевидно,

що керуючі сигнали Yпр і Yоб не повинні

збігатися в часі. Наприклад, при зчитуванні

інформації парафазним оберненим кодом

отримаємо:

Yпр = 0; Yоб = 1; Шi* =![]() ;

; ![]() =

Qі.

=

Qі.

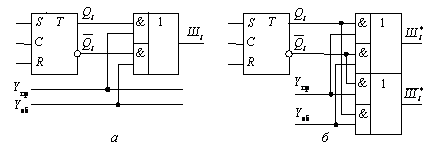

Схеми вихідної логіки для і-го розряду на основі рівнянь (4.3) і (4.4) показані на рис. 1.5.

Рис.

4.5 Схеми вихідної логіки і-го розряду

регістра для зчитування інформації: а

– однофазним кодом; б – парафазним

кодом

Рис.

4.5 Схеми вихідної логіки і-го розряду

регістра для зчитування інформації: а

– однофазним кодом; б – парафазним

кодом

1.5. Логічні мікрооперації в регістрах

У

регістрах можуть виконуватися такі

порозрядні (без перенесень) логічні

мікрооперації над словами А і В: логічне

додавання і множення: RG1:=AÚB;

RG1:=

AÙB;

додавання за модулем два і його

заперечення: RG1:=A![]() B;

RG1:=

B;

RG1:=![]() ;

інверсія слова: RG1:=

;

інверсія слова: RG1:=![]() .

Логічні

мікрооперації передбачають наявність

першого слова А в регістрі. З урахуванням

цього логічне додавання слів А і В

в регістрі на RS- або JK-тригерах з однофазним

записом виконується введенням слів В

без попереднього скидання. Логічне

множення реалізується подаванням

інверсних значень розрядів слова В на

входи R (або K) тригерів регістра.

Дійсно, якщо значення Вi=0, то

.

Логічні

мікрооперації передбачають наявність

першого слова А в регістрі. З урахуванням

цього логічне додавання слів А і В

в регістрі на RS- або JK-тригерах з однофазним

записом виконується введенням слів В

без попереднього скидання. Логічне

множення реалізується подаванням

інверсних значень розрядів слова В на

входи R (або K) тригерів регістра.

Дійсно, якщо значення Вi=0, то ![]() =1

і відповідно тригери обнуляються,

що і потрібно для порозрядного логічного

множення.

=1

і відповідно тригери обнуляються,

що і потрібно для порозрядного логічного

множення.

Мікрооперації

додавання за модулем два і його заперечення

реалізуються в регістрах на Т-тригерах.

Спочатку записується слово А, а потім

без попереднього скидання по лічильному

входу вводиться слово В. Після цього на

прямих виходах тригерів фіксується

результат операції Q=A Å B, а на інверсних

виходах – ![]() =

=![]() Мікрооперація

інвертування складається з подавання

імпульсу на всі Т-входи тригерів регістра,

в яких зберігається слово А. У підсумку

на прямих виходах тригерів встановлюється

результат згідно із співвідношенням

Qi=Ai Å 1=

Мікрооперація

інвертування складається з подавання

імпульсу на всі Т-входи тригерів регістра,

в яких зберігається слово А. У підсумку

на прямих виходах тригерів встановлюється

результат згідно із співвідношенням

Qi=Ai Å 1=![]()