- •Автоколебательный мультивибратор на транзисторах

- •Мультивибратор в режиме ожидания

- •Транзисторные триггеры

- •Тригер Шмитта на транзисторах

- •Компаратор

- •Особенности Операционных усилителей

- •Генератор прямоугольных импульсов на операционном усилителе

- •Логические операции. Функционально-полная группа логических элементов

- •Транзисторно-транзисторные элементы.

- •Логические схемы на комплиментарных мдп-транзисторах (кмдп-транзисторах).

- •Асинхронный триггер на логических элементах

- •Одноступенчатый синхронный

- •Счётчики импульсов

- •Регистры

- •Дешифраторы и шифраторы

- •Mультиплексор и Демультиплексор

- •Устройство

- •Обобщённая схема мультиплексора

- •Цифро-аналоговые преобразователи

- •Аналого-цифровые преобразователи

Логические схемы на комплиментарных мдп-транзисторах (кмдп-транзисторах).

Принципиальная схема инвертора на комплиментарных МДП-транзисторах приведена на рис. 3.17, а стоковые вольт-амперные характеристики — на рис. 3.18. Если Uвх меньше порогового напряжения U01 транзистора VT1, то транзистор VT1 закрыт, а VT2 открыт. Выходное напряжение практически равно

Рис. 3.17. Инвертор на комплиментарных МДП-транзисторах

напряжению питания Е (рис. 3.18, а)

U1 = E - I ут1 rк2 E вых ут к

где Iут1 — ток утечки между стоком и истоком закрытого транзисто-

ра VT1 (Iут 1 нА); rк2 — сопротивление канала открытого транзисто-

ра VT2 (rк2 1 кОм).

При Uвх выше порогового напряжения U01 транзистор VT1 от-

крывается, а VT2 закрывается. Выходное напряжение при Uвх ≈ E

уменьшается практически до нуля (рис. 3.18, б):

U0вых = Iут2rк1 0.

В обоих состояниях ключа, представленных на рис. 3.18, мощность в статистическом режиме практически не потребляется, так как один из транзисторов всегда закрыт, и ток, потребляемый от источника питания, определяется током утечки закрытого ключа. Малая потребляемая мощность — главное достоинство схем на КМДП-транзисторах. Это справедливо, однако, лишь для рассмотренного здесь статистического режима при низких частотах переключения. В общем случае (включающем и статику, и динамику) мощность Рпот , потребляемая ключом от источника питания Е, состоит из трех слагаемых:

Рпот = Ремк + Рскв + Рут ,

где Ремк = СвыхE2 fп — мощность, расходуемая на перезаряд выход-

ной схемы Свых , определяемой выражением (3.5); fп — частота пере-

ключений схемы; Рскв = IсквEtф fп — мощность, определяемая сквозным

током Iскв , который протекает в те моменты времени, когда при переходе схемы из одного состояния в другое открыты оба транзистора (один уже открылся, а второй еще не закрылся); tф — длительность фронта переключающего импульса; Рут = IутE — мощность, потребляемая в статистическом режиме. При малых частотах переключения, схемы на КМДП-транзисторах потребляют очень малую мощность. Однако при больших

частотах переключения (fп > 1 МГц) эти схемы не имеют преимуществ по сравнению с ТТЛ-схемами. Двухвходовые логические элементы ИЛИ—НЕ и И—НЕ представлены на рис. 3.19. Общие правила построения логических элементов на КМДП-транзисторах:

• параллельному соединению одного типа транзисторов соответствует последовательное соединение транзисторов другого типа;

• выполняемая логическая функция определяется включением транзисторов нижнего этажа;

• полярность источника питания Е зависит от типа канала транзисторов нижнего этажа.

Напряжение питания выбирают из условия Е > U0n + U0p , где

U0n — пороговое напряжение n-канального транзистора;

U0p —пороговое напряжение р-канального транзистора.

Время переключения логических элементов на КМДП-транзисторах определяется временем перезаряда выходной емкости Свых .

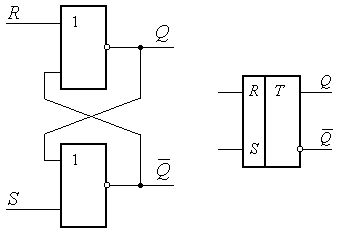

Асинхронный триггер на логических элементах

Асинхронный RS-триггер. На выходе элемента И—НЕ (ИЛИ—НЕ) имеется инвертор (усилитель). Поэтому на двух таких элементах можно выполнить триггер, если вход одного элемента соединить с выходом другого. Полученный таким образом триггер является асинхронным RS-триггером. Он имеет два входа: S — установки триггера в 1 и R — установки триггера в 0. Асинхронный

RS-триггер — простейший интегральный триггер, применяющийся самостоятельно, а также входящий в состав более сложных интегральных триггеров в качестве запоминающей ячейки.

RS-триггер на элементах ИЛИ—НЕ. Рассмотрим воздействие на такой триггер (рис. 3.32, а) комбинаций сигналов S = 1, R = 1 и S = 0, R = 0.

Сочетание S = 1, R = 1 является запрещенным, так как при нем на обоих выходах триггера устанавливаются логические 0 и после снятия входных сигналов состояние его непредсказуемо. Для элемента ИЛИ—НЕ логический 0 — это пассивный сигнал: с поступлением его на вход состояние выхода элемента не изменяется. Поэтому появление комбинации S = 0, R = 0 не изменяет состояние триггера.

Логическая 1 для элемента ИЛИ—НЕ является активным сигналом: наличие ее на входе однозначно определяет на выходе логический 0 вне зависимости от сигнала на другом входе. Отсюда следует: переключающим сигналом для рассматриваемого триггера является логическая 1, а также то, что вход S (установка триггера в состояние Q = 1) должен быть связан с элементом, выход которого принят за Q. Из всего сказанного следует: что для переключения триггера в состояние Q = 1 на его входы следует подать комбинацию S = 1, R = 0, а для переключения в состояние Q = 0 — комбинацию S = 0, R = 1. Пусть триггер находится в состоянии 0 (Q = 0, Q = 1), а на входах действуют сигналы S = 0, R = 0. Для его переключения в состояние Q = 1 подадим на входы комбинацию S = 1, R = 0. Тогда на выходе элемента Э2 установится логический 0, на входах элемента Э1 будут одновременно действовать логические 0 и на выходе Q установится логическая 1 — триггер переключается в новое состояние (Q = 1, Q = 0). Для его переключения из этого состояния на входы должна поступить комбинация S = 0, R = 1. После этого на выходе Q будет логический 0, на входах элемента Э2 одновременно окажутся логические 0 и его выход примет потенциал, соответствующий Q = 1, — триггер переключается в состояние Q = 0, Q = 1 (рис. 3.33). Из изложенного следует: время переключения триггера (tпер) равно удвоенному времени переключения логического элемента (удвоенному времени задержки 2tз . Часто, предусматривая запас, принимают tпер = 3tз . Для надежного переключения триггера длительность входного переключающего сигнала не должна быть меньше tпер. Условное изображение асинхронного RS-триггера со статическими входами приведено на рис. На входы элементов триггера поступают четыре сигнала: S, R, Qt и Qt , где Qt и Q t характеризуют исходное состояние триггера (до смены сигналов на входах S и R). Три из них (S, R, Qt) являются независимыми переменными. Ими определяется новое состояние триггера (Qt + 1), в которое он переключается вслед за сменой сигналов на входах S и R. R-S-триггер на элементах И—НЕ. Для элемента И—НЕ активным сигналом является логический 0: наличие его хотя бы на одном входе обусловливает на выходе логическую 1 вне зависимости от сигналов на других входах. Логическая 1 для такого элемента является пассивным сигналом. С ее поступлением на вход состояние выхода элемента не изменяется. В силу сказанного, триггер на элементах И—НЕ (рис. 3.34) переключается логическим 0. На условном изображении такого триггера это отражают инверсными входами. Для данного триггера комбинация входных сигналов S = 0, R = 0 является запрещенной, а комбинация S = 1, R = 1 не меняет его предыдущего состояния.

Синхронный триггер на универсальных логических элементов

Синхронный RSС-триггер.

На входы логического элемента или устройства сигналы не всегда поступают одновременно, так как перед этим могут проходить через разное число узлов, не обладающих к тому же одинаковой задержкой. Это явление называют состязаниями (или гонками). В результате его в течение некоторого времени на входах создастся непредвиденная ситуация: новые значения одних сигналов сочетаются с предыдущими значениями других, что может привести к ложному срабатыванию элемента (устройства).

Последствия гонок можно устранить временным стробированием, когда на элемент кроме информационных сигналов подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы заведомо успевают установиться на входах.