- •Автоколебательный мультивибратор на транзисторах

- •Мультивибратор в режиме ожидания

- •Транзисторные триггеры

- •Тригер Шмитта на транзисторах

- •Компаратор

- •Особенности Операционных усилителей

- •Генератор прямоугольных импульсов на операционном усилителе

- •Логические операции. Функционально-полная группа логических элементов

- •Транзисторно-транзисторные элементы.

- •Логические схемы на комплиментарных мдп-транзисторах (кмдп-транзисторах).

- •Асинхронный триггер на логических элементах

- •Одноступенчатый синхронный

- •Счётчики импульсов

- •Регистры

- •Дешифраторы и шифраторы

- •Mультиплексор и Демультиплексор

- •Устройство

- •Обобщённая схема мультиплексора

- •Цифро-аналоговые преобразователи

- •Аналого-цифровые преобразователи

Транзисторно-транзисторные элементы.

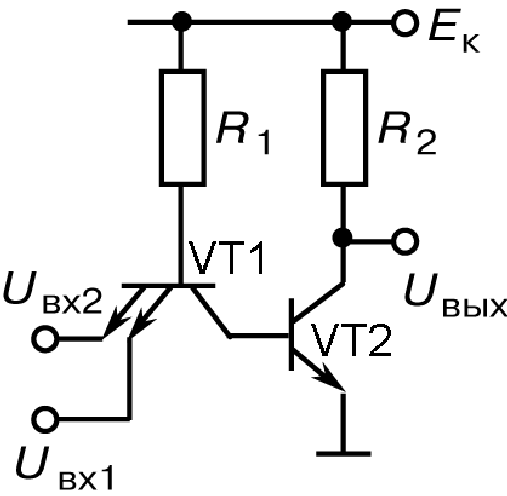

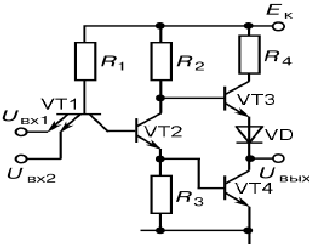

Простейший базовый элемент транзисторно-транзисторной логики (рис. 3.13) в принципе повторяет структуру микросхем ДТЛ-типа. В то же время за счет использования многоэмиттерного транзистора, объединяющего свойства диода и транзисторного усилителя, эта схема позволяет увеличить быстродействие, улучшить технологию изготовления. Базовый элемент ТТЛ так же, как и элемент ДТЛ, выполняет логическую операцию И—НЕ. При низком уровне сигнала (логический нуль) хотя бы на одном из входов многоэмиттерного транзистора VT1 последний находится в состоянии насыщения, а транзистор VT2 закрыт. На выходе схемы существует высокий уровень напряжения (логическая единица). При высоком уровне сигнала на всех входах многоэмиттерный транзистор VT1 работает в активном инверсном режиме, а транзистор VT2 находится в состоянии насыщения. Описанный элемент ТТЛ-логики несмотря на упрощенную технологию изготовления не нашел широкого применения из-за низкой помехоустойчивости, малой нагрузочной способности и малого быстродействия при работе на емкостную нагрузку. Его целесообразно использовать лишь при разработке микросхем с открытым коллектором для реализации функции «монтажное ИЛИ», а также для включения элементов индикации, когда не требуется высокая помехоустойчивость и большая нагрузочная способность. Дополнительными компонентами в схеме базового элемента ТТЛ (рис. 3.14) по сравнению со схемой на рис. 3.13 являются транзисторы VT3 и VT4, образующие сложный инвертор. Диод VD повышает порог отпирания транзистора VT3, обеспечивая его закрытое состояние при открытом и насыщенном транзисторе VT4. Использование сложного инвертора повышает помехоустойчивость и нагрузочную способность схемы. Базовый элемент (рис. 3.14) —основной при разработке современных микросхем ТТЛ-логики.

Рис.3.13. ТТЛ с простым Рис. 3.14. ТТЛ со сложным инвертором

Логические схемы на однотипных МДП-транзисторах. В этих схемах используется только один тип транзисторов — либо р-канальные, либо п-канальные. Более широкое применение находят п-канальные МДП-транзисторы, обеспечивающие большее быстродействие. Типовые схемы элементов ИЛИ—НЕ и И—НЕ на п-канальных МДП-транзисторах приведены на рис. 3.16, а, б. Транзисторы VT1 и VT2 — активные (управляющие), транзистор VT3 — нагрузочный. При низком уровне напряжения на затворах активных транзисторов VT1 и VT2 (Uвх < U0, где U0 — пороговое напряжение) эти транзисторы будут закрыты и ток стока равен нулю. На выходе устанавливается высокий потенциал U1вх = Е – U0 — уровень логической единицы. При входном напряжении на затворах транзисторов VT1 или VT2 больше порогового напряжения U0 соответствующий транзистор отпирается и начинает протекать ток стока. Дальнейшее увеличение Uвх приводит к уменьшению напряжения Uвых. Для получения малого значения уровня логического нуля необходимо, чтобы сопротивление канала открытого транзистора VT1 (или VT2) было гораздо меньше сопротивления канала транзистора VT3.