ЛЕКЦИЯ ВТОРАЯ

Общие сведения о дискретных устройствах и программируемых логических матрицах

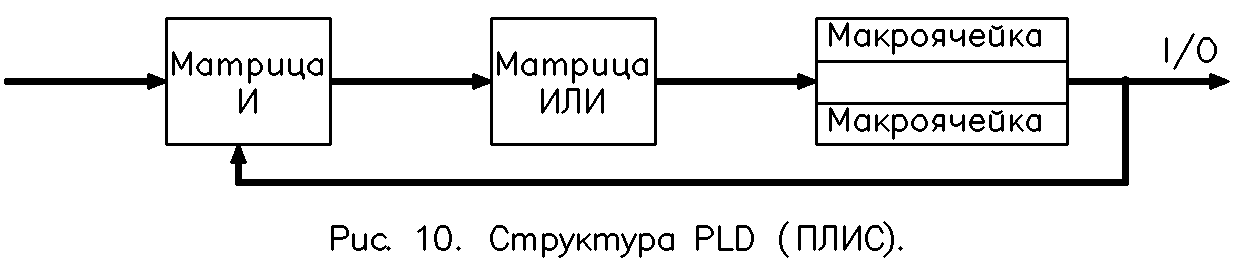

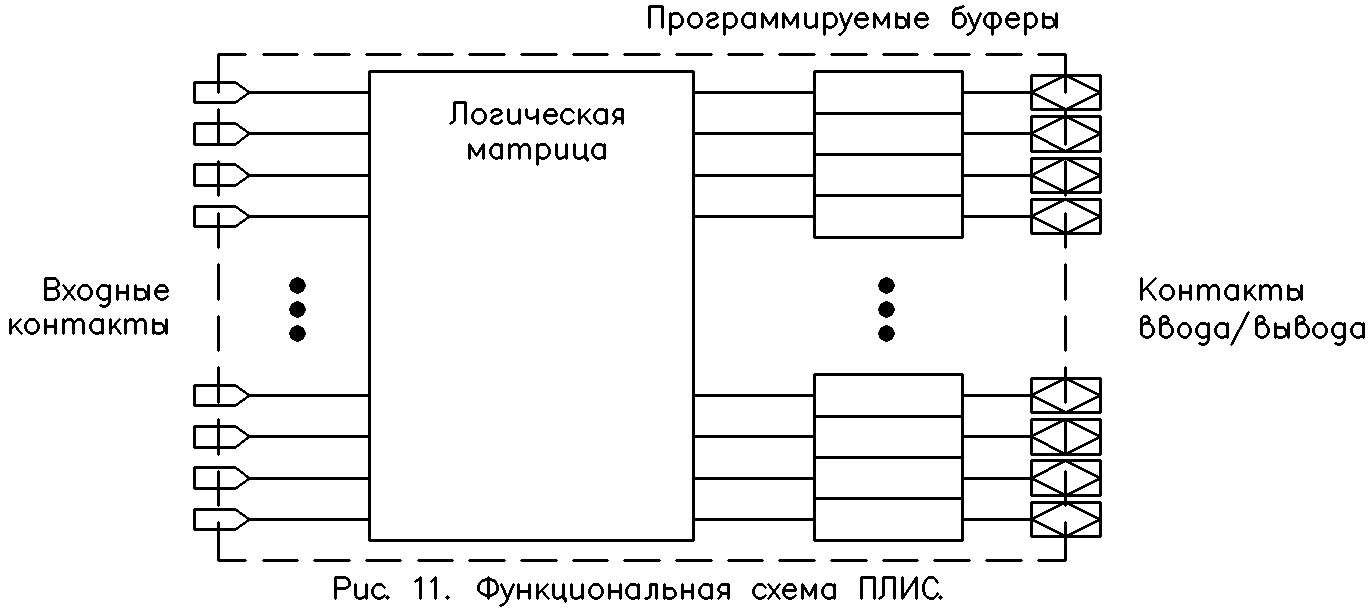

1. Общие сведения о pld

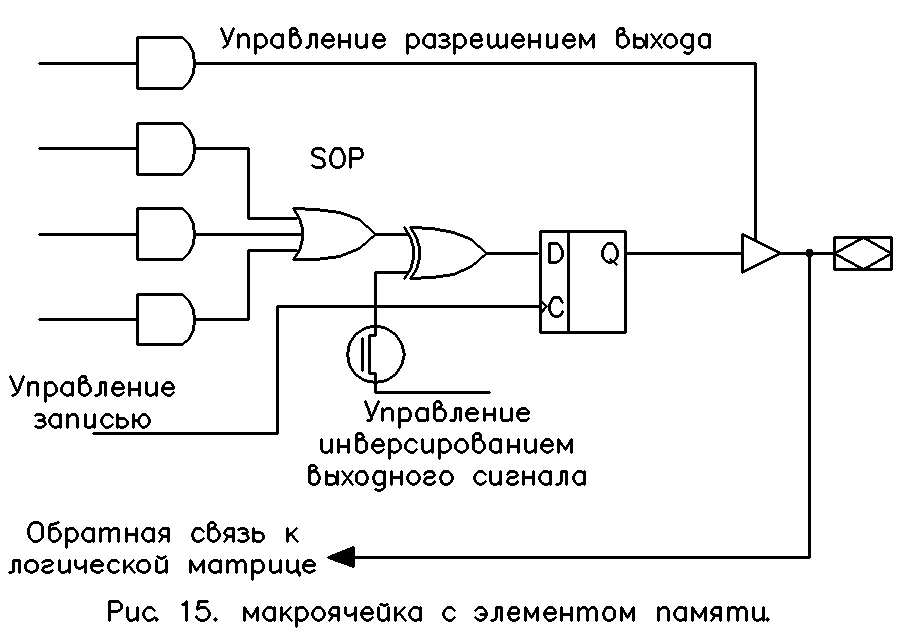

Несколько p-термов могут объединяться схемой “ИЛИ”, расположенной на входе так называемых XOR - элементов, которые при изменении управляющих сигналов и в соответствии с заложенными в них при программировании свойствами меняют вид выходной информации, направление передачи информации через двунаправленный вывод и т.д. Эта логическая сумма р-термов часто обозначается аббревиатурой SOP (Sum of Products). Как правило выход SOP связан с выходом макроячейки через схему “Исключающее ИЛИ” (рис.13) используемую для программного управления инверсией выходного сигнала, и снабженный фиксированным комбинаторным буфером, использующимся только для вывода информации. Очевидно, что при подаче на второй вход элемента “Исключающее ИЛИ” низкого логического уровня информация выводится из ПЛИС в прямом коде, а при соединении его с задатчиком уровня логической единицы - в инверсном. Для минимизации необходимого числа выводов микросхемы выходной сигнал SOP использует тот же внешний контакт, что и вход, использующий внутренние цепи связи с логической матрицей в виде обратной связи.

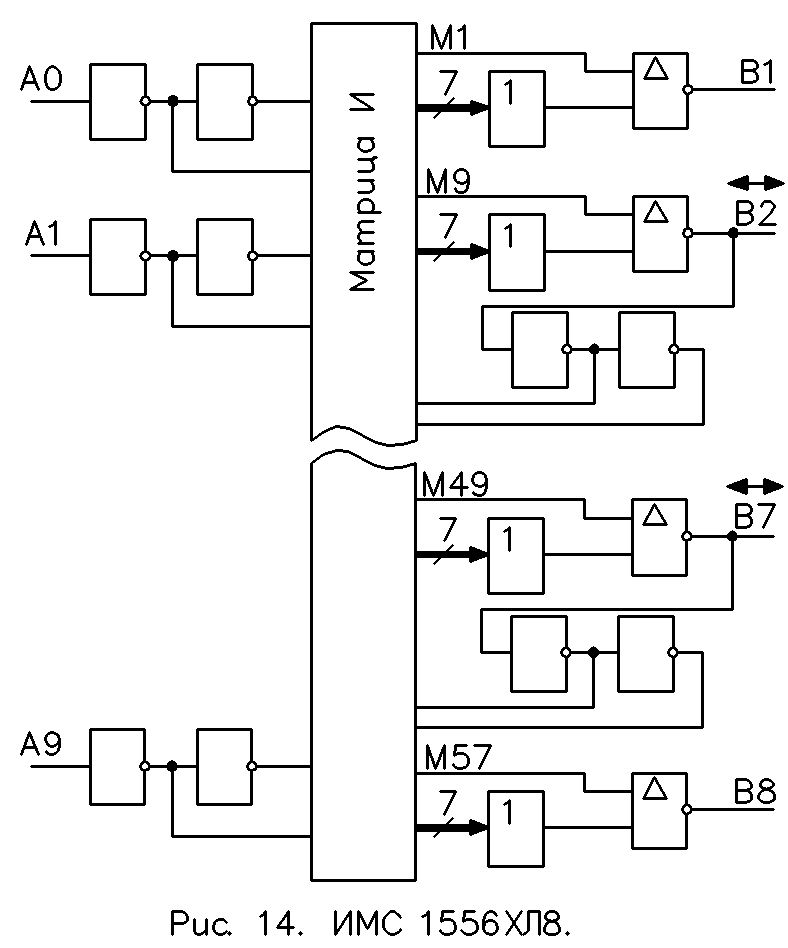

Выходные сигналы, появляющиеся на выходных шинах 64 элементов матрицы “И”, вводятся в матрицу “ИЛИ”, образующую второй логический уровень и реализующую дизъюнкции заданных конъюнкций. Матрицу “ИЛИ” образуют восемь дизъюнкторов, каждый из которых может быть связан с одной из восьми групп конъюнкторов (по семь конъюнкторов в группе).

Выходной каскад, включающий восемь выходных усилителей с тремя состояниями, предназначен для вывода информации. Выборка выходных усилителей осуществляется непосредственно из матрицы “И”, т.е. адресным путем, в зависимости от комбинаций сигналов на входах ПЛИС и уравнений, реализуемых логической матрицей. Возможны следующие режимы работы микросхемы: хранение, считывание, программирование и контроль матрицы “И”.

Режим хранения осуществляется установкой выводов микросхемы в закрытое (высокоимпедансное) состояние путем подачи на выводы определенных адресных воздействий, приводящих к появлению на выходах первого, девятого, ..., или пятдесят седьмого элементов “И” низкого логического уровня.

Разрешение выборки выходных каскадов в этой микросхеме осуществляется непосредственно из матрицы. Пережигание всех перемычек в управляющей строке соответствует переводу выходного каскада в режим считывания независимо от подаваемого адреса. Двунаправленные выводы микросхемы могут быть использованы как входы, если установить выходной каскад в третье (высокоимпедансное) состояние.

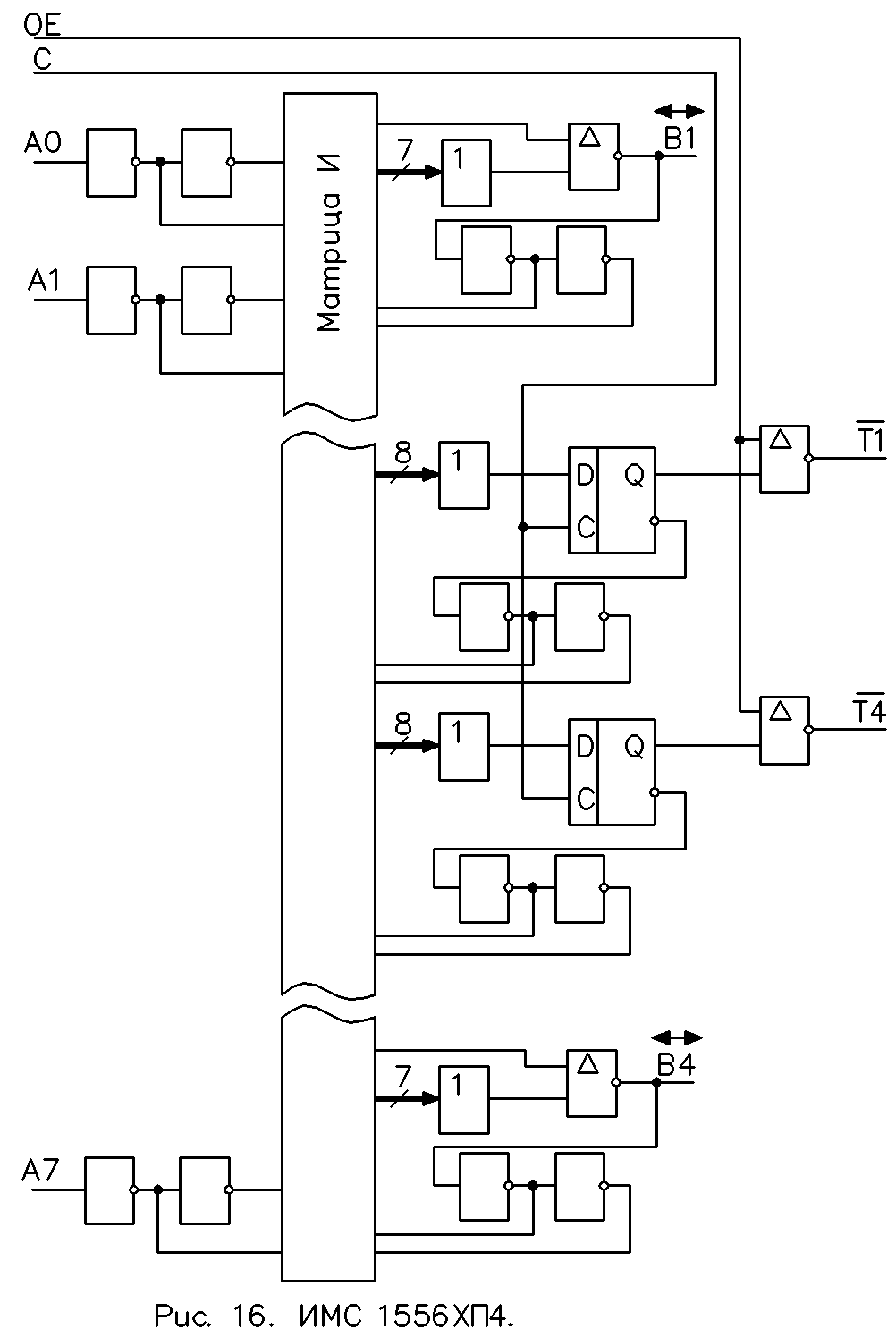

Примером отечественной интегральной микросхемы, имеющей триггеры в составе выходной макроячейки, может служить КР1556ХП4 (рис.16).

Первый уровень ее логики образуют конъюнкции входных переменных А0...А7; второй - матрица “ИЛИ”, состоящая из восьми дизъюнкторов (четырех 7-входовых и четырех 8-входовых).

Выходной каскад КР1556ХП4 включает четыре выходных усилителя с тремя состояниями, предназначенных для ввода-вывода информации (аналогично КР1556ХЛ8), и четыре D - триггера, синхронизируемых фронтом внешнего сигнала С, причем выходы триггеров подключены к матрице “И” и контактам микросхем через трехстабильные буферы, управляемые внешним сигналом ОЕ.

Микросхемы КР1556ХП6 и КР1556ХП8 отличаются числом триггерных и комбинационных выводов: первая из них имеет шесть комбинационных и два триггерных вывода, а вторая - восемь триггерных выводов.

Следующим шагом разработки PLD было создание микросхем, имеющих в каждой макроячейке в место D-триггера программируемый регистр, который мог быть сконфигурирован на выполнение функций D, T, JK и SR триггеров, причем каждый из них мог быть запрограммирован индивидуально для каждой макроячейки.

Гибкость и возможность программирования PLD позволяют производить разработку приборов на их базе гораздо быстрее, чем на базе дискретной логики. Возможность настройки универсальной PLD для специфического применения позволяет с помощью нескольких PLD общего назначения осуществлять функции, для реализации которых потребовались бы сотни микросхем. Использование СБИС PLD позволяет резко снизить затраты на производство, к тому же, занимает меньше пространства на печатных платах, нежели дискретные устройства, так как в каждый PLD - прибор можно занести больше логических функций, чем реализовать с помощью дискретного элемента.