Книги / ЭВТ-3-Конспект лекций по ДУ-Шарыбин / METOD4_97

.doc

ЛЕКЦИЯ ЧЕТВЕРТАЯ

Устройства MAX 9000 и FLASHlogic

1. MAX(Multiple Array matriX ) 9000

Семейство МАХ 9000 это внутри программируемые, высокоэффективные EPLD с высокой плотностью элементов, основанные на третьем поколении архитектуры МАХ фирмы Altera. Изготовленный с помощью продвинутой технологии КМОП-структуры, ЭППЗУ-основанное семейство МАХ 9000 содержит от 6,000 до 12,000 пригодных для использования логических элементов, обеспечивает время прохождения сигнала от вывода к выводу 7.5 нс и частоту счетчика до 178 MHz (таблица 12)

Таблица 12

|

Характеристика |

EPM9320 EPM9320A |

EPM9400 |

EPM9480 EPM9480A |

EPM9560 EPM9560A |

|

Число вентилей |

6000 |

8000 |

10000 |

12000 |

|

Число триггеров |

484 |

580 |

676 |

772 |

|

Число макроячеек |

320 |

400 |

480 |

560 |

|

Число БЛМ |

20 |

25 |

30 |

35 |

|

Максимальное число контактов ввода-выода |

168 |

159 |

175 |

216 |

|

tPD(нс) |

7.5 |

15 |

10 |

10 |

|

fCNT(МГц) |

178 |

118 |

145 |

145 |

Архитектура МАХ 9000 основана на высокоэффективных, гибких модулях логических матриц (рис 41). БЛМ состоят из массивов макроячеек, количество макрояечеек в них не привышает 16. БЛМ связаны через структуру маршрутизации FastTrack Interconnect, которая представляет собой ряд непрерывных горизонтальных и вертикальных каналов тракта, которые пересекают все устройство. Эта структура тракта обеспечивает предсказуемую эффективность даже в сложных проектах. (Рис 42)

Макроячейки МАХ 9000 состоят из трех функциональных блоков: р-термов, матриц выделения р-термов и программируемых регистров (рис 43).

-

Общие р-термы расширения являются инвертированными р-термами. Они подаются обратно в логическую матрицу.

Каждый блок логической матрицы имеет 16 общих р-термов расширения, которые могут рассматриваться как объединение одиночных р-термов (один из каждой макроячейки) с инвертированными выводами, которые подаются обратно в локальный БЛМ массив. Каждый общий р-терм расширения может использоваться, как отдельно так и совместно, любой или всеми макроячейками в БЛМ, для формирования сложных логических функций (Рис. 44).

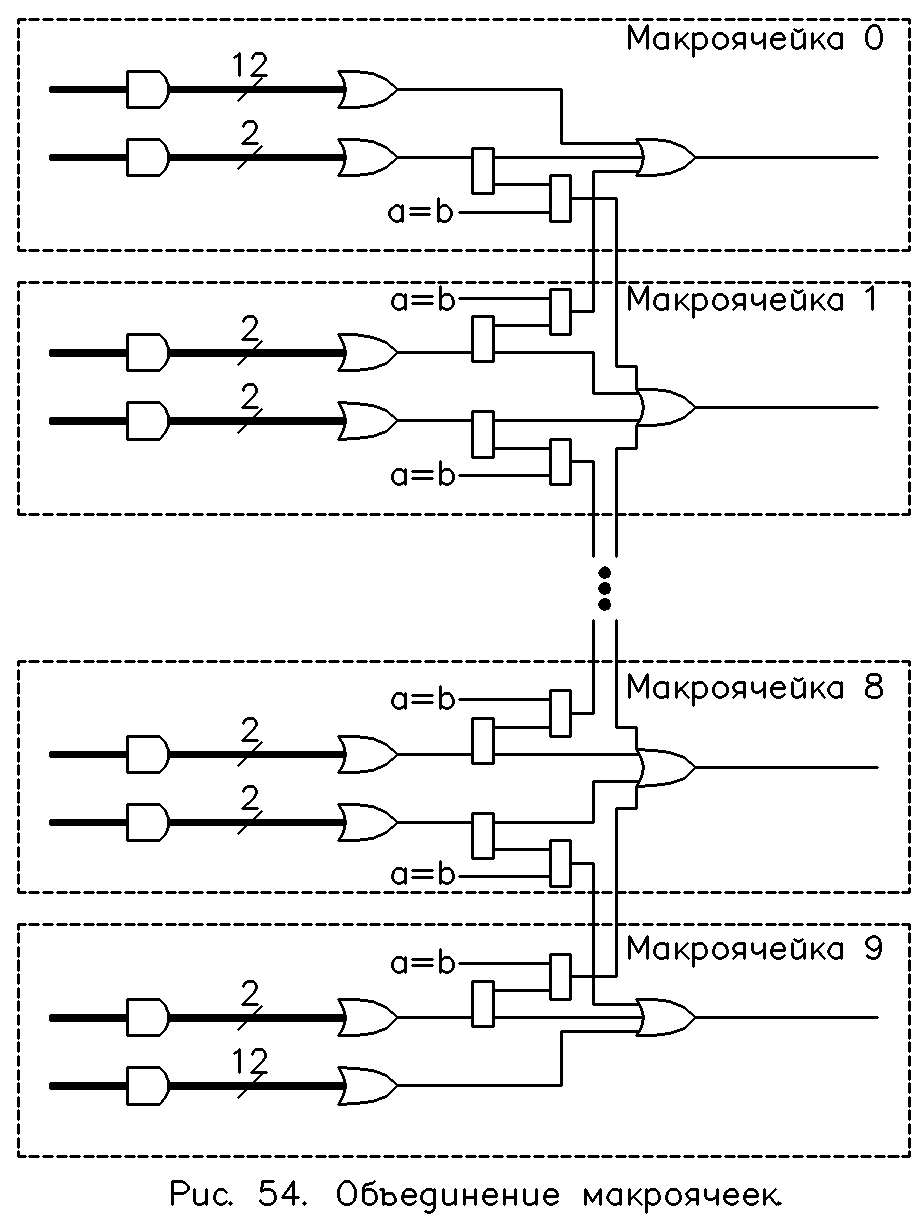

Параллельные р-термы расширения это неиспользуемые р-термы, которые могут быть отданы соседней макроячейке, для более быстрого выполнения сложных логических функций. Параллельные р-термы расширения позволяют увеличить число непосредственно передаваемых р-термов макроячейке "ИЛИ" до 20: 5 р-термов обеспечиваются макроячейкой и 15 параллельных р-термов расширения обеспечиваются соседними макроячейками блока логической матрицы (Рис. 45).

Две группы по 8 макроячеек внутри каждого БЛМ (например, макроячейки с 1 до 8 и с 9 до 16) формируют 2 цепочки для предоставления или заимствования параллельных р-термов расширения. Макроячейка заимствует параллельные расширенные р-термы из ниже пронумерованных макроячеек. Например, макроячейка 8 может заимствовать параллельные расширенные р-термы из макроячейки 7, из макроячеек 7 и 6 или из макроячеек 7, 6 и 5. Внутри каждой группы 8-я, самая низко пронумерованная макроячейка может только предоставлять параллельные р-термы, а макорячейка с наименьшим номером может только занимать их.

Каждый программируемый регистр может быть синхронизирован в тремя различными способами:

-

Любым глобальным сигналом синхронизации. Этот режим требует наименьшее время для появления сигнала на выходе, с момента начала синхронизации.

-

Глобальным сигналом синхронизации и с учётом высокого уровня сигнала разрешения синхронизации.. Этот режим обеспечивает отпирание каждого триггера, при все еще малом времени появления сигнала на выходе, с момента начала синхронизации.

-

Массивом р-термов. В этом режиме, триггер может быть синхронизирован сигналами из скрытых макроячеек или выводов I/O.

Доступны два глобальных сигнала синхронизации (Рис. 46). Эти глобальные сигналы синхронизации могут быть истинными сигналами или дополнениями от любого из выводов глобальной синхронизации (DIN1 и DIN2).

Также каждый регистр поддерживает функции асинхронной предустановки и сброса. Матрица выделения р-термов распределяет р-термы для управления этими операциями (см рис. 43.). Хотя управление предустановкой и сбросом регистров р-термов управляется высоким уровнем, управление при низком уровне может быть получено инвертированием сигнала внутри логической матрицы. Кроме того, каждый регистр с функцией сброса может индивидуально управляться низким уровнем через специальный вывод общей очистки (DIN3). Глобальный сброс может быть запрограммирован для операций при активно-высоком или активно-низком уровне.

БЛМ внутри устройств МАХ 9000 размещены в матрице столбцов и строк. Каждая строка БЛМ имеет специализированную строку межсоединений, которая направляет сигналы в БЛМ и из него в строку. Строка межсоединения затем может управлять выводами I/O или подавать в другие БЛМ. Каждая строка межсоединений имеет общее количество каналов, равное 96 (Рис. 47).

Канал строки межсоединения может быть подан от вывода макроячейки через мультиплексор с 4 входами, который макроячейка использует совместно с тремя столбцами каналов. Если мультиплексор используется для подключения макроячейки к строке, сигналы трех столбцов могут обращаться к другому каналу строки через дополнительный мультиплексор с 3 входами. Внутри любой БЛМ мультиплексоры обеспечивают доступом все 48 канала столбцов к 32 каналам строк .

В каждый БЛМ подается 33 входа из строки межсоединений и 16 сигналов обратной связи из макроячеек внутри БЛМ. Все эти сигналы доступны внутри БЛМ в их истинной и инвертированной форме. Кроме того, 16 общедоступных р-термов расширения доступны в их инвертированной форме, в итоге, общее количество сигналов, которые подаются в БЛМ, равно 114. В каждый БЛМ также подается два синхроимпульса с малым фазовым сдвигом и один сигнал глобального сброса, который может использоваться для управления регистрами во всех 16 макроячейках.

Выводы I/O могут использоваться для ввода, вывода информации или для выполнения двунаправленных операций. Каждая IOC имеет регистр IOC с синхроимпульсами разрешения ввод. Этот регистр может использоваться как входной регистр для внешних данных, которые требуют малого времени установки, или как регистр вывода для данных, быстрого появления сигнала на выходе после начала синхронизации. Разрешающие синхроимпульсы регистра IOC позволяют глобальной синхронизации, быть использованной для быстрого появления сигнала на выходе после начала синхронизации, при поддержании гибкости, требуемой для выборочной синхронизации.

Синхроимпульсы, разрешающие синхроимпульсы, очистка и управление разрешения вывода для IOC обеспечиваются сетью сигналов управления I/O. Эти сигналы могут быть поданы на специализированные входы или сгенерированы внутренней логикой. Пути сигнала управления IOC разработаны так, чтобы минимизировать расфазировку при прохождении сигналов через устройство. Все источники сигналов управления буферизированы на быстродействующие задающие устройства, которые управляют сигналами вокруг периферии устройства. Эта " периферийная шина " может быть сконфигурирована так, чтобы обеспечивать до восьми сигналов разрешения вывода, до четырех сигналов синхронизации, до шести сигналов, разрешающих синхроимпульсов, и до двух чистых сигналов.

Входной сигнал из ячейки I/O может управлять двумя отдельными каналами строки. Когда ячейка I/O используется для вывода, сигнал управляется мультиплексором (10 к 1), который выбирает каналы строки. Каждый конец канала строки подает до восьми IOC на периферию устройства (Рис 49).

В дополнение к универсальным выводам I/O, устройств МАХ 9000 имеют четыре специализированных входа. Эти специализированные входы обеспечивают распределение сигнала с малой расфазировкой к БЛМ и IOC, и обычно используются для глобальной синхронизации, очистки и сигналов разрешения управления выводом. Глобальные сигналы управления могут подаваться макроячейке или синхроимпульсам IOC, очищая входы, также как разрешающий вывод IOC. Специализированные входы могут также использоваться как универсальные входы данных, потому что они могут подаваться строке структуры тракта FastTrack Interconnect (см. Рис. 46.)

Архитектура устройства МАХ 9000 поддерживает свойство интерфейса I/O –“MultiVolt”, которое позволяет устройствам МАХ 9000 связываться с помощью интерфейса с системами, отличающимися напряжениями питания. Устройства с питанием 5.0В во всех корпусах могут быть установлены для операций с выводами I/O при напряжении 3.3В или 5.0В. Эти устройства имеют набор выводов Vсc для внутренней операции и входного буфера (VCCINT), и другой набор для драйверов вывода I/O (VCCIO).Выводы VCCINT должны всегда соединяться с питанием 5.0В. Уровень входного напряжения VССINT 5.0В - в уровнях ТТЛ и следовательно совместим с 5.0В и 3.3В входами.

Устройства МАХ 9000 могут внутренне программироваться через интерфейс JTAG BST с 4 выводами. ISP предлагает быстрые и эффективные итерации в течение разработки проекта и циклов отладки. Архитектура МАХ9000 внутренне генерирует напряжение 12.0В, требуемое для программирования ячеек ЭППЗУ, при этом потребность в внешнем питании 12.0В для программирования устройства на плате отпадает. В течение ISP, выводы I/O находятся в высокоимпедансном состоянии, что устраняет возможные конфликты.

ISP упрощает поток производства, позволяя устройствам быть установленными на печатной плате прежде, чем они программируются. Устройства МАХ 9000 могут программироваться выгружая информацию через внутрисхемные тестеры (ICT), внедренные процессоры, загрузочные кабели Altera BitBlaster или ByteBlaster. Программирование устройств после того, как они помещены в плату, устраняет повреждения на корпусах с большим количеством выводов (например, QFP корпуса), вызванных обработкой устройства. Устройства МАХ 9000 могут также быть перепрограммированы практически в любых условиях (то есть, обновление программы может выполняться с помощью программного обеспечения или модема).

Внутреннее программирование может быть выполнено с адаптивным или постоянным алгоритмом. Адаптивный алгоритм читает информацию из модуля и приспосабливает последующие шаги программирования, так, чтобы достичь самого быстрого времени программирования для этого модуля. Поскольку некоторые ICT платформы имеют трудности обеспечения адаптивного алгоритма, Altera предлагает устройства, проверенные с постоянным алгоритмом. Устройства проверенные постоянным алгоритмом отмечены суффиксом "F" в названии.

2. Семейство FLASHLogic

Семейство FLASHlogic объединяет два вида СБИС, логика которых построена по принципам SRAM-памяти. СБИС этой серии позволяют реализовать логические функции различной степени интеграции, обеспечивают высокую плотность элементов от 1600 до 3200 используемых вентилей, задержку сигнала на элементе 10 нс и частоту синхронизации 80 МГц (таб. №13).

Таблица 13

|

Характеристика |

EXP880 |

EXP8160 |

|

Число вентилей |

1.600 |

3.200 |

|

Максимальное число SRAM-бит |

10.240 |

20.480 |

|

Число макроячеек |

80 |

160 |

|

Число блоков логических матриц |

8 |

16 |

|

Тип корпуса (число контактов общего назначения) |

84 вывода, PLCC (62) 132 вывода, PQFP (104) |

208 выводов, PQFP (172) |

|

tPD, нс |

10 |

10 |

|

tСO, нс |

6 |

6 |

|

tCNT, МГц |

80 |

80 |

В случае настройки в качестве логического блока 24V10, БЛМ состоит из 10 макроячеек, 12-разрядного компаратора, 2-х линий глобальной синхронизации, блока управления внутренней синхронизацией, установкой, сбросом и сигналами разрешения выдачи (ОЕ) (рис. 52).

Макроячейка, как и макроячейки предыдущих серий, состоит из трех блоков: логической матрицы, схема распределения р-термов и программируемого регистра (рис.53).

При выполнении регистровых операции регистр каждой макроячейки может быть независимо от других регистров запрограммирован на режим работы: в качестве D, T, JK или RS триггера, кроме того, он имеет независимые входы синхронизации, установки, сброса. В случае необходимости, регистр может быть отключен (обойден) - в комбинаторном режиме работы.

Каждый регистр может быть синхронизирован тремя способами:

-

Глобальный режим - синхронизация регистра происходит сигналом, снимаемым с любого из двух входов глобальной синхронизации. В этом режиме достигается максимальная производительность - минимальное время между подачей синхроимпульса и информацией на выходе (clock-to-output delay).

-

Глобальный режим с задержкой (delayed global mode) - синхронизация регистра происходит любым из двух глобальных синхросигналов, к которому внутри БЛМ добавлена некоторая задержка.

-

Матричный режим (array mode) - синхронизация регистра происходит любым из двух внутренних синхросигналов матрицы.

Описанные способы синхронизации увеличивают гибкость элементов серии FLASHlogic с точки зрения синхронизации, позволяют разработчику изменять время установки сигнала, время хранения (hold time), время между подачей синхроимпульса и информацией на выходе (clock-to-output delay). Эти способы синхронизации особенно полезны в устройствах, работающих в быстродействующей микропроцессорной системе, например на базе процессора Pentium.

Компаратор сравнивает до 12 пар входов элемента за время tPD. Матрица распределения р-термов позволяет любой из 10 макроячеек использовать выход сигнал с выхода компаратора (рис. 55).

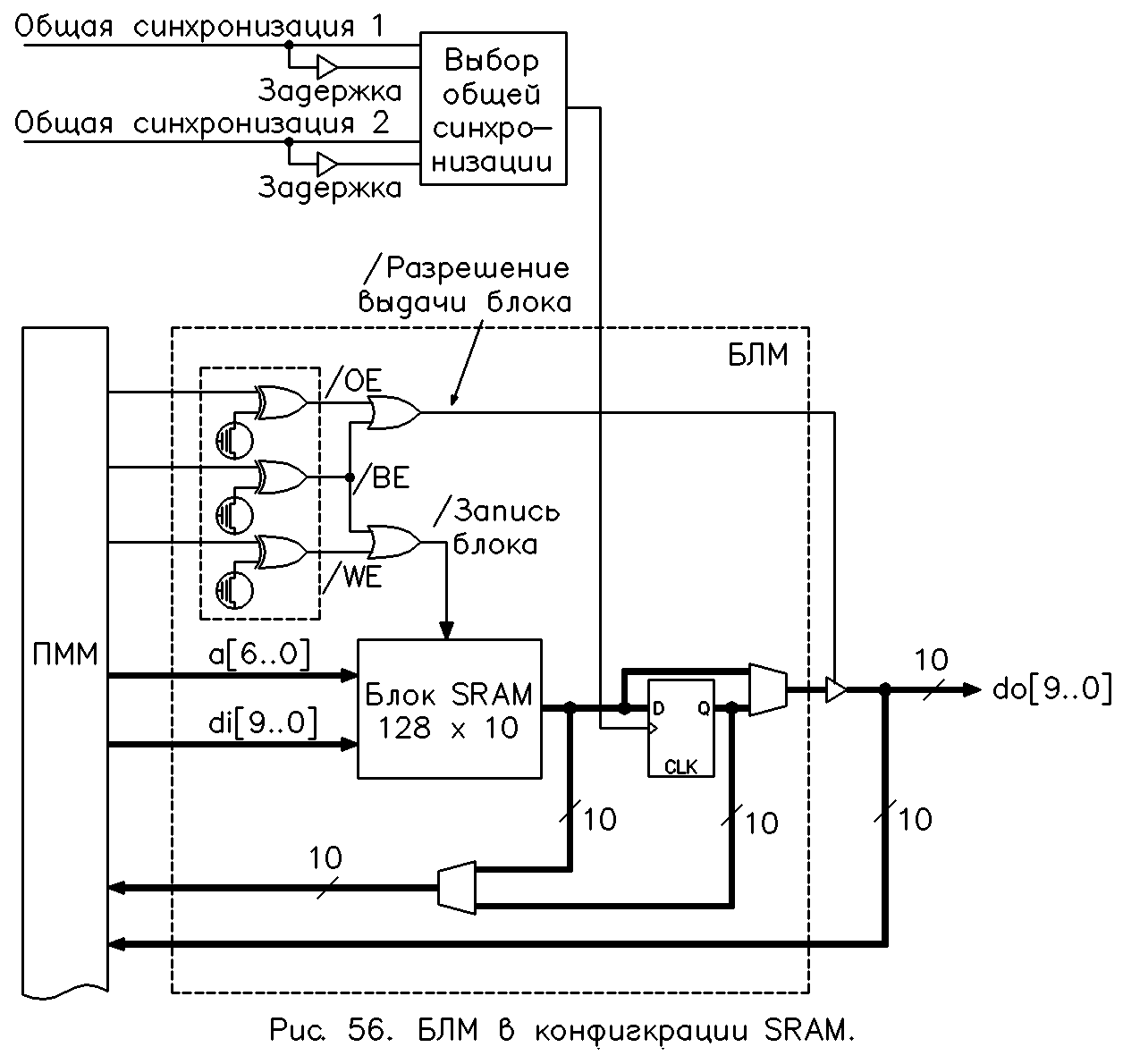

Обращение к SRAM происходит с помощью подмножества 24 сигналов, поступающих с PIA: 7 бит - для адреса; 10 бит - для входных данных; 3 бита - сигналы разрешения операций с блоком (/ВЕ); сигнал разрешения записи (/WE) и сигнал разрешения выдачи (/OE), см. таблицу 14.

Таблица 14. SRAM функции

|

Входы |

Шинный цикл |

Возможность снятия сигнала с контактов ввода-вывода |

||

|

/BE |

/WE |

/OE |

|

|

|

1 |

X |

X |

Нет цикла |

Запрещено |

|

0 |

1 |

1 |

Чтение |

Запрещено |

|

0 |

1 |

0 |

Чтение |

Разрешено |

|

0 |

0 |

1 |

Запись |

Запрещено |

|

0 |

0 |

0 |

Запись |

Разрешено |

Во время подачи питания, происходит инициализация SRAM элементов памяти от энергонезависимых конфигурационных ячеек. Если во время работы в SRAM ячейку не была записана какая-либо информация, то она содержит копию информации, содержащейся в энергонезависимой конфигурационной ячейке. Таким образом, блок SRAM может эмулировать ПЗУ (ROM).

В случае когда БЛМ конфигурирован как SRAM, все р-термы используются как SRAM блоки и не могут быть использованы для реализации логических функций. Несколько БЛМ могут каскадно соединяться между собой, что позволяет увеличить объём SRAM.

Блок управления вводом - выводом позволяет каждой магистрали ввода - вывода быть индивидуально настроенной либо на приём информации (работа в качестве входа) либо выдачу информации (работа в качестве выхода) либо работу в качестве двунаправленной магистрали (ввод-вывод). Все магистрали ввода - вывода имеют в своём составе тристабильный буфер, который независимо от других буферов может управляться: одним из двух сигналов ОЕ, снимаемым с выхода БЛМ, либо может быть непосредственно соединён с входом сигналов GND или VСС (рис. 57).

Архитектура элементов серии FLASHlogic такова, что они содержат две линии обратной связи, благодаря которым макроячейки и контакты обратной связи независимы. Когда контакты ввода-вывода настроены на приём сигнала (работают как входы), связанная с ними макроячейка может быть использована для реализации скрытой логики (buried logic).

Входы прибора точно также как и магистрали ввода -вывода, используемые для приема информации, могут быть оптимизированы с целью уменьшения величины тока в режиме простоя. Для этого при описании устройства на языке PLDasm необходимо использовать ключевые слова CMOS_LEVEL (для 5,0 В КМОП входов) и TTL_LEVEL (для 3,3 В КМОП или ТТЛ входов). Если режим оптимизации не используется, то для всех входов "применяется" ключевое слово TTL_LEVEL.

Выходы элемента FLASHLogic обычно настраиваются таким образом, чтобы учесть ряд системных требований.

-

Работа в режиме 3.3 В и 5 В (3.3-V or 5.0-V Operation)

Выводы в блоке управления вводом-выводом могут выдавать напряжение номиналом 3.3 V или 5.0 V. Эта возможность позволяет проектировщику в проектируемом устройстве смешивать выходы с номиналом выдаваемого напряжения 3,3 В и входы с номиналом 5,0 В в том случае, если на соответствующие контакты Vcco подаётся напряжение номиналом 3,3 В. Для нормальной работы на элементы серии FLASHlogic необходимо подавать напряжение величиной 5,0 В. Однако, контакт Vcco, связанный с каждой парой БЛМ может быть соединен с источником напряжения 5,0 В или 3,3 В, что позволяет управлять выходным напряжениям контактов ввода - вывода соответствующей пары БЛМ. Эта возможность позволяет использовать элементы серии FLASHLogic в системах со смешанным питанием. Например, рассматриваемые элементы могут использоваться как интерфейсная прослойка между 3,3 В центральным процессором и 5-и В периферийной логикой.

Более мощный блок питания требуется в том случае, когда все БЛМ функционируют на уровне 3,3 В.

-

Работа в режиме “открытого” стока

Выходы элементов серии FLASHlogic могут быть переключены, каждый по отдельности, на работу в режиме открытого стока (этот режим эквивалентен режиму открытого коллектора). В случае необходимости логические функции могут быть реализованы с использованием множества выводов с открытым стоком, что эквивалентно использованию дополнительной матрицы ИЛИ.