- •Структурная схема 8-ми разрядного мп

- •Алгоритм работы управляющего автомата

- •Форматы команд

- •Способы адресации

- •Команды пересылки (команды передачи данных) Арифметические и логические команды

- •Команды сдвига (сдвига в аккумуляторе)

- •Команды передачи управления

- •Спецкоманды

- •Псевдокоманды

- •Запоминающие устройства

- •1. Регистровый способ адресации с одним регистром Rd

- •Сторожевые таймеры

- •Организация таймеров/счетчиков.

1. Регистровый способ адресации с одним регистром Rd

Данные, над которыми осуществляется операция (или используются при выполнении операции), находятся в регистре d (Rd).

Прямая регистровая адресация с двумя регистрами — Rd и Rr

Данные, над которыми осуществляется операция, находятся в регистрах г (Rr) и d (Rd). Результат операции сохраняется в регистре d (Rd).

INC

RD ADD

RD

Rr

INC

RD ADD

RD

Rr

2.непосредственная адресация к области ввода/вывода

OUT P,RR

n — адрес регистра, используемого в операции, находится непосредственно в коде команды, в битах 0...5.

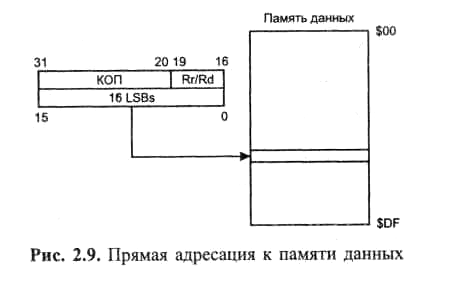

3.Прямая адресация к памяти данных

1 6-разрядный

адрес ячейки памяти данных находится

в кодекоманды,

состоящей из двух слов. Rr/Rd

определяет регистр, используемый

при работе с памятью данных (т. е. регистр,

куда записываются

результаты операции либо откуда они

берутся для выполнения операции).

6-разрядный

адрес ячейки памяти данных находится

в кодекоманды,

состоящей из двух слов. Rr/Rd

определяет регистр, используемый

при работе с памятью данных (т. е. регистр,

куда записываются

результаты операции либо откуда они

берутся для выполнения операции).

4.Косвенная адресация к памяти данных со смещением

Адрес операнда определяется как сумма содержимого Z или Y регистра и бит 0...5 кода команды.

STD Y+q,RR

[RR]->M( [Y+q])

5.Косвенная адресация к памяти данных без смещения

Адрес операнда находится в Х-, Y- или Z-регистре.

ST Х,RR

[RR]->M([Х])

6.Косвенная

адресация к памяти данных с предварительным

декрементом

6.Косвенная

адресация к памяти данных с предварительным

декрементом

Адрес операнда находится в Х-, Y- или Z-регистре. Однако перед выполнением операции соответствующий индексный регистр Х-, Y-или Z уменьшается на единицу.

ST – Х,RR

[Х] -1 -> Х

[RR] ->M([Х])

7.Косвенная адресация к памяти данных с постинкрементом

ST Х+,RR

8.Адресация с использованием команд LPM и ELPM

Адрес константы — байта содержится в регистре Z. 15 старших битов определяют адрес слова, а младший (0) бит — младший или старший байт константы в памяти программ. Если в младшем бите 0 — выбран младший байт, 1 — старший байт.

ELPM

(M[Z]) ->RO

9.Косвенная адресация памяти программ IJMP и ICALL

П осле

операций IJMP или ICALL выполнение программы

продолжается с адреса, записанного

в Z-регистре (т. е. в PC счетчик команд

микроконтроллера записывается содержимое

Z-регистра).

осле

операций IJMP или ICALL выполнение программы

продолжается с адреса, записанного

в Z-регистре (т. е. в PC счетчик команд

микроконтроллера записывается содержимое

Z-регистра).

10.Относительная адресация памяти программ

После операций RJMP или RCALL выполнение программы продолжается с адреса PC+k+l. Относительный адрес к может составлять от-2048 до 2047.

PC +k

PC+k+1 ->PC

Система команд AVR

Арифметические и логические команды

|

Мнемоника |

Описание |

Действие |

Флаги |

Циклы |

|

ADD Rd.Rr |

Сложить два регистра |

Rd<Rd+Rr |

Z,C,N,V,H |

1 |

|

ADC Rd.Rr |

Сложить с переносом |

Rd<Rd+Rr+C |

Z,C,N,V,H |

1 |

|

ADIW Rdl.K |

Сложить слово с константой |

Rdh,KRdh,l+K |

Z,C,N,V,S |

2 |

|

SUB Rd.Rr |

Вычесть два регистра |

Rd<Rd-Rr |

Z,C,N,V,H |

1 |

|

SUBI Rd,K |

Вычесть константу |

Rd<Rd-K |

Z,C,N,V,H |

1 |

|

SBIW Rdl.K |

Вычесть слово с константой |

Rdh.KRdh.l-K |

Z,C,N,V,S |

2 |

|

SBC Rd.Rr |

Вычесть с переносом |

Rd<Rd-Rr-C |

Z,C,N,V,H |

1 |

|

SBCI Rd,K |

Вычесть с переносом |

Rd<Rd-K-C |

Z,CSN,V,H |

1 |

|

AND Rd,Rr |

Логическое И |

Rd<RdANDRr |

Z,N,V |

1 |

|

ANDI Rd.K |

Логическое И |

Rd<RdANDK |

Z.N.V |

1 |

|

OR Rd,Rr |

Логическое ИЛИ |

Rd<Rd OR Rr |

Z.N.V |

1 |

|

ORI Rd.K |

Логическое ИЛИ |

Rd<RdORK |

Z.N.V |

1 |

|

EOR Rd.Rr |

Исключающее ИЛИ |

Rd<RdXORRr |

Z,N,V |

1 |

|

COMRd |

Дополнение до 1 |

Rd<$FF-Rd |

Z,C,N,V |

1 |

|

NEGRd |

Дополнение до 2 |

Rd<$00 - Rd |

Z,C,N,V,H |

1 |

|

SBR Rd,K |

Установить бит(ы) в регистре |

Rd<Rd OR К |

Z,N,V |

1 |

|

CBR Rd.K |

Сбросить бит(ы) в регистре |

Rd<RdAND(FFh-K) |

Z,N,V |

1 |

|

INCRd |

Увеличить на 1 |

Rd<Rd+1 |

Z,N,V |

1 |

|

DECRd |

Уменьшить на 1 |

Rd<Rd-1 |

Z,N,V |

1 |

|

TSTRd |

Проверить на 0 или |

Rd<RdANDRd |

Z,N,V |

1 |

|

CLRRd |

Очистить регистр |

Rd<RdXORRd |

Z,N,V |

1 |

|

SERRd |

Установить регистр |

Rd<$FF |

None |

1 |

Команды ветвления

|

Мнемоник |

Описание |

Действие |

Флаги |

Циклы |

|

RJMPk |

Относительный переход |

РС<РС+к+1 |

None |

2 |

|

LJMP |

Переход по адресу (Z) |

PC<Z |

None |

2 |

|

RCALLk |

Относительный вызов подпрограммы |

РС<РС+к+1 |

None |

3 |

|

ICALL |

Вызов подпрограммы по адресу (Z) |

PC<Z |

None |

3 |

|

RET |

Выход из подпрограммы |

PC<STACK |

None |

4 |

|

REfl |

Выход из прерывания |

PC<STACK |

S |

4 |

|

CPSERd.Rr |

Сравнить, пропуск, если равно |

if(Rd=Rr) PC<PC+2 или З |

None |

1/2 |

|

CP Rd,Rr |

Сравнить |

Rd-Rr |

Z.N.V.C.H |

1 |

|

CPC Rd.Rr |

Сравнить с переносом |

Rd-Rr-C |

Z,N,V,C,H |

1 |

|

CPI Rd,K |

Сравнить с константой |

Rd-K |

Z,N,V,C,H |

1 |

|

BREQk |

Переход, если равно |

if(Z=1)PC<PC+k+1 |

None |

1/2 |

|

BRNEk |

Переход, если неравно |

if(Z=0)PC<PC+k+1 |

None |

1/2 |

|

BRCSk |

Переход, если установлен перенос |

if(C=1)PC<PC+k+1 |

None |

1/2 |

|

BRCCk |

Переход, если сброшен перенос |

if(C=O) PC<PC+k+1 |

None |

1/2 |

|

BRSHk |

Переход, если равно или больше |

if(C=O) PC<PC+k+1 |

None |

1/2 |

|

BRLO к |

Переход, если меньше |

if(C=1)PC<PC+k+1 |

None |

1/2 |

|

BRMIk |

Переход, если минус |

if(N=1)PC<PC+k+1 |

None |

1/2 |

|

BRPLk |

Переход, если плюс |

if(N=O) PC<PC+k+1 |

None |

1/2 |

|

BRGEk |

Переход, если больше или равно со знаком |

if(NXORV=0)PC<PC+k+1 |

None |

1/2 |

|

BRLTk |

Переход, если меньше нуля со знаком |

if(NXORV=1)PC<PC+k+1 |

None |

1/2 |

Команды пересылки

|

Мнемони |

Описание |

Действие |

Флаги |

Циклы |

|

MOVRd.Rr |

Пересылка между регистрами |

Rd<Rr |

None |

1 |

|

LDI Rd,K |

Загрузить константу |

Rd<K |

None |

1 |

|

LDRd,X |

Загрузить регистр непосредственно |

Rd<(X) |

None |

2 |

|

LD Rd,X+ |

Загрузить регистр непосредственно с постинкрементом |

Rd<(X),X<X+1 |

None |

2 |

|

ID Rd,-X |

Загрузить регистр непосредственно с предварительным декрементом |

X<X-1,Rd<(X) |

None |

2 |

|

LDRd.Y |

Загрузить регистр непосредственно |

Rd<(Y) |

None |

2 |

|

LD Rd,Y+ |

Загрузить регистр непосредственно с постинкрементом |

Rd<(Y),Y<Y+1 |

None |

2 |

|

LD Rd,-Y |

Загрузить регистр непосредственно с предварительным декрементом |

Y<Y-1,Rd<(Y) |

None |

2 |

|

LDD Rd,Y+q |

Загрузить регистр непосредственно со смещением |

Rd<(Y+q) |

None |

2 |

|

U)Rd,Z |

Загрузить регистр непосредственно |

Rd<(Z) |

None |

2 |

|

LD Rd,Z+ |

Загрузить регистр непосредственно с постинкрементом |

Rd<(Z),Z<Z+1 |

None |

2 |

|

LD Rd,-Z |

Загрузить регистр непосредственно с предварительным декрементом |

Z<Z-1,Rd<(Z) |

None |

2 |

|

LDD Rd,Z+q |

Загрузить регистр непосредственно со смещением |

Rd<(Z+q) |

None |

2 |

|

LDS Rd,k |

Загрузить из ОЗУ |

Rd<(k) |

None |

3 |

|

STX,Rr |

Записать регистр непосредственно |

(X)<Rr |

None |

2 |

|

STX+,Rr |

Записать регистр непосредственно с постинкрементом |

(X)<Rr,X<X+1 |

None |

2 |

|

ST -X,Rr |

Записать регистр непосредственно с предварительным декрементом |

X<X-1,(X)<Rr |

None |

2 |

|

STY,Rr |

Записать регистр непосредственно |

(Y)<Rr |

None |

2 |

|

STY+.Rr |

Записать регистр непосредственно с постинкрементом |

(Y)<Rr,Y<Y+1 |

None |

2 |

|

ST -Y.Rr |

Записать регистр непосредственно с пред.дек-рементом |

Y<Y-1,(Y)<Rr |

None |

2 |

|

STDY+q.Rr |

Записать регистр непосредственно со смещением |

(Y+q)<Rr |

None |

2 |

|

STZ,Rr |

Записать регистр непосредственно |

(Z)<Rr |

None |

2 |

|

STZ+.Rr |

Записать регистр непосредственно с постинкрементом |

(Z)<Rr,Z<Z+1 |

None |

2 |

|

ST-Z,Rr |

Записать регистр непосредственно с предварительным декрементом |

Z<Z-1,(Z)<Rr |

None |

2 |

|

STDY+q.Rr |

Запись регистра непосредственно со смещением |

(Y+q)<Rr |

None |

2 |

|

STSk.Rr |

Записать в ОЗУ |

(k)<Rr |

None |

3 |

|

LPM |

Загрузка из памяти программ |

R0<(Z) |

None |

3 |

|

IN Rd, P |

Ввод из порта |

Rd<P |

None |

1 |

|

OUTP.Rr |

Вывод в порт |

P<Rr |

None |

1 |

|

PUSH Rr |

Записать в стек |

STACK<Rr |

None |

2 |

|

POPRr |

Прочитать из стека |

Rr<STACK |

None |

2 |

Команды работы с битами

|

Мнемоника |

Описание |

Действие |

Флаги |

Циклы |

|

SBI Р,Ь |

Установить бит в регистре ввода/вывода |

1/О(Р,Ь)<1 |

None |

2 |

|

CBI Р,Ь |

Сбросить бит в регистре ввода/вывода |

l/O(P,b)<0 |

None |

2 |

|

LSLRd |

Логический сдвиг влево |

Rd(n+1)<Rd(n),Rd(0)<0 |

Z,C,N,V |

1 |

|

LSRRd |

Логический сдвиг вправо |

Rd(n)<Rd(n+1),Rd(7)<0 |

Z.C.N.V |

1 |

|

ROLRd |

Сдвиг влево через С |

Rd(0)<C,Rd(n+1)<Rd(n), C<Rd(7) |

Z.C.N.V |

1 |

|

RORRd |

Сдвиг вправо через С |

Rd(7)<C, Rd(n)<Rd(n+1), C<Rd(0) |

Z,C,N,V |

1 |

|

ASRRd |

Арифметический сдвиг вправо |

Rd(n)<Rd(n+1),n=0...6 |

Z,C,N,V |

1 |

|

SWAP Rd |

Обмен нибблов |

Rd(3-0)<Rd(7-4) Rd(7-4)<Rd(3-0) |

None |

1 |

|

BSETs |

Установить флаг |

SREG(s)<1 |

SREG(s) |

1 |

|

BCLRs |

Сбросить флаг |

SREG(s)<0 |

SREG(s) |

1 |

|

BST Rr,b |

Запомнить бит в Т |

T<Rr(b) |

T |

1 |

|

ВLD Rd,b |

Прочитать бит из Г |

Rd(b)<T |

None |

1 |

|

SEC |

Установить перенос |

C<1 |

С |

1 |

|

CLC |

Сбросить перенос |

C<0 |

С |

1 |

|

SEN |

Установить флаг N |

N<1 |

N |

1 |

|

CLN |

Сбросить флаг N |

N<0 |

N |

1 |

|

SEZ |

Установить флаг Z |

Z<1 |

Z |

1 |

|

CLZ |

Сбросить флаг Z |

Z<0 |

Z |

1 |

|

SEI |

Разрешить прерывания |

K1 |

I |

1 |

|

CU |

Запретить прерывания |

КО |

1 |

1 |

|

SES |

Установить флаг S |

S<1 |

S |

1 |

|

CLS |

Сбросить флаг S |

S<0 |

S |

1 |

|

SEV |

Установить флаг V |

V<1 |

V |

1 |

|

CLV |

Сбросить флаг V |

V<0 |

V |

1 |

|

SET |

Установить флаг Т |

T<1 |

T |

1 |

|

CLT |

Сбросить флаг Т |

T<0 |

T |

1 |

|

SEH |

Установить флаг Н |

H<1 |

H |

1 |

|

CLH |

Сбросить флаг Н |

H<0 |

H |

1 |

|

NOP |

Нет операции |

|

None |

1 |

|

SLEEP |

Останов |

|

None |

3 |

|

WDR |

Сброс сторожевого таймера |

|

None |

1 |

Вопрос №15

Аналогово-цифровой преобразователь

Отличительные особенности:

10-разрядное разрешение;

время преобразования 65 - 260 мкс;

8 мультиплексированных однополярных входов;

прерывание по завершении преобразования АЦП;

механизм подавления шумов в режиме сна.

Краткое описание. AT90mega103 содержит 10-разр. АЦП последовательного приближения. АЦП связан с 8-канальным аналоговым мультиплексором, 8 однополярных входов которого связаны с линиями порта F. Общий входных сигналов должен иметь потенциал 0В (т. е. связан с GND). АЦП имеет отдельный вывод питания AVCC (аналоговое питание). AVCC не должен отличаться более чем на ± 0.3В от VCC.

Принцип действия. АЦП преобразовывает входное аналоговое напряжение в 10-разр. код методом последовательных приближений. Минимальное значение соответствует уровню GND, а максимальное уровню AREF минус 1 мл. разр. Результат преобразования зависит от полярности входного сигнала. Для определения полярности достаточно опросить старший бит результата преобразования (ADC9 в ADCH). Если данный бит равен лог. 1, то результат отрицательный, если же лог. 0, то положительный. Результат преобразования отрицательных входных сигналов представляется в дополнительном коде.

Работа АЦП разрешается путем установки бита ADEN в ADCSRA. Выбор опорного источника и канала преобразования невозможно выполнить до установки ADEN. АЦП генерирует 10-разрядный результат, который помещается в пару регистров данных АЦП ADCH и ADCL. Необходимо первым считать содержимое регистра ADCL, а затем ADCH. После чтения ADCL блокируется доступ к регистрам данных для АЦП. Если считан ADCL и преобразование завершается перед чтением регистра ADCH, то ни один из регистров не может модифицироваться и результат преобразования теряется. После чтения ADCH доступ к регистрам ADCH и ADCL со стороны АЦП снова разрешается. АЦП генерирует собственный запрос на прерывание по завершении преобразования. Если между чтением регистров ADCH и ADCL запрещен доступ к данным для АЦП, то прерывание возникнет, даже если результат преобразования будет потерян.

Запуск преобразования. Одиночное преобразование запускается путем записи лог. 1 в бит запуска преобразования АЦП ADSC. Данный бит остается в высоком состоянии в процессе преобразования и сбрасывается по завершении преобразования. Первое преобразование инициируется путем записи лог. 1 в бит ADSC регистра ADCSRA. Модуль АЦП содержит предделитель, который формирует производные частоты свыше 100 кГц по отношению к частоте синхронизации ЦПУ. Коэффициент деления устанавливается с помощью бит ADPS в регистре ADCSRA. Предделитель начинает счет с момента включения АЦП установкой бита ADEN в регистре ADCSRA. Предделитель работает пока бит ADEN = 1 и сброшен, когда ADEN = 0. Если инициируется однополярное преобразование установкой бита ADSC в регистре ADCSRA, то преобразование начинается со следующего нарастающего фронта тактового сигнала АЦП. Нормальное преобразование требует 13 тактов синхронизации АЦП. После начала нормального преобразования на выборку-хранение затрачивается 2 такта синхронизации АЦП. По завершении преобразования результат помещается в регистры данных АЦП и устанавливается флаг ADIF. В режиме одиночного преобразования одновременно сбрасывается бит ADSC.

Входные каналы АЦП. При переключении входного канала необходимо учесть некоторые рекомендации, которые исключат некорректность переключения. В режиме одиночного преобразования переключение канала необходимо выполнять перед началом преобразования. Переключение канала может произойти только в течение одного такта синхронизации АЦП после записи лог. 1 в ADSC. Однако самым простым методом является ожидание завершения преобразования перед выбором нового канала.

В режиме автоматического перезапуска канал необходимо выбирать перед началом первого преобразования. Переключение канала происходит аналогично – в течение одного такта синхронизации АЦП после записи лог. 1 в ADSC. Но самым простым методом является ожидание завершения первого

преобразования, а затем переключение канала. Поскольку следующее преобразование уже запущено автоматически, то следующий результат будет соответствовать предыдущему каналу. Последующие преобразования отражают результат для нового канала. При переключении на дифференциальный канал первое преобразование будет характеризоваться плохой точностью из-за переходного процесса в схеме

автоматической регулировки смещения. Следовательно, первый результат такого преобразования рекомендуется игнорировать.

Подавитель шумов АЦП. АЦП характеризуется возможностью подавления шумов, которые вызваны работой ядра ЦПУ и периферийных устройств ввода-вывода. Подавитель шумов может быть использован в режиме снижения шумов АЦП и в режиме холостого хода. При использовании данной функции

необходимо придерживаться следующей процедуры:

1. Выберите режим одиночного преобразования и разрешите прерывание по

завершении преобразования.

2. Введите режим уменьшения шумов АЦП (или режим холостого хода). АЦП запустит преобразование как только остановится ЦПУ.

3. Если до завершения преобразования не возникает других прерываний, то АЦП вызовет прерывание ЦПУ и программа перейдет на вектор обработки прерывания по завершении преобразования АЦП. Если до завершения преобразования другое прерывание пробуждает микроконтроллер, то это прерывание

обрабатывается, а по завершении преобразования генерируется соответствующий запрос на прерывание. АЦП остается в активном режиме пока не будет выполнена очередная команда sleep.

Рекомендации по снижению влияния шумов на результат преобразования.

1. Выполняйте путь аналоговых сигналов как можно более коротким. Следите, чтобы аналоговые сигналы проходили над плоскостью (слоем) с аналоговой землей (экраном) и далеко от проводников, передающих высокочастотные цифровые сигналы.

2. Вывод AVCC необходимо связать с цифровым питанием VCC через LC-цепь в соответствии.

3. Используйте функцию подавления шумов АЦП, внесенных работой ядра ЦПУ.

4. Если какой-либо из выводов АЦП используется как цифровой выход, то чрезвычайно важно не допустить переключение состояния этого выхода в процессе преобразования.

Бит 7 – ADEN: Разрешение работы АЦП

Запись в данный бит лог. 1 разрешает работу АЦП. Если в данный бит записать лог. 0, то АЦП отключается, даже если он находился в процессе преобразования.

Бит 6 – ADSC: Запуск преобразования АЦП

В режиме одиночного преобразования установка данного бита инициирует старт каждого преобразования. В режиме автоматического перезапуска установкой этого бита инициируется только первое преобразование, а все остальные выполняются автоматически. Первое преобразование после разрешения работы АЦП, инициированное битом ADSC, выполняется по расширенному алгоритму и длится 25 тактов синхронизации АЦП вместо обычных 13 тактов. Это связано с необходимостью инициализации АЦП.

Бит 5 – ADFR: Выбор режима автоматического перезапуска АЦП

Если в данный бит записать лог. 1, то АЦП перейдет в режим автоматического перезапуска. В этом режиме АЦП автоматически выполняет преобразования и модифицирует регистры результата преобразования через фиксированные промежутки времени. Запись лог. 0 в этот бит прекращает работу в данном режиме.

Бит 4 – ADIF: Флаг прерывания АЦП

Данный флаг устанавливается после завершения преобразования АЦП и обновления регистров данных. Если установлены биты ADIE и I (регистр SREG), то происходит прерывание по завершении преобразования. Флаг ADIF сбрасывается аппаратно при переходе на соответствующий вектор прерывания. Альтернативно флаг ADIF сбрасывается путем записи лог. 1 в него. При вы-

полнении команды «чтение-модификация-запись» с регистром ADCSRA ожидаемое прерывание может быть отключено. Это также распространяется на использование инструкций SBI и CBI.

Бит 3 – ADIE: Разрешение прерывания АЦП

После записи лог. 1 в этот бит, при условии, что установлен бит I в регистре SREG, разрешается прерывание по завершении преобразования АЦП.

Биты 2:0 – ADPS2:0: Биты управления предделителем АЦП. Данные биты определяют соотношение между тактовой частотой ЦПУ и частотой входной синхронизации АЦП.

Вопрос №16

Сторожевой таймер

Сторожевой таймер – это 16-разряный таймер, который можно использовать как в качестве сторожевого, так и в качестве «интервального» таймера. В этом разделе описывается модуль сторожевого таймера. Сторожевой таймер реализован во всех устройствах MSP430x1xx.

10.1 Введение в сторожевой таймер

Первичная функция модуля сторожевого таймера (WDT) – выполнять рестарт управляемой системы при возникновении проблемы с программным обеспечением. Если установленный временной интервал истек, генерируется системный сброс. Если сторожевая функция в приложении не нужна, модуль может быть сконфигурирован как интервальный таймер для генерации прерываний через установленные интервалы времени.

Сторожевой таймер обладает следующими возможностями:

Восемь программно настраиваемых временных интервалов

Режим сторожевого таймера

Режим интервального отсчета

Доступ к регистру управления WDT защищен паролем

Управление функцией вывода nonRST/NMI

Возможность выбора источника тактовых импульсов

Возможность останова для уменьшения потребляемой мощности

Блок схема модуля WDT показана на рис.9-1.

|

Примечание: Работа сторожевого таймера после подачи питания После сигнала PUC, модуль WDT автоматически конфигурируется в сторожевом режиме с начальным интервалом сброса ~32 мС с использованием DCOCLK. Пользователь должен выполнить необходимую настройку или остановить WDT до истечения начального интервала сброса. |

Рис.10-1

Блок-схема сторожевого таймера

Рис.10-1

Блок-схема сторожевого таймера

10.2 Функционирование сторожевого таймера

Модуль WDT можно сконфигурировать с помощью регистра WDTCTL как сторожевой либо интервальный таймер. Регистр WDTCTL также содержит управляющие биты для конфигурирования вывода nonRST/NMI. WDTCTL – это 16-разрядный, защищенный паролем регистр чтения/записи. Любое чтение или попытка записи должны использовать команды-слова, а попытка записи должна содержать пароль записи 05Ah в старшем байте. Любая запись в WDTCTL любого значения, отличного от 05Ah в старшем байте приведет к нарушению ключа безопасности и запуску системного сброса PUC независимо от режима таймера. При любом чтении WDTCTL в старшем байте читается 069h.

10.2.1 Счетчик сторожевого таймера

Счетчик сторожевого таймера (WDTCNT) – это 16-разрядный суммирующий счетчик, не имеющий прямого доступа из программы. Управление WDTCNT и выбор временных интервалов производится через регистр управления сторожевым таймером WDTCTL. WDTCNT может тактироваться от ACLK или SMCLK. Источник тактирования выбирается с помощью битаWDTSSEL.

10.2.2 Сторожевой режим

После состояния PUC, модуль WDT конфигурируется в сторожевом режиме с начальным интервалом сброса ~32 мС с использованием DCOCLK. Пользователь должен настроить, остановить или очистить WDT до истечения начального интервала сброса, в противном случае будет сгенерирован новый сигнал PUC. Когда WDT сконфигурирован в сторожевом режиме, запись в WDTCTL неправильного пароля или истечение выбранного интервала времени приведет к запуску PUC. PUC сбросит WDT к исходному состоянию и сконфигурирует вывод nonRST/NMI на режим сброса.

10.2.3 Режим интервального таймера

Установка бита WDTTMSEL в «1» приводит к выбору режима интервального таймера. Этот режим можно использовать для получения периодических прерываний. В режиме интервального таймера флаг WDTIFG устанавливается по истечении выбранного интервала времени. PUC не генерируется в режиме интервального таймера по истечении установленного временного интервала, а WDTIFG разрешает биту WDTIE оставаться неизменным.

Когда биты WDTIE и GIE установлены, флаг WDTIFG запрашивает прерывание. Флаг прерывания WDTIFG автоматически сбрасывается, когда обслуживается его запрос на прерывание, либо же он может быть сброшен программно. Адреса векторов прерывания различаются для интервального и сторожевого режимов таймера.

|

Примечание: Модификация сторожевого таймера Интервал WDT должен быть изменен совместно с WDTCNTCL=1 в одной команде, чтобы избежать неожиданной немедленной генерации PUC или прерывания. Модуль WDT должен быть приостановлен перед сменой источника тактирования для предотвращения возможности установки некорректного интервала. |

10.2.4 Прерывания сторожевого таймера

WDT использует два бита в SFR для управления прерыванием.

Флаг прерывания WDT, WDTIFG, расположенный в IFG1.0

Бит разрешения прерывания от WDT, WDTIE, расположенный в IE1.0

Если WDT используется в сторожевом режиме, флаг WDTIFG является источником вектора прерывания по сбросу. WDTIFG может быть использован процедурой обработки прерывания по сбросу для определения, был ли сторожевой таймер причиной сброса устройства. Если флаг установлен, состояние сброса было инициировано сторожевым таймером по истечении времени, либо произошло нарушение ключа безопасности. Если WDTIFG очищен, сброс был вызван другим источником.

При использовании WDT в режиме интервального таймера, флаг WDTIFG устанавливается после выбранного временного интервала и запрашивает прерывание интервального таймера WDT, если установлены биты WDTIE и GIE. Вектор прерывания интервального таймера отличается от вектора сброса, используемого в сторожевом режиме. В режиме интервального таймера флаг WDTIFG сбрасывается автоматически при обработке прерывания, либо же он может быть сброшен программно.

10.2.5 Работа в режимах пониженного энергопотребления

Устройства MSP430 имеют несколько режимов пониженного энергопотребления. Различные сигналы тактирования доступны в различных режимах пониженного энергопотребления. Потребности пользовательского приложения и тип используемой системы тактирования определяют, как WDT должен быть сконфигурирован. К примеру, WDT не должен конфигурироваться в сторожевом режиме с SMCLK в качестве источника тактирования, если пользователь хочет использовать 3-ий режим пониженного потребления, поскольку SMCLK не активен в режиме LPM3 и WDT не будет функционировать. Если сторожевой таймер не нужен, с помощью бита WDTHOLD можно остановить WDTCNT, чтобы уменьшить энергопотребление.

10.2.6 Примеры программного обеспечения

Любая операция записи в WDTCTL должна быть операцией-словом со значением 05Ah (WDTPW) в старшем байте:

; Периодическая отчистка активного сторожевого таймера

MOV #WDTPW+WDTCNTCL,&WDTCTL

;

; Изменение интервала сторожевого таймера

MOV #WDTPW+WDTCNTL+SSEL,&WDTCTL

;

; Останов сторожевого таймера

MOV #WDTPW+WDTHOLD,&WDTCTL

;

; Переключение WDT в интервальный режим с интервалом clock/8192

MOV #WDTPW+WDTCNTCL+WDTTMSEL+WDTIS0,&WDTCTL

10.3 Регистры сторожевого таймера

Регистры модуля сторожевого таймера приведены в таблице 10-1.

Таблица 10-1. Регистры сторожевого таймера.

|

Регистр |

Краткое обозначение |

Тип регистра |

Адрес |

Исходное состояние |

|

Регистр управления сторожевым таймером |

WDTCTL |

Чтение/запись |

0120h |

06900h после PUC |

|

SFR регистр 1 разрешения прерываний |

IE1 |

Чтение/запись |

0000h |

Сброс с PUC |

|

SFR регистр 1 флагов прерываний |

IFG1 |

Чтение/запись |

0002h |

Сброс с PUC1 |

1)WDTIFG сбрасывается с POR

WDTCTL, регистр сторожевого таймера

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

Читается как 069h |

|

WDTPWx, должен записываться как 05Ah |

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

WDTHOLD |

WDTNMIES |

WDTNMI |

WDTTMSEL |

WDTCNTCL |

WDTSSEL |

WDTISx |

|

rw-0 |

rw-0 |

rw-0 |

rw-0 |

r0(w) |

rw-0 |

rw-0 |

rw-0 |

|

WDTPWx |

Биты 15-8 |

Пароль сторожевого таймера. Всегда читается как 069h. Должен записываться как 05Ah, в противном случае будет сгенерирован PUC. |

|

WDTHOLD |

Бит 7 |

Останов сторожевого таймера. Этот бит останавливает сторожевой таймер. Установка WDTHOLD=1, когда WDT не используется, позволяет снизить энергопотребление. 0 Сторожевой таймер не остановлен 1 Сторожевой таймер остановлен |

|

WDTNMIES |

Бит 6 |

Выбор фронта NMI сторожевого таймера. Этот бит позволяет выбрать фронт прерывания для NMI прерывания при WDTNMI=1. Изменение этого бита может вызвать NMI. Чтобы избежать случайного запуска NMI следует изменять этот бит при WDTNMI=0. 0 NMI прерывание происходит по переднему фронту 1 NMI прерывание происходит по спаду |

|

WDTNMI |

Бит 5 |

Выбор NMI сторожевого таймера. Этот бит позволяет установить режим функционирования вывода nonRST/NMI. 0 Функция сброса 1 Функция NMI |

|

WDTTMSEL |

Бит 4 |

Выбор режима сторожевого таймера 0 Сторожевой режим 1 Режим интервального таймера |

|

WDTCNTCL |

Бит 3 |

Очистка счетчика сторожевого таймера. Установкой WDTCNTCL=1 производится очистка счетчика до значения 0000h. Бит WDTCNTCL автоматически сбрасывается. 0 Действие не производится 1 WDTCNT = 0000h |

|

WDTSSEL |

Бит 2 |

Выбор источника тактирования сторожевого таймера 0 SMCLK 1 ACLK |

|

WDTISx |

Биты 1-0 |

Выбор интервала сторожевого таймера. Эти биты определяют интервал времени сторожевого таймера, по истечении которого устанавливается флаг WDTIFG и/или генерируется сигнал PUC. 00 Частота источника тактирования сторожевого таймера / 32768 01 Частота источника тактирования сторожевого таймера / 8192 10 Частота источника тактирования сторожевого таймера / 512 11 Частота источника тактирования сторожевого таймера / 64 |

IE1, регистр 1 разрешения прерываний

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

WDTIE |

|

|

|

|

|

|

|

|

rw-(0) |

|

|

Биты 7-1 |

Эти биты могут быть использованы другими модулями. См. справочное руководство конкретного устройства. |

|

WDTIE |

Бит 0 |

Разрешение прерывания от сторожевого таймера. Этот бит разрешает прерывание WDTIFG в режиме интервального таймера. Нет необходимости устанавливать этот бит в режиме сторожевого таймера. Поскольку другие биты в IE1 могут быть использованы другими модулями, рекомендуется устанавливать и очищать эти биты с помощью команд BIS.B или BIC.B, а не командами MOV.B или CLR.B. 0 Прерывание запрещено 1 Прерывание разрешено |

IFG1, регистр 1 флагов прерываний

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

WDTIFG |

|

|

|

|

|

|

|

|

rw-(0) |

|

|

Биты 7-1 |

Эти биты могут быть использованы другими модулями. См. справочное руководство конкретного устройства. |

|

WDTIE |

Бит 0 |

Флаг прерывания сторожевого таймера. В сторожевом режиме WDTIFG остается установленным до сброса программным обеспечением. В интервальном режиме бит WDTIFG сбрасывается автоматически при обслуживании прерывания или же может быть сброшен программно. Поскольку другие биты в IE1 могут быть использованы другими модулями, рекомендуется устанавливать и очищать эти биты с помощью команд BIS.B или BIC.B, а не командами MOV.B или CLR.B. 0 Прерывание не ожидается 1 Прерывание ожидается |