- •Структурная схема 8-ми разрядного мп

- •Алгоритм работы управляющего автомата

- •Форматы команд

- •Способы адресации

- •Команды пересылки (команды передачи данных) Арифметические и логические команды

- •Команды сдвига (сдвига в аккумуляторе)

- •Команды передачи управления

- •Спецкоманды

- •Псевдокоманды

- •Запоминающие устройства

- •1. Регистровый способ адресации с одним регистром Rd

- •Сторожевые таймеры

- •Организация таймеров/счетчиков.

Вопрос №1

Микропроцессоры и микроЭВМ являются в настоящее время наиболее массовыми средствами вычислительной техники.

Эволюция развития микропроцессорной техники:

1971 – фирма IBM выпустила микросхему серии4004- микропрограммируемое вычислительное устройство (МПУ), которое представляет собой однокристальный ЦП, имеющий в своем составе 4-х разрядный параллельный сумматор, 15 4-х разрядных регистров и стек. МПУ 4004 было реализовано на 2300 транзисторах и могло выполнять 45 различных команд. Имело частоту 750 КГц.

1972- появился термин «микропроцессор».

1974- фирма INTEL выпустила 8-разрядный МП с тактовой частотой 2МГц, что дало дальнейшее развитие микропроцессорной технике.

1981- был выпущен 16-разрядный МП 8086 с тактовой ч. 4,77 МГц (3-е поколение). Но слишком сложная и дорогостоящая технология производства заставила выпустить другую модель МП-8086 с 8-р. внешней шиной д-х. Именно этот МП IBM выбрала в качестве ЦП для PC/XT

1984- 4-е поколение МП INTEL. Это МП 80286 16-разрядный, тактовая ч. которого была повышена до 8МГц. В настоящее время т.ч. МП 80286 повышена до 20МГц.

1986- 5-е поколение. МП 80386, 32-разрядный, с тактовой ч. до 40 МГц. Данный МП может выполнять одновременно несколько программ.

1989- 6-е поколение МП, имеет условное обозначение 80486. Данный МП объединяет вместе процессор 80386 и сопроцессор 80387 и некоторые системные компоненты, что дает при такой же тактовой ч МП 80386 производить вычисления в 3-4 раза быстрее. Тактовая частота МП 80486DX2 достигает 66 МГц.

1993- появился новый МП – 80586, получивший название Pentium. Данный МП представляет 32-разрядную структуру и имеет уровень интеграции на 20% выше, чем 80486. Тактовая ч неуклонно повышалась и достигла 180-200 МГц, что позволяет говорить о 7-м этапе в развитии микропроцессорной техники.

В последнее время (1998-год изд. методы) такие фирмы, как DEK, Amd, Cyrix, IBM, начинают успешно конкурировать на микропроцессорном рынке с фирмой INTEL. Так, фирмой DEK разработан МП Alpha-Chip AXP 21064, тактовая частота которого составляет 200МГц, а производительность 300 млн. оп. в секунду. Разрядность МП достигает 64 при напр. питания 3,3 В. Фирмой DEK разработан также более простой вариант процессора Alpha-Chip- микропроцессор AXP 21066, тактовая ч.- до 166МГц и предназначенный для массового спроса.

Основные понятия:

Микропроцессор (МП)– программно-управляемое устройство, осуществляющее прием, обработку и выдачу цифровой информации и служит для реализации вычислительной или управляющей структуры, построенное на одной (однокристальный МП) или нескольких (многокристальный МП) больших инт. схем (БИС), входящих в состав микропроцессорного комплекта(МПК).

МПК- называется совокупность микропроцессорных и других БИС, совместных по конструктивно-технологическому исполнению и предназначенных для совместного использования при построении МП, микроЭВМ, контроллеров и других средств вычислительной техники и цифровой автоматики.

МПС- обычно называют специализированную информационную или управляющую систему, построенную на основе микропроцессорных средств.

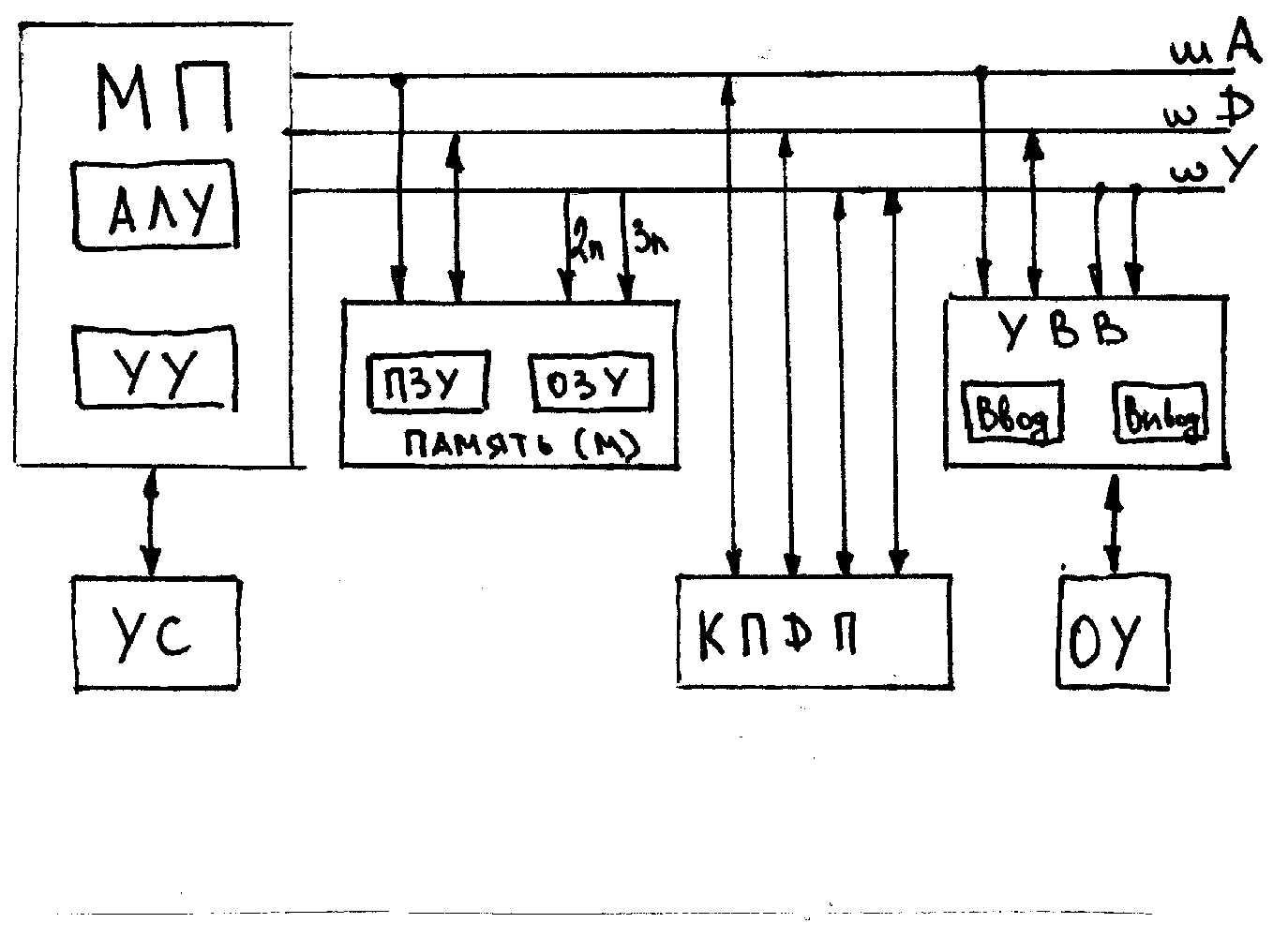

Структурная схема трех-магистральной микроЭВМ.

ш Д-

двунаправленная

Д-

двунаправленная

УС-узел синхронизации –включает в себя тактовый генератор и и опр. цепи, может размещаться в МП (микроконтроллер).

АЛУ- 8-разрядная комбинационная схема, выполняющая арифметические и логические операции.

Память- имеет две структуры: Неймановская и Гарвардская.

Н.- память программ (ПЗУ) и память (ОЗУ) находятся в едином физическом устройстве.

Г.- ПЗУ и ОЗУ – физически разделены.

Прямо адресуемое пространство в памяти определяется шиной адреса.

Для микропроцессоров характерна трехшинная структура, содержащая шину адреса, двунаправленную шину данных и шину управления. Как видно из рисунка типовая структура МП-системы предполагает наличие общего сопряжения ( общего или единого интерфейса) для модулей памяти (ОЗУ и ПЗУ) и периферийных устройств- внешних ЗУ и устройств ввода-вывода(УВВ).

Шина адреса имеет 3 состояния: 0,1, z(состояние высокого сопротивления). Эти состояния характерны и для шины данных.

КПДП- контроллер прямого доступа в память.

ОУ- объект управления.

Устройство ВВ- сопрягает ОУ с микроЭВМ. Количество линий определяется структурой микропроцессора, структурой команд.

Состав и характеристики МПК.

МПК серии К580 предназначен для создания средств вычислительной техники и обработки информации.

В состав базового комплекта входят следующие основные БИС:

К580ИК80А - центральный процессор (микропроцессор МП)

К580ВН59 - программируемый контроллер прерываний

К580ИК57 - контроллер прямого доступа в память

К580ИК55 - программируемый параллельный адаптер

К580ИК51 - программируемый последовательный интерфейс

К580ВК28/38 - системный контроллер

К580ГФ24 - генератор тактовых импульсов

К580ВИ53 - программируемый интервальный таймер

К580ВГ75 - программируемый контроллер клавиатуры и индикации

К580ВГ79 - программируемый контроллер ЭЛТ

К580ВА86/87 - шинные формирователи.

Вопрос №2

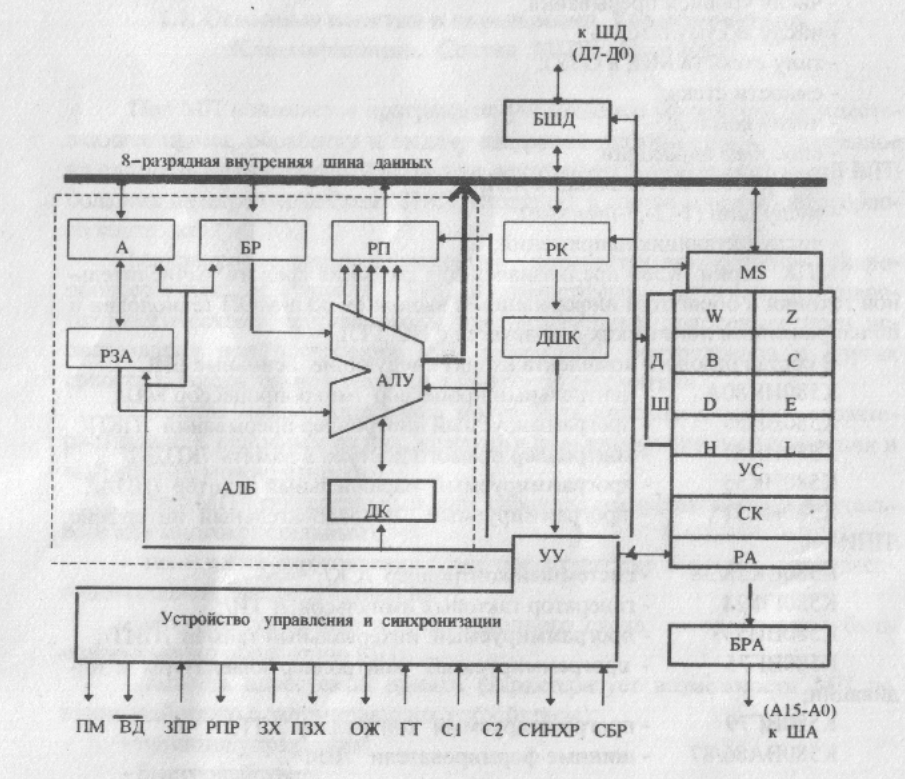

Структурная схема 8-ми разрядного мп

Микропроцессор К580ИК80А (в дальнейшем для краткости обозначаем МП К580) имеет следующие характеристики:

- разрядность шины данных - 8;

- тактовая частота - до 2 МГц;

- разрядность шины адреса – 16

- количество контактов на корпусе - 40:

- размер кристалла кремния - около 30 мм ;

- технология изготовления - п-МОП;

- количество транзисторов - около 5 тысяч;

Укрупнено в схеме МП можно выделить:

- арифметико-логический блок /АЛБ/;

- регистры общего назначения /В,СД,Е,НL/;

- специальные регистры /УС, СК, РА,РК,W. Z/;

- устройство управления и синхронизации;

В состав АЛ Б входят:

- арифметико-логическое устройство АЛ У/ALU;

- регистр-защелка аккумулятора РЗА /ТА/;

- буферный регистр БР/Т/;

- аккумулятор /А/;

- регистр признаков РП /F/;

- десятичный корректор ДК /DА/;

К специальным регистрам относятся:

- регистр команд РК /IR/ с дешифратором команд /ДШК/;

- указатель стека УС /SР/;

- счетчик команд СК /РС/;

- регистр адреса РА /КСА/;

- регистры W,Z - программно недоступные.

Кроме того, можно выделить двунаправленный буфер шины данных БШД /BFD/ и однонаправленный буферный регистр адреса БРА /ВFА/; выбор регистров происходит за счет работы мультиплексора МС /МS и дешифратора /ДШ/,

Обмен информацией между составными частями схемы осуществляется с помощью 8-разрядной внутренней шины По шине передаются команды, адреса, данные, а также информация о состоянии процессора /SW/ в текущем машинном цикле.

АЛУ представляет собой 8-разрядную комбинационную схему, которая выполняет арифметические и логические операции Операнды на входы АЛУ подаются с регистров временного хранения РЗА и БР, что позволяет избежать возникновения "гонок" при работе МП .АЛУ выполняет следующие операции: СЛОЖЕНИЕ, ВЫЧИТАНИЕ, И, ИЛИ. ИСКЛЮЧАЮЩИЕ ИЛИ, ИНВЕРСИЮ, СДВИГ ВПРАВО, СДВИГ ВЛЕВО, ПРИРАЩЕНИЕ ПОЛОЖИТЕЛЬНОЕ, ПРИРАЩЕНИЕ ОТРИЦАТЕЛЬНОЕ.

Аккумулятор используется при выполнении арифметических или логических операций, для хранения одного из операндов и результата выполнения операций. Следует отметить, что у некоторых МП имеется в составе несколько аккумуляторов, что повышает общую производительность микроЭВМ

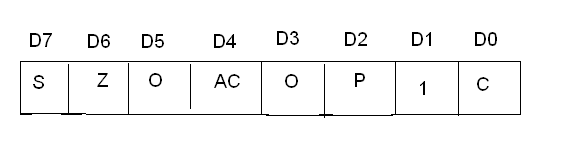

Регистр признаковпредставляет собой набор триггеров, называемых флажками. В зависимости от результатов выполняемых АЛУ операций, каждый триггер устанавливается в состояние 0 или 1.Он служит для организации ветвления.

S=1 отрицательный результат

S=0 триггер не взведен, положительный результат

Z=1 нулевой признак

АС ~H=1 дополнительный перенос(он происходит в АЛУ)

Р=1 паритет( четность)

С=1 перенос, он нужен для десятичной коррекции, для многобайтовых сложений

Десятичный корректор - устройство, назначение которого состоит в том, чтобы под действием специальной команды представить результат выполнения двоичной операции АЛУ как результат операции десятичной арифметики. Коррекция осуществляется прибавлением двоичного кода числа шесть к младшей или старшей тетраде результата, когда содержимое их находится в пределах А – F или в случае возникновения основного или дополнительного переноса.

Регистры общего назначения используются для хранения операндов, промежуточных и конечных результатов, а также адресов и индексов при косвенной и индексной адресациях. Причем регистры могут составлять пары /ВС, DE, HL/ Регистр HL - парный регистр косвенного адреса.

Регистр командпредназначен для хранения кода текущей выполняемой команды. Выполнение каждой команды производится МП в строгой последовательности, определяемой кодом команды, и синхронизируется во времени с сигналами генератора тактовых импульсов.

Указатель стека -16-разрядный регистр, который содержит адрес ячейки стековой памяти занятой информацией /вершины стека/.

Стековая память- область последовательно расположенных регистров или ячеек памяти, снабженных указателем стека, в котором автоматически при записи и считывании устанавливается номер /адрес/ последней занятой ячейки стека. В МП К58О используется "перевернутый" стек, т.е. при передаче в стек информации величина УС уменьшается, а при извлечении информации из стека УС - увеличивается.

Счетчик команд, или программный счетчик, используется для приема и хранения текущего адреса команды. Содержимое СК автоматически инкрементируется после выборки каждого байта команды

Регистр адреса16-разрядный служит для приема и хранения в течение одного машинного цикла адреса команды или операнда и выдачи его на буфер регистра адреса.

Регистры W,Z предназначены для так называемых тендемных (внутренних) пересылок, когда в цикле выполнения команды последовательно передаются два байта информации.

Устройство управления и синхронизации МПсостоит из двух относительно независимых частей:

- первичного автомата, управляющего процессами внутри МП;

- логической схемы, обрабатывающей входные сигналы и формирующей управляющие сигналы в микропроцессорной системе.

Сигналы устройства управленияМП К580ИК80А :

ПМ /DBIN/ - сигнал высокого уровня, показывает на прием с ШД в МП информации, выставленной ЗУ или УВВ;

ВД/ WR/ - сигнал низкого уровня, показывает что информация из МП выдана на ШД и может быть считана ЗУ или УВВ;

ЗПР /INT/ - сигнал запроса прерывания высокого уровня от внешнего устройства;

РПР /INTE/ - сигнал высокого уровня, показывает , что внутренний триггер прерывания в УУ МП установлен в " 1', т.е. разрешены прерывания в МПС;

ЗХ /HOLD/ - сигнал высокого уровня "захват", указывает на запрос другими устройствами системы на управление шинами системы;

ПЗХ /HLDA/ - сигнал высокого уровня "подтверждение захвата", указывает на перевод ША и ШД МП в высокоимпедансное состояние;

ОЖ/WAIT/ - сигнал высокого уровня "ожидание", показывает, что МП в состоянии ожидания;

ГТ /READY/ - сигнал высокого уровня "готовность", показывает на готовность данных от ВУ на ШД для записи в МП или на готовность ВУ к приему данных от МП;

f1,f2 -тактовые импульсы от ГТИ;

СИНХР /SYNC/ - начало машинного цикла МП,

СБР /RESET/ - системный сброс МП.