Схемотехника / Схемотехника(1) / 103 Edition [MEGAAVRR]

.pdf

ÊÒÖ-ÌÊ

ATmega603,

ATmega603L,

ATmega103,

ATmega103L

8-разрядные микроконтроллеры

с Flash памятью емкостью 64/128Kбайт

Отличительные особенности

•Использована AVR расширенная RISC архитектура

•Мощный набор из 121 команды, большинство которых выполняетс я за один машинный цикл

•Емкость внутрисистемно программируемой Flash памяти 64 Кбайт (ATmega603/L) и 128 Кбайт (ATmega103/L), 1000 циклов стирания/записи

•SPI интерфейс внутрисистемного программирования

•Емкость встроенной EEPROM 2 Кбайт (ATmega603/L) и 4 Кбайт (ATmega103/L), 100000 циклов стирания/записи

•Встроенная RAM емкостью 4 Кбайт

•32 8-разрядных регистра общего назначения, набор регистров у правления периферией

•32 программируемых линии I/O, 8 линий выхода, 8 линий входа

•Программируемые последовательные UART и SPI интерфейсы

•Диапазон напряжений питания от 2,7 В до 6,0 В (ATmega603L/ ATmega103L) и

îò 4,0 Â äî 6,0 Â (ATmega603/ ATmega103)

•Диапазон тактовых частот от 0 до 4 МГц (ATmega603L/ ATmega103L) и от 0 до 6 МГц (ATmega603/ ATmega103)

•Производительность до 6 MIPS при частоте 6 МГц

•Встроенная система реального времени с отдельным генера тором

•Äâà 8-разрядных таймера/счетчика с отдельным предделителе м и ШИМ

•16-разрядный таймер/счетчик с отдельным предделителем, реж имами захвата/ сравнения и двойным ШИМ с разрядностью 8, 9 или 10 разрядов

•Программируемый сторожевой таймер с встроенным генерат ором

•Встроенный аналоговый компаратор

•8-канальный 10-разрядный аналого-цифровой преобразователь

•Режимы энергосбережения Idle, Power Save и Power Down

•Программная установка тактовой частоты

•Программная блокировка защиты программных средств

5 5

ATMEL |

ÊÒÖ-ÌÊ |

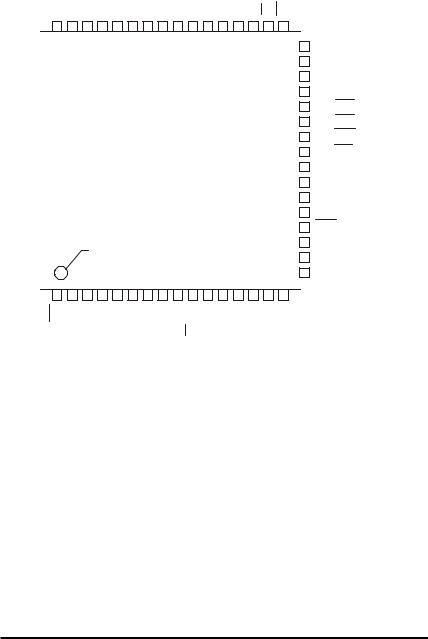

Разводка выводов

|

|

PA3 (Ad3) |

PA4 (AD4) |

PA5 (AD5) |

PA6 (AD6) |

PA7 (AD7) |

ALE |

PC7 (A15) |

PC6 (A14) |

PC5 (A13) |

PC4 (A12) |

PC3 (A11) |

PC2 (A10) |

PC1 (A9) |

PC0 (A8) |

RD |

(AD2) PA2 |

|

|

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

39 |

38 |

37 |

36 |

35 |

34 |

|

48 |

|||||||||||||||

|

49 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(AD1) PA1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(AD0)PA0 |

|

51 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vcc |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

53 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADC7) PF7 |

|

54 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADC6) PF6 |

|

55 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AT90mega103 |

|

|

|

|

|||||||

(ADC5) PF5 |

|

56 |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADC4) PF4 |

|

57 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADC3) PF3 |

|

58 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADC2) PF2 |

|

59 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADC1) PF1 |

|

60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADC0) PF0 |

|

61 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AREF |

|

62 |

|

INDEX CORNER |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

AGND |

|

63 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AVcc |

|

64 |

|

|

|

|

|

|

|

|

10 |

11 |

12 |

13 |

14 |

15 |

|

|

|

|

|

|

|

|

|

||||||||

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

||||||

|

|

PEN |

PE0 |

PE1 |

PE2 |

PE3 |

PE4 |

PE5 |

PE6 |

PE7 |

PB0 |

PB1 |

PB2 |

PB3 |

PB4 |

PB5 |

|

|

|

(PDI/RXD) |

(PD0/TXD) |

(AC+) |

(AC-) |

(INT4) |

(INT5) |

(INT6) |

(INT7) |

(SS) |

(SCK) |

(MOSI) |

(MISO) |

(OC0/PWM0) |

(OC1A/PWM1A) |

WR |

|

|

|

33 |

|

PD7 (T2) |

|

|

|||

|

32 |

|

|

|

31 |

|

PD6 (T1) |

|

30 |

|

PD5 |

|

29 |

|

PD4 (IC1) |

|

28 |

|

PD3 (INT3) |

|

27 |

|

PD2 (INT2) |

|

26 |

|

PD1 (INT1) |

|

25 |

|

PD0 (INT0) |

|

24 |

|

XTAL1 |

|

23 |

|

XTAL2 |

|

22 |

|

GND |

|

21 |

|

Vcc |

|

20 |

|

RESET |

|

19 |

|

TOSC1 |

|

18 |

|

TOSC2 |

16 |

17 |

|

PB7 (OC2/PWM2) |

|

|

|

|

(OC1B/PWM1B) PB6 |

|

|

|

Описание

Приборы ATmega603/103 являются 8-разрядными CMOS микроконтроллерами с AVR усовершенствованной RISC архитектурой. Выполняя большин ство команд за один тактовый цикл, микроконтроллеры ATmega603/103 обеспечивают производительность 1 MIPS на каждый мегагерц тактовой частот ы, что позволяет разработчикам оптимизировать потребление, зависящее в о сновном от тактовой частоты.

AVR ядро базируется на усовершенствованной RISC архитектуре, с регистровым файлом быстрого доступа, содержащим 32 регистра общего наз начения, непосредственно связанных с арифметико-логическим устройством (ALU), и мощно й системой команд. За один тактовый цикл из регистрового файла извлекаются два операнда, выполняется команда и результат записывается в регистр назначения. Та кая высокоэффективная архитектура обеспечивает производительность почти в де сять раз большую, чем стандартные CISC микроконтроллеры.

5 6

ÊÒÖ-ÌÊ

Микроконтроллеры ATmega603/103 располагают следующими возможнос тями: 64/128 Кбайт внутрисистемно программируемой Flash памяти програ мм, 2/4 Кбайт EEPROM данных, 4 Кбайт SRAM данных, 32 линии I/O общего назначения, 8 линий входа, 8 линий выхода, 32 рабочих регистра общего назначения, 4 гибки х таймера/счетчика с режимами сравнения, PWM и UART, программируемый сторожевой тайм ер с встроенным собственным генератором, последовательный SPI порт и три пр ограммно устанавливаемых режима энергосбережения. В режиме Idle оста навливается центральный процессор, но продолжают работать SRAM, таймеры/ счетчики, порт SPI и система прерываний. В режиме Power Down сохраняется содержимое р егистров, но останавливается тактовый генератор и до поступления сиг нала прерывания или аппаратного сброса запрещается выполнение всех функций микроконтроллера. В режиме Power Save все устройства находятся в режиме «сна», но гене ратор таймера продолжает работать, обеспечивая сохранность временной базы

Приборы изготавливаются по технологии энергонезависимо й памяти фирмы Atmel. Встроенная ISP Flash память программ может быть перепрограмм ирована непосредственно в системе, с использованием последовате льного SPI интерфейса, или с помощью обычных программаторов энергонезависимой пам яти. Объединив 8- разрядное RISC CPU с внутрисистемно программируемой Flash памятью большого объема, фирма создала семейство мощных микроконтроллеро в, обеспечивающих реализацию недорогих и очень удобных решений для большого количества встраиваемых применений. Семейство ATmega603/103 поддерживается большим количе ством средств разработки программ и систем, включающих: С-компиляторы, м акроассемблеры, отладчики/симуляторы программ, внутрисхемные эмуляторы и отладочные устройства.

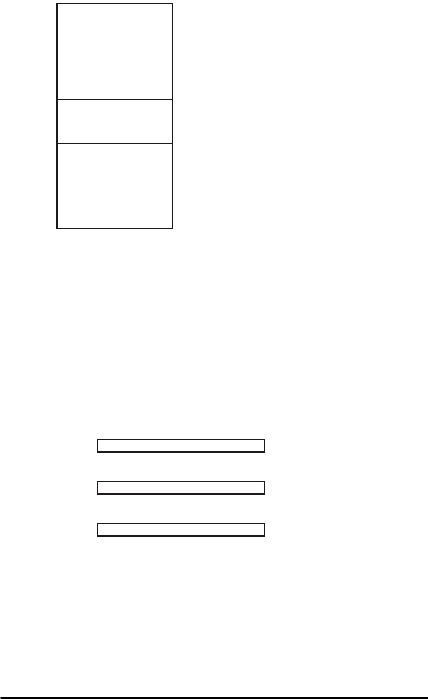

СРАВНЕНИЕ ATmega603 и ATmega103

Микроконтроллер ATmega603 оснащен внутрисистемно программиру емой Flash памятью емкостью 64 Кбайт, 2 Кбайт EEPROM и 4 Кбайт SRAM и не выполняет команду ELPM. Микроконтроллер Atmega103 оснащен внутрисистемно программир уемой Flash памятью емкостью 128 Кбайт, 4 Кбайт EEPROM и 4 Кбайт SRAM. В систему кома нд этого микроконтроллера включена команда ELPM, необходимая д ля обеспечения непрерывного табличного поиска в старшей половине адрес ов Flash памяти.

В Табл. 1 представлены отличия в объеме памяти этих двух при боров.

Таблица 1

Тип прибора |

Объем Flash памяти |

Объем EEPROM |

Объем SRAM |

ATmega603 |

64 Кбайт |

2 Кбайт |

4 Кбайт |

|

|

|

|

ATmega103 |

128 Кбайт |

4 Кбайт |

4 Кбайт |

Назначение выводов

VCC Напряжение питания GND Земля

Port A (PA7..PA0) 8-разрядный двунаправленный порт I/O. К выходам порта могут быть подключены встроенные нагрузочные резисторы (отдельно к каждому разряду). Выходные буферы обеспечивают втекающий ток 20 мА и способн ы напрямую управлять LED индикатором. При использовании выводов порта в качестве входов и установке внешним сигналом в низкое состояние, ток будет вытекать т олько при подключенных встроенных нагрузочных резисторах.

5 7

ATMEL |

ÊÒÖ-ÌÊ |

PF0 - PF7 |

PA0 - PA7 |

PC0 - PC7 |

Vcc

GND

БУФЕРЫ ПОРТА F |

|

|

ДРАЙВЕРЫ/БУФЕРЫ ПОРТА F |

ДРАЙВЕРЫ ПОРТА С |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АНАЛОГОВЫЙ |

ADC |

РЕГИСТР ДАННЫХ |

РЕГИСТР НАПРАВЛ. |

РЕГИСТР ДАННЫХ |

|||||||||||||||||

МУЛЬТИПЛЕКСОР |

ПОРТА А |

|

|

ДАННЫХ ПОРТА А |

ПОРТА С |

||||||||||||||||

|

|

|

|||||||||||||||||||

8-РАЗРЯДНАЯ ШИНА ДАННЫХ

8-РАЗРЯДНАЯ ШИНА ДАННЫХ

AGND

AREF

|

|

ВНУТРЕННИЙ |

ГЕНЕРАТОР |

|

|

|

ГЕНЕРАТОР |

||

|

|

|

||

СЧЕТЧИК |

УКАЗАТЕЛЬ |

СТОРОЖЕВОЙ |

ГЕНЕРАТОР |

|

КОМАНД |

СТЕКА |

ТАЙМЕР |

||

|

||||

FLASH ПАМЯТЬ |

SRAM |

РЕГИСТР |

CИНХРОНИЗАЦИЯ |

|

ПРОГРАММ |

УПРАВЛЕНИЯ MCU |

И УПРАВЛЕНИЕ |

||

|

||||

РЕГИСТР |

РЕГИСТРЫ |

ТАЙМЕРЫ/ |

|

|

КОМАНД |

СЧЕТЧИКИ |

|

||

ОБЩЕГО |

|

|||

|

|

|

||

|

НАЗНАЧЕНИЯ |

|

|

|

ДЕКОДЕР |

X |

|

|

|

Y |

КОНТРОЛЛЕР |

|

||

КОМАНД |

Z |

ПРЕРЫВАНИЯ |

|

|

ЛИНИИ |

|

|

|

|

УПРАВЛЕНИЯ |

|

EEPROM |

|

|

|

ÀËÓ |

|

||

|

|

|

||

|

РЕГИСТР |

ЛОГИКА ПРОГРАМ- |

|

|

|

СОСТОЯНИЯ |

МИРОВАНИЯ |

|

|

|

SPI |

UART |

|

XTAL1

XTAL2

TOSC2

TOSC1

RESET

ALE

WR

RD

PEN

+ - |

|

АНАЛОГОВЫЙ |

КОМПАРАТОР |

||||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

РЕГИСТР |

|

|

|

|

РЕГИСТР НАПРАВЛ. |

|

РЕГИСТР |

|

|

|

РЕГИСТР НАПРАВЛ. |

|

|

РЕГИСТР |

|

|

|

|

РЕГИСТР НАПРАВЛ. |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ДАННЫХ ПОРТА Е |

|

ДАННЫХ ПОРТА Е |

|

|

ДАННЫХ ПОРТА В |

|

ДАННЫХ ПОРТА В |

|

|

ДАННЫХ ПОРТА D |

|

ДАННЫХ ПОРТА D |

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vcc |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

ДРАЙВЕРЫ/БУФЕРЫ ПОРТА Е |

|

|

|

|

|

ДРАЙВЕРЫ/БУФЕРЫ ПОРТА В |

|

|

|

|

|

|

ДРАЙВЕРЫ/БУФЕРЫ ПОРТА D |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

ÐÅ0 - ÐÅ7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ÐÂ0 - ÐÂ7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ÐD0 - ÐD7 |

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

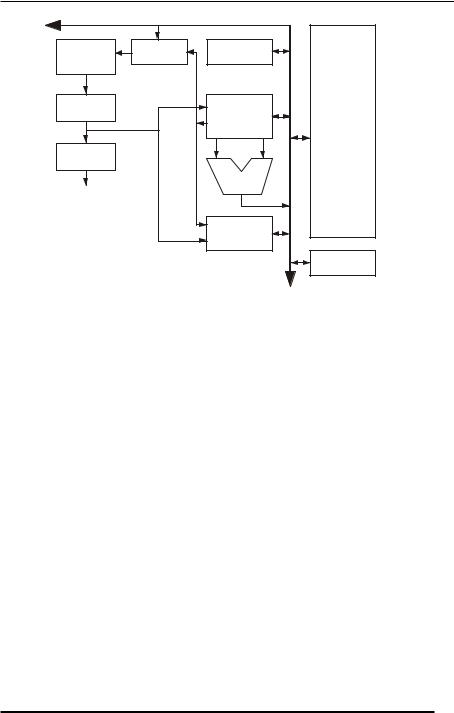

Блок схема микроконтроллеров ATmega603/103.

Порт A, при наличии внешней SRAM, используется в качестве мульт иплексируемой шины адреса/данных.

Port B (PB7. .PB0) 8-разрядный двунаправленный порт I/O со встроенными нагрузочными резисторами. Выходные буферы обеспечивают втекающий ток 20 мА. При использовании выводов порта в качестве входов и устан овке внешним сигналом в низкое состояние, ток будет вытекать только при подключен ных встроенных нагрузочных резисторах. Порт B используется также при реализации разл ичных специальных функций.

Port C (PC7. .PC0) 8-разрядный порт выхода. Выходные буферы обеспечивают втекающий ток 20 мА.

5 8

ÊÒÖ-ÌÊ

Порт C используется также как выходы адреса при использов ании внешней SRAM. Port D (PD7. .PD0) 8-разрядный двунаправленный порт I/O со встроенными нагрузочными резисторами. Выходные буферы обеспечивают втекающий ток 20 мА. При использовании выводов порта в качестве входов и устан овке внешним сигналом в низкое состояние, ток будет вытекать только при подключен ных встроенных нагрузочных

резисторах.

Port E (PE7..PE0) 8-разрядный двунаправленный порт I/O со встроенными нагрузочными резисторами. . Выходные буферы обеспечивают втекающий ток 20 мА. При использовании выводов порта в качестве входов и устан овке внешним сигналом в низкое состояние, вытекающий через них ток обеспечиваетс я только при подключенных встроенных нагрузочных резисторах.

Port F (PF7..PF0) 8-разрядный порт входа. Входы порта используются также как аналоговые входы аналого-цифрового преобразователя .

RESET Вход сброса. Для выполнения сброса необходимо удерживать низкий уровень на входе в течение двух машинных циклов.

XTAL1 Вход инвертирующего усилителя генератора и вход схемы встроенного генератора тактовой частоты.

XTAL2 Выход инвертирующего усилителя генератора.

TOSC1 Вход инвертирующего усилителя генератора таймера/счетчика. TOSC2 Выход инвертирующего усилителя генератора таймера/счетчика. WR Строб записи внешней SRAM.

RD Строб чтения внешней SRAM.

ALE Строб разрешения фиксации адреса, используемый для разре шении внешней памяти. Строб ALE используется для фиксации младшег о байта адреса в защелках адреса в течение первого цикла обращения, в тече ние второго цикла обращения, при обращении к данным, используются выводы AD0AD 7.

AVCC Напряжение питания аналого-цифрового преобразователя. В ывод подсоединяется к внешнему VCC через низкочастотный фильтр . Подробности см. на рис. 47.

AREF Вход аналогового напряжения сравнения для аналого-цифро вого преобразователя. На этот вывод, для обеспечения работы ан алого-цифрового преобразователя, подается напряжение в диапазоне между AG ND и AVCC.

AGND Этот вывод должен быть подсоединен к отдельной аналоговой земле, если плàòà оснащена ею. В ином случае вывод подсоединяетс я к общей земле.

PEN Вывод разрешения программирования в низковольтном последовательном режиме программирования. При удержании этого вывода на ни зком уровне во время сброса по включении питания, прибор перейдет в режим прог раммирования по последовательному каналу.

Тактовый генератор

XTAL1 и XTAL2 являются входом и выходом, соответственно, инвертиру ющего усилителя, который с использованием кварцевого кристалл а или керамического резонатора работает как встроенный генератор, как показа но на Рис. 2, При использовании внешнего источника тактовой частоты выво д XTAL2 должен остаться свободным, сигнал подается на вывод XTAL1, как показано на Рис. 3.

Кварцевый кристалл генератора таймера подсоединяется н епосредственно к выводам OSC1 и OSC2. Внешние конденсаторы не требуются. Генерато р оптимизирован под часовой кварц с частотой 32,768 КГц. Внешний тактовый сигнал,

5 9

ATMEL |

ÊÒÖ-ÌÊ |

подаваемый на эти выводы, поступает на усилитель с полосо й пропускания 256 КГц. Таким образом частота внешнего сигнала должна находитьс я в диапазоне от 0 до 256 КГц.

C2 |

NC |

XTAL2 |

|

XTAL2 |

|||

|

|

||

C1 |

СИГНАЛ |

XTAL1 |

|

ВНЕШНЕГО |

|||

XTAL1 |

|||

ГЕНЕРАТОРА |

|

||

|

|

||

GND |

|

GND |

|

|

|

||

Рис. 2 Подсоединение тактового |

Рис. 3 Подсоединение внешнего |

||

генератора. |

источника тактового сигнала |

||

Архитектура микроконтроллеров ATmega603/103

Файл регистров быстрого доступа, содержит 32 8-разрядных раб очих регистра общего назначения связанных непосредственно с ALU. За один т актовый цикл из файла регистров выбираются два операнда, выполняется операция и результат вновь возвращается в файл регистров.

Шесть из 32 регистров могут быть использованы как три 16-разр ядных регистра указателя косвенной адресации адресного пространства д анных, обеспечивающие эффективное вычисление адресов. Один из этих указателей а дреса используется, также, как указатель адреса для функции непрерывного просмотра таблиц. Эти 16-разрядные дополнительные регистры обозначаются X-регистр, Y-регистр и Z-регистр.

ALU поддерживает арифметические и логические операции меж ду регистрами или между константой и регистром. Выполняются в ALU и операц ии с отдельными регистрами. На Рис. 4 показана AVR расширенная RISC архитектура м икроконтроллеров ATmega603/103.

Âдополнение к операциям с регистрами, регистровый файл м ожет использоваться и для обычной адресации памяти. Это объясн яется тем, что файл регистров располагается по 32 самыми младшими адресами пространства данных, и к ним можно обращаться как к обычным ячейкам памяти.

Пространство памяти I/O содержит 64 адреса периферийных функ ций CPU таких как: регистры управления, таймеры/счетчики, аналого -цифровые преобразователи

èдругие I/O функции. К памяти I/O можно обращаться непосредств енно или как к ячейкам пространства памяти соответствующим адресам ре гистра файлов $20 - $5F. В микроконтроллерах AVR использованы принципы Гарвардской архитектуры - отдельные память и шины для программ и данных. При работе с памятью программ используется одноуровневый конвейер - в то время, как одна команда выполняется, следующая команда выбирается из памяти программ, Такой пр ием позволяет выполнять команду в каждом тактовом цикле. Памятью программ являетс я внутрисистемно программируемая Flash память. За малым исключением AVR команды имеют формат одного 16-разрядного слова, в связи с чем каждый адрес памят и программ содержит одну 16-разрядную команду.

Âпроцессе обработки прерываний и вызовов подпрограмм ад рес возврата счетчика команд (PC) сохраняется в стеке. Стек размещается в SRAM данных и, следовательно размер стека ограничен только общим разме ром SRAM и уровнем

6 0

ÊÒÖ-ÌÊ

ПАМЯТЬ

ПРОГРАММ 32K/64К х 16

РЕГИСТР

КОМАНД

ДЕКОДЕР

КОМАНД

ЛИНИИ

УПРАВЛЕНИЯ

8-разрядная шина данных |

|

||

СЧЕТЧИК |

|

СОСТОЯНИЕ И |

|

КОМАНД |

|

ТЕСТИРОВАНИЕ |

|

|

|

РЕГИСТРЫ |

|

|

|

ОБЩЕГО |

|

|

|

НАЗНАЧЕНИЯ |

ПЕРИФЕРИЯ |

адресация |

|

32 õ 8 |

|

адресация |

|

||

|

|

||

Непосредственная |

Косвенная |

ALU |

|

|

|

|

|

|

|

SRAM |

|

|

|

ДАННЫХ |

|

|

|

4K x 8 |

|

|

|

|

EEPROM |

|

|

|

2K/4K x 8 |

Рис. 4 AVR Enhanced RISC архитектура микроконтроллеров ATmega603/103

ее использования. Все пользовательские программы в подпр ограммах возврата (прежде, чем подпрограммы или прерывания будут выполняться) должн ы инициализировать указатель стека (SP). 16-разрядный указатель стека, с возможно стью чтения/записи располагается в пространстве I/O.

AVR архитектура поддерживает пять различных режимов адрес ации 4000 байт SRAM данных.

Гибкий модуль обработки прерываний имеет в пространстве I/O свой управляющий регистр с дополнительным битом разрешения г лобального прерывания в регистре статуса. Все прерывания имеют свои векторы преры вания в таблице векторов прерывания, располагаемой в начале памяти программ. Приор итеты прерываний соответствуют положению векторов прерываний - прерывани е с наименьшим адресом вектора имеет наивысший приоритет.

Все пространства памяти AVR архитектуры линейны и регулярн ы.

Файл регистров общего назначения

На Рис 5 представлена структура 32 регистров общего назначе ния.

Все регистровые команды обращаются непосредственно к ре гистрам в течение одного тактового цикла. Исключением являются пять логиче ских и арифметических операций с константами (SBCI, SUBI, CPI и ANDI) и операция ORI между константой и содержимым регистра, и команда непосредственной загрузк и константы LDI. Эти команды используют вторую половину регистров регистрового файл а - R16..R31.

Самые общие команды SBC, SUB, CP, AND и OR и все прочие операции между двумя регистрами или с одним регистром используют для зап иси результата регистровый файл.

Как показано на Рис. 5, каждому регистру соответствует адре с памяти данных, отображающий их в первых 32 ячейках пользовательского про странства данных. Хотя

6 1

ATMEL |

|

ÊÒÖ-ÌÊ |

||

|

7 |

0 Addr. |

||

|

R0 |

$00 |

||

|

|

|

|

|

|

R1 |

$01 |

||

|

|

|

|

|

|

R2 |

$02 |

||

|

… |

|

|

|

|

R13 |

|

$0D |

|

|

R14 |

|

$0E |

|

|

R15 |

|

$0F |

|

РЕГИСТРЫ |

R16 |

|

$10 |

|

R17 |

$11 |

|||

ОБЩЕГО |

||||

|

|

|

||

НАЗНАЧЕНИЯ |

… |

|

|

|

R26 |

$1A |

Младший байт регистра X |

|

|

Старший байт регистра X |

R27 |

$1B |

|

|

$1C |

Младший байт регистра Y |

R28 |

||

|

$1D |

Старший байт регистра Y |

R29 |

||

|

|

Младший байт регистра Z |

R30 |

$1E |

|

|

|

Старший байт регистра Z |

R31 |

$1F |

Рис. 5 Регистры общего назначения CPU микроконтроллеров AVR

они не используются как физические ячейки SRAM, такая органи зация памяти обеспечивает гибкое обращение к регистрам , поскольку X,Y и Z регистры могут быть использованы для индексации любого регистра в файле.

SRAM данных имеет объем 4 Кбайт и занимает адресное пространс тво от $0060 до $0FFF.

РЕГИСТР X, РЕГИСТР Y И РЕГИСТР Z

Шесть регистров (с R26 по R31) регистрового файла, кроме обычной для прочих регистров функций, выполняют функцию 16-разрядных регистр ов указателей адреса при косвенной адресации SRAM. Эти три регистра косвенной адр есации определяются как регистры X,Y и Z.

|

15 |

|

|

|

0 |

регистр X |

7 |

|

0 |

7 |

0 |

|

|

R27 |

($1B) |

|

R26 ($1A) |

|

15 |

|

|

|

0 |

регистр Y |

7 |

|

0 |

7 |

0 |

|

|

R29 |

($1D) |

|

R28 ($1C) |

|

15 |

|

|

|

0 |

регистр Z |

7 |

|

0 |

7 |

0 |

|

|

R31 |

($1F) |

|

R30 ($1E) |

Рис. 6 Регистры X,Y и Z.

В различных режимах адресации эти регистры выполняют фун кции фиксированного смещения, автоматического инкремента и декремента (см. оп исания команд).

6 2

ÊÒÖ-ÌÊ

ALU - Арифметико-логическое устройство

Высокопроизводительное AVR ALU соединено непосредственно со всеми 32 быстродействующими регистрами общего назначения. За оди н тактовый цикл ALU выполняет операцию между регистрами этого регистрового файла. Операции ALU подразделяются на три основные категории: арифметически е, логические и операции над битами.

Внутрисистемно программируемая Flash память программ

Коды программ микроконтроллеров ATmega603/103 записываются в 64/128 Кбайт встроенной внутрисистемно программируемой Flash памя ти. Поскольку все команды имеют формат одного или двух 16-разрядных слов, то и память программ имеет организацию 32/64Кx16. Flash память обеспечивает не менее 1000 ци клов стирания/записи.

Таблицы констант могут быть размещены в любом месте всего пространства памяти программ (см. описания команд LPM (Load Program Memory) - Загрузить ба йт памяти программ и ELPM (Extended Load Program Memory) - Загрузить байт памяти программ в расширенном режиме).

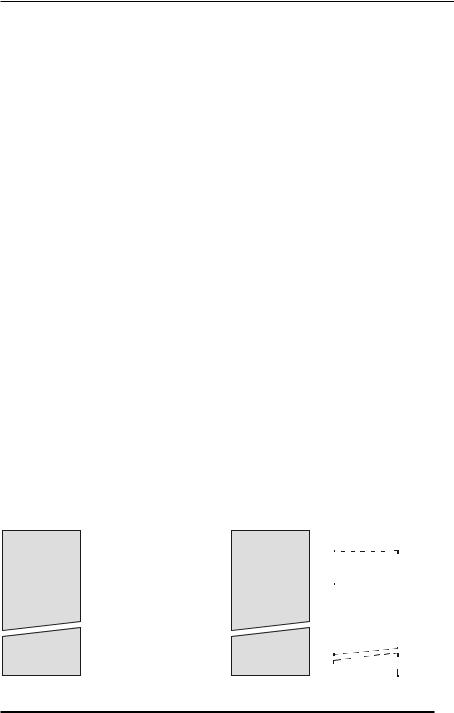

Конфигурация памяти

Микроконтроллеры ATmega603/103 поддерживают две конфигурации, как показано в таблице 2.

Таблица 2 Конфигурация памяти

Конфигурация |

Встроенная SRAM данных |

Внешняя SRAM данных |

|

A |

4000 |

áàéò |

Íåò |

|

|

|

|

B |

4000 |

áàéò |

До 64Кбайт (1) |

Примечание 1. Из 64 Кбайт внешней памяти будут доступны 60 Кбай т.

По первым 4096 адресам памяти данных размещаются регистровы й файл, пространство памяти I/O и встроенная SRAM данных. Из них первые 96 адресов занимают регистровый файл и пространство памяти I/O, в следу ющих 4000 адресов размещается встроенная SRAM.

Конфигурация памяти А |

|

|

Конфигурация памяти B |

|

|||||||||||||||

Память программ |

|

|

|

|

Память программ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

$0000 - $001F |

|

$0000 |

32 регистра |

$0000 - $001F |

|

$0000 |

|

32 регистра |

|

|||||||||||

|

|

64 регистра I/O |

$020 - $005F |

|

|

|

64 регистра I/O |

$020 - $005F |

|||||||||||

FLASH память |

|

Встроенная |

$0060 |

|

FLASH память |

|

Встроенная |

$0060 |

|||||||||||

|

|

|

|

|

|||||||||||||||

|

SRAM |

|

|

|

|

|

SRAM |

|

|||||||||||

прграмм |

|

|

|

прграмм |

|

|

|

|

|

||||||||||

|

(4000 õ 8) |

$0FFF |

|

|

(4000 õ 8) |

|

|

|

$0FFF |

||||||||||

(32Ê/64Ê õ 16) |

|

|

(32Ê/64Ê õ 16) |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

Внешняя |

$1000 |

|||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

SRAM |

|

||||||||

|

|

|

|

|

|

|

(0 - 64Ê õ 8) |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

$7FFF |

|

|

$7FFF |

|

|

|

|

|

|

|

|

|

|

|

|

$FFFF |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

$FFFF |

|

|

$FFFF |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 7. Конфигурация памяти

6 3

ATMEL |

ÊÒÖ-ÌÊ |

Микроконтроллеры конфигурации B позволяют использовать дополнительную внешнюю память данных. Внешняя память будет адресоваться оставшимся до 64К пространством адресов, т.е. оно будет начинаться следом за пространством адресов встроенной SRAM. При использовании внешней SRAM емкостью 64К буду т потеряны 4К внешней памяти, поскольку адреса этого объема будут зан яты встроенной памятью. При обращении по адресам памяти данных за пределами встро енной SRAM используются те же команды, что для обращения к встроенно й SRAM. При обращеíèè ê âñòроенной памяти данных выводы стробов управления вне шней памятью данных (RD и WR) остаются неактивными во время всего цикла обращения.

Работа внешней SRAM разрешается установкой бита SRE в регистре MCUCR. По сравнению с обращением к встроенной памяти данных, обр ащение к внешней памяти данных требует дополнительного цикла на каждый ба йт. Это означает, что для выполнения команд LD, ST, LDS, STS, PUSH и POP требуется дополнительный так товый цикл. Если стек размещен во внешней SRAM, то прерывания, вызов подпрограмм и возвраты потребуют два дополнительных цикла, поскольку в стеке будет опускаться и подниматься содержимое двухбайтового счетчика команд. Е сли интерфейс с внешней SRAM используется с состоянием ожидания, то на каждый байт не обходимо еще два дополнительных тактовых цикла. Это приводит к следующему эффекту. Командам пересылки данных необходимо два дополнительных тактовы х цикла, тогда как при обработке прерывания, вызове подпрограммы и при возврате из подпрограмм потребуется на четыре тактовых цикла больше, чем это указ ано в описании системы команд.

При адресации памяти данных используются пять режимов ад ресации: непосредственная адресация, косвенная со смещением, косв енная, косвенная с преддекрементом и косвенная с постдекрементом. Регистры с R26 по R31 регистрового файла работают как X, Y и Z регистры указатели косвенной адре сации.

Косвенной адресации со смещением доступны 63 адреса относ ительно базовых адресов, находящихся в регистрах Y или Z. При использовании косвенной адресации с автоматическим преддекрементом и постдекрементом автом атически декрементируются и инкрементируются адреса записанные в регистры X, Y и Z. Всем и этими режимами перекрывается все адресное пространство данных, включая 32 регистра общего назначения и 64 регистра I/O. Подробное описание всех режимов адресации приведено в следующем разделе.

Режимы адресации памяти программ и данных

При обращении к Flash памяти программ и памяти данных (SRAM, регис тровому файлу и памяти I/O) AVR Enhanced RISC микроконтроллерами ATmega603/103 используются мощные и эффективные режимы адресации. В дан ном разделе описываются режимы адресации, поддерживаемые AVR архитект урой. На рисунках OP обозначает часть слова команды, соответствующую операц ионному коду.

6 4