Передатчик hdlc

Функции передатчика:

передача стартового флага

обеспечение режима прозрачности

генерация и передача CRC (если разрешено)

передача конечного флага

Б лок-схема

передатчика.

лок-схема

передатчика.

Передающий FIFO: передающий FIFO состоит из 16-байтного FIFO-буфера, логики определения конца кадра и запросов DMA. Интерфейс SmartDMA использует сигналы счетчиков DMA контроллера.

Интерфейс передающего FIFO: когда передающий FIFO требует данных, он может сгенерировать внешний DMA-запрос или установить бит TDATA1 регистра HxISTAT0 в единицу, при этом вырабатывается маскируемое прерывание.

Предел передающего FIFO: у передающего FIFO есть три уровня запроса данных, обозначаемых полем TTHRSH регистра HxTCON0:

– Доступно все пространство (TTHRSH = 00)

– Доступно 9 байт (TTHRSH = 01)

– Доступно 16 байт (TTHRSH = 10)

При достижении предела генерируется маскируемое влияет на бит TTHRES регистра HxISTAT0).

Transmit-Space Available: при работе в режиме программного I/O, бит TDATA1 регистра HxISTAT0 указывает на возможность записи в передающий FIFO независимо от установленного предела. Для этой цели также возможна выработка маскируемого прерывания.

Переполнение передающего FIFO: при переполнении FIFO генерируется маскируемое прерывание и активизируется режим выброса кадра.

Смена полярности синхроимпульсов для передачи: инициализируется битом TXCINV регистра HxTCON1, независимо от полярности синхроимпульсов приема. Это свойство используется в режиме DCE.

Безотлагательный старт передачи: в этом режиме данные передаются по мере их поступления в FIFO, иначе передача будет проводиться только при половинном заполнении FIFO или при наличии в нем законченного кадра, смотря что будет первым. Для установки безотлагательного режима передачи данных необходимо бит IMSTART регистра HxTCON0 установить в 1.

Генерация флагов или кадров ожидания: это происходит при активном передатчике и отсутствии данных для передачи (включая краевые флаги) или в случае бракования передаваемых пакетов. Определите флаг ожидания установкой бита FLAGIDL регистра HxTCON1 в 1 а кадр ожидания установкой бита FLAGIDL в 0. Флаг имеет вид 7Eh (01111110), последовательность кадра ожидания представляет собой 15 единиц, последовательность выброса: 0 и 7-14 единиц. Для корректной поддержки передачи с временным разделением и с детектированием коллизий передатчик должен быть сконфигурирован на генерацию кадров ожидания. Во время передачи флагов или кадров ожидания передатчик находитсяв idle condition.

Генерация флагов смежных кадров (Back-to-Back Frames): между кадрами генерируются как минимум два флага (закрывающий в конце одного и стартовый в начале следующего, исключая режим прозрачности). Смежные флаги посылаются без вставки нулей (т.e. 0111111001111110, а не 011111101111110).

Генерация последовательности выброса (Abort Generation): передатчик посылает последовательность выброса (0 и 7-14единиц) при установке бита FORABR регистра HxTCON0 в 1 и продолжает передачу до снятия этого бита. Также эта последовательность генерируется если CTS теряется во время передачи кадра или когда передающий FIFO переполняется (исключая прозрачный режим). При работе в режиме GCI или режиме multidrop передатчик отключается после первой же посылки последовательности. Параллельно-последовательный регистр: передаваемые данные из FIFO или генератора флагов/сброса побайтно записываются в параллельно-последовательный регистр сдвиговый регистр и отправляет в канал данные с его выхода. Данные, образующие флаги или последовательности сброса/ожидания следуют на выход минуя логику вставки нулей.

Генерация CRC: CRC или FCS (Frame Check Sequence) содержит сгенерированный CRC-код для передаваемого кадра. Все данные, передаваемые между стартовым и конечным флагами (исключая вставленные нули) участвуют в генерации CRC. Передатчик добавляет CRC к конец кадра перед закрывающим флагом. Поддерживаются следующие алгоритмы генерации: CRC-CCITT, CRC-16 и CRC-32, выбираемые в поле CRCTYPE регистра HxCON. Установка бита CRCDIS регистра HxTCON0 в 1 блокирует генерацию CRC. Запрет генерации CRC можно инвертировать в любое время перед передачей последнего байта кадра. Этот прием используется в режиме programmed I/O дя генерации кадров с CRC чередующихся с кадрами без CRC.

Вставка нулевых битов: логика вставки нулей гарантирует что удаленный приемник не распознает флаг или последовательности ожидания и сброса как данные. Логика вставки нулей просматривает данные между конечными флагами и вставляет нуль после пяти единиц, следующих подряд. Эта функция заблокирована при работе в прозрачном режиме и при генерации флагов и служебных последовательностей.

Разрешение передачи (Transmit Enable): когда передача блокируется, передатчик завершает передачу текущего кадра, ожидает пока не произойдет генерация статуса переданного кадра, затем устанавливает бит стопора передатчика и начинает генерацию флагов или последовательностей в зависимости от конфигурации режима ожидания. Пока передача заблокирована, передатчик продолжает заполнять FIFO. При разблокировке передатчика если передавались флаги ожидания, то передатчик закончит передачу флага а потом начнет передавать данные, в случае, когда передается последовательность ожидания и хотя бы 16 единиц было передано, то данные идут в канал не дожидаясь полной передачи последовательности. Для блокировки передачи надо очистить бит HTEN регистра HxTCON0.

Transmit-FIFO Enable: для нормального функционирования требуется разрешение работы передатчика (бит HTEN регистра HxTCON0) и FIFO передатчика (бит TFIFOEN регистра HxTCON0). Очистка бита TFIFOEN вызывает потерю данных в FIFO.

Состояния вывода: последовательный выход интерфейса DCE (DCE_TXD_x) поддерживает высокоимпендансное состояние (по умолчанию), режим открытого стока и каскадный выход, выбор осуществляется программно. Выход должен быть в режиме открытого стока для корректной работы в multidrop-режиме. Режим задается полем ODRV регистра HxTCON1.

Статус передатчика: после передачи кадра передатчик вырабатывает маскируемое прерывание. При ошибке передачи передатчик стопорится и изменяется содержимое бит FABRST, CTSLST, TUFLO, TGOODF, TSTOP регистра HxISTAT0.

Автоматический режим CTS: при работе в этом режиме передатчик не посылает данные пока не произойдет подтверждение приема сигнала CTS. При прекращении подтверждения CTS во время передачи кадра, происходит т.н. потеря CTS. Передача прекращается и генерируется сигнал abort и маскируемое прерывание. Если при потере CTS передатчик находился в режиме ожидания ничего не происходит. В мультиплексном режиме CTS игнорируется. При отключении этой функции вход CTS игнорируется. Это делается для работы в Multidrop-режиме. Для подключения CTS нужно установить бит AUTOCTS регистра HxTCON1 в 1.

Режим Multidrop с детектированием коллизий: для этого режима выход передатчика заводится на вход CTS. Помимо этого нужно разрешить работу флагов ожидания, отключить CTS и настроить работу выходов контроллера в режиме открытого стока. Канал HDLC задерживает передачу до тех пор пока не зафиксирует запрограммированное число непрерывных единиц на входе CTS. Число единиц определяется в поле TDELAY регистра HxTCON1. Эта процедура снижает риск появления коллизий. При начале передачи передатчик сравнивает поток данных на входе CTS с данными, переданными HDLC. При обнаружении отличий передатчик генерирует прерывание потери CTS, останавливает процесс передачи, начинает передавать флаг ожидания и сбрасывает передающий FIFO. Для активизации этого режима нужно бит MLTDRP оегистра HxTCON1 установить в 1.

Разрешение конфликтов канала GCI D: перед передачей данных передатчик посылает сигнал запроса доступа к каналу. При установке бита GCIDEN регистра HxTCON1 в 1, передача не производится пока передатчик GCI не получит квитирующего сигнала. Если сигналы подтверждения доступа к каналу исчезли во время передачи, передатчик прерывает передачу, начинает транслировать сигналы ожидания, генерирует прерывание и индицирует статус потери CTS. В конце передачи (после закрывающего флага) передатчик перестает запрашивать доступность к каналу.

Порядок передачи битов: возможен порядок следования битов, когда сперва передаются более значимые биты - MSB (Most significant bit) или когда первыми передаются младшие биты - LSB (Least significant bit). Для передачи MSB-first бит TMSBF регистра HxTCON1 устанавливается в 1. Эта возможность используется только в прозрачном режиме.

Прозрачный режим: для его поддержки нужно бит TRANSM регистра HxCON установить в 1. При работе в этом режиме данные передаются как только появляются в FIFO. В этом режиме не производятся вставка нулей, кадрирование флагами и генерация CRC. Применяется для передачи необработанных потоков данных, например аудиоинформации (для работы с кодеками или DSP). Для выполнения byte alignment необходимо синхронизировать передатчик сбрасыванием HDLC после конфигурирования TSA и HDLC. Режим Raw DCE не поддерживает byte alignment. Кроме того byte alignment невозможно если времямультиплексированная шина используется простым каналом TSA/HDLC. Для разрешения работы в режиме прозрачности нужно бит TRANSM регистра HxCON установить в 1.

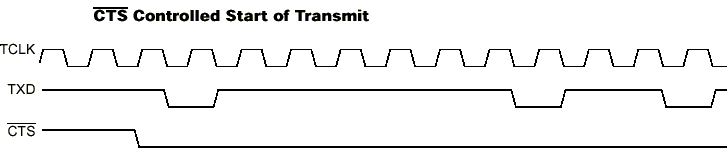

Н а

рисунках 1 и 2 показаны временные диаграммы

передачи с auto-enable CTS.

а

рисунках 1 и 2 показаны временные диаграммы

передачи с auto-enable CTS.

Рис.2

CTS становмтся активным для начала передачи, начинающейся с флага. После флага переданы три бита пока CTS не был распознан как неактивный, после чего на TXD выставился высокий уровень.

Рис.3

Рис.3 показывает другой тип передачи с auto-enable CTS. В конце закрывающего флага CTS становится неактивной. CTS становится неактивной в то же время, когда передается последний бит байта перед флагом, но до следующего бита это не распознается, поэтому потеря CTS не наступает.

Рис.3