HDLC.

В семиуровневой модели Open Systems Interconnection (OSI) второй уровень называется канальным. Он обеспечивает управление между физическими узлами: инициализацию связи, управление потоком данных и контроль ошибки.Одним из протоколов, поддерживающим все эти функции, является High-level Data Link Control (HDLC). Передача данных в HDLC осуществляется в кадрах. Стандарт ISO/IEC 3309 определяет структуру кадра. Микроконтроллер Am186CC обеспечивает поддержку каналов HDLC, которые используются для передачи и приема кадров данных основанных на форматах HDLC.

Кадр HDLC использует флаги для определения начала и конца кадра. Ими же обеспечивается кадровая синхронизация. Один флаг может использоваться для обозначения как конца одного кадра, так и для индикации начала следующего.

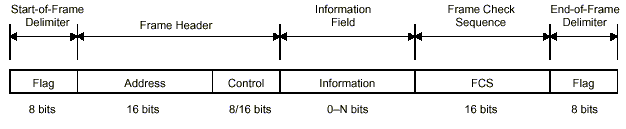

Кадр HDLC содержит флаг старта, адресного поля, контрольного поля, информационной части, контрольное поле информационного блока, (frame checking sequencing - FCS) и флага конца. Особенностью HDLC является вставка нуля после следующих подряд пяти единиц. Приемник отбрасывает ненужные нули после приема кадра.

При

передаче можно запрограммировать

HDLC-контроллер добавлять к информационной

части контрольные биты, причем метод

контроля выбирается пользователем. При

приеме данных HDLC-контроллер выделяет

флаги для распознавания начала и конца

кадров, убирает вставленные биты,

проверяет полученную информацию на

предмет искажений. HDLC-контроллер также

проверяет адресную информацию и может

забраковать пакет, если тот имеет

некорректный адрес.

При

передаче можно запрограммировать

HDLC-контроллер добавлять к информационной

части контрольные биты, причем метод

контроля выбирается пользователем. При

приеме данных HDLC-контроллер выделяет

флаги для распознавания начала и конца

кадров, убирает вставленные биты,

проверяет полученную информацию на

предмет искажений. HDLC-контроллер также

проверяет адресную информацию и может

забраковать пакет, если тот имеет

некорректный адрес.

Микроконтроллер HDLC использует регистры FIFO а обоих направлениях (16-байтный на передачу и 32-байтный на прием) для изолирования запросов данных с системной шины. Контроллер поддерживает режим SmartDMA и программный ввод/вывод данных для заполнения или очистки FIFO. Каждый канал HDLC может присоединяться к внешнему устройству с последовательным приемным интерфейсом напрямую (немультиплексированный режим) или в режиме мультиплексирования (временного уплотнения).

Канал HDLC поддерживают полный дуплексный режим обмена данными со скоростью до 10 Мбит/с при использовании импульсно-кодовой модуляции. Микроконтроллер содержит внутренние регистры для конфигурирования режимов работы, мониторинга и контроля и для передаваемых данных. Каждый HDLC-канал состоит из передатчика, приемника и интерфейса.

Микроконтроллер Am186CC поддерживает 4 канала HDLC: A, B, C и D, которые поддерживают интерфейсы DCE, PCM highway и GCI.

В таблице 1 показаны HDLC/TSA/GCI signals that are multiplexed with other microcontroller functions. Pinstraps are sampled only at external reset and do not affect the pin’s other functions, so they are not shown in this table. Other multiplexed signals, when enabled, either disable or alter any other functions that use the same pin.

Функционирование.

Перед использованием HDLC-каналов требуется предварительная конфигурация мультиплексированных выводов. Для использования HDLC-канала D, необходима установка бита ITF4 в регистре SYSCON.

Конфигурирование контроллера происходит с помощью регистров HxCON, HxTCON0, HxTCON1 и HxRCON1. После этого происходит подключение нужных прерываний установкой надлежащих битов соотретствующих регистров.

Этапы конфигурирования HDLC-каналов:

1. Конфигурирование временных фреймов - Time Slot Assigners (TSAs).

2. Конфигурирование режимов работы HDLC-каналов:

Конфигурирование NRZI-кодирования, прозрачного режима, местных и удаленных заворотов и типа CRC программированием HxCON-регистра.

Для передачи: конфигурирование флага ожидания (между кадрами), порядока следования битов, полярность синхрочастоты (фронт-срез), задержки передачи программированием регистра HxTCON1.

3. Установка необходимых допущений при передаче (регистр HxTXON0) и при приеме (регистр HxRCON0) для каждого HDLC-канала.

4. Сброс для очистки FIFOs и всех битов статуса R/0 кроме статуса прерываний.

5. Очистка битов статуса прерываний установкой 0 в регистр INTSTS.

Интерфейс.

Каналы HDLC работают в одном из двух технический режимах: SmartDMA-режим или programmed I/O. SmartDMA обеспечивает автоматическое перемещение данных в передающий FIFO и из приемного FIFO. Programmed I/O предназначен для низкоскоростной передачи данных, когда у процессора есть возможность побайтной обработки данных.

SmartDma Interface

SmartDMA интерфейс конфигурируется следующими регистрами: HxSTATE, HxISTAT0, HxISTAT1, HxRFS1, HxRFS2, HxRFS3, HxASBMSB, HxASBLSB. SmartDMA-интерфейс автоматически копирует все данные из буферов во внешнюю память.

Programmed I/O Interface

Передача с использованием интерфейса Programmed I/O

Для передачи кадра используя programmed I/O, сперва надо сконфигурировать контрольные регистры,затем подключить передатчик. После этого или использовать разрешающее передачу прерывание для определения моментов, когда возможна передача или пользоваться разрешающим битом в статусном регистре.

После записи последнего байта кадра в передающий FIFO в контрольном регистре устанавливается бит “последнего байта”. После этого HDLC-контроллер добаляет CRC (если разрешено) и закрывающий флаг. Когда последний байт кадра передан, передатчик генерирует маскируемое прерывание и устанавливает бит статуса.

Регистр прерываний показывает были ли искажения переданных данных или прерывалась ли передача кадра. Если это так, то контроллер очищает FIFO и останавливает передатчик до тех пор, пока соответствующий бит статусного регистра не будет очищен.

Приемный интерфейс Programmed I/O

Для приема кадра используя этот интерфейс сначала требуется сконфигурировать контрольные регистры. После этого можно пользоваться или статусными битами или использовать прерывания для определения того что данные находятся в приемном FIFO. Эти данные могут быть считаны из приемного FIFO. Другой бит регистра статуса указывает на конец кадра и возможность его считывания из приемного FIFO. Также вырабатывается маскируемое прерывание. Статусный блок состоит из трех байт: первые два - , третий байт – байт генерального статуса.

Когда выполняется чтение 16-битного слова из FIFO, младший байт содержит данные, а старший указывает что содержится в младшем – данные или какой-либо байт статуса. Старший байт также показывает имеется ли превышение программно заданного порога количества данных и были ли какие-либо прерывания во время передачи.

Получаемый блок статуса содержит следуюшую информацию:

было ли переполнение приемного FIFO

было ли получено не целое число байт

контрольные биты показывают ошибку в принятых данных

адресная информация

слишком длинный (короткий) кадр

приемник был в нерабочем состоянии во время приема хатя бы одного бита

закончился ли фрейм комбинацией сброса (0 после 7…14 единиц подряд)

После приема кадра контроллер перед приемом следующего кадра должен считать информацию статуса из приемного FIFO.

General HDLC Options

Обеспечение основных функций HDLC.

Эти функции актуальны как для приемника, так и для передатчика.

Синхронизация. Каждый HDLC-канал требует два вида синхронизации: для передатчика и для приемника.

HDLC-сброс. Для активизации сброса бит HRESET регистра HxCON устанавливается в 1. При сбросе очищаются каналы HDLC и FIFO, регистры статуса устанавливаются в начальную конфигурацию исключая биты, программируемые пользователем.

NRZ/NRZI-декодирование. Микроконтроллер поддерживает форматы non-return to zero (NRZ), non-return to zero, invert on zero (NRZI). Выбор режима производится установкой бита NRZI регистра HxCON.

Прозрачный режим. Режим прозрачности исключает вставку и удаление нулевых промежуточных битов, генерацию проверочных символов и флагов старта-конца кадра. HDLC-контроллер передает данные сразу после заполнения передающего FIFO. Когда FIFO незаполнен, контроллер генерирует сигналы ожидания (флаги) и не выставляет бит аварии (прерывания передачи). Прозрачный режим также сопровождается отключением счетчика байтов в приемнике, следовательно, не выводятся ошибки очень коротких (длинных) файлов. Byte alignment возможно во всех режимах кроме raw DCE. Для разрешения работы в прозрачном режиме надо установить бит TRANSM регистра HxCON в 1.

Для использования byte alignment при работе в режиме прозрачности при временном уплотнении данных надо установить а затем сбросить бит HRESET регистра HxCON после конфигурирования TSA and HDLC каналов и операций установки. Первый полученный или переданный байт может быть искажен пока HDLC-канал выполняет alignment. Для маскирования этого эффекта на передающей стороне нужно настроить передатчик на использование mark idles и сделать первый переданный байт состоящим из единиц (FFh).

Для поддержки byte alignment ширина временных фреймов должна быть кратна 8 битам и нужен хотя бы один пустой фрейм для точного определения границ байт. Если передающий FIFO переполняется, byte alignment теряется.

Режим дистанционного закольцовывания (Remote Loopback Mode): для активизации этого режима надо установить бит LOOPR регистра HxCON в 1.

Remote Loopback отключает передатчик и отражает данные на последовательном входе на последовательный выход. Приемник в этом режиме работает нормально.

Режим локального закольцовывания (Local Loopback Mode): для активизации этого режима надо установить бит LOOPL регистра HxCON в 1.

Этот режим отсоединяет последовательный вход и присоединяет последовательный выход к приемнику. Последовательный выход может находиться в высокоимпедансном состоянии, режиме открытого коллектора.

Тип CRC: алгоритмы генерации и проверки CRC: CRC-CCIT, CRC-16, или CRC-32. Метод CRC устанавливается полем CRCTYPE регистра HxCON.

Временное разделение каналов (Time Slot Assigner - TSA): каждый HDLC-канал тесно связан с TSA, которое может работать как в мультиплексированном, так и в немультиплексированном режимах. В мультиплексированном вход TXCLK служит входом синхрочастоты; контроллер TSA определяет когда разрешена генерация синхрочастоты. Также с помощью TSA можно уменьшить число бит, передаваемых в 8-битном временном интервале, опустив скорость передачи с 64 Kбит/с до 8 Kбит/с. Это позволяет использовать HDLC-канал для LAP-D или LAP-B, например 56 Kбит/с.