диплом / YmPldQ2

.docРеализация интерфейса Q2 на плате YM120.

Требования к интерфейсу Q2 изложены в файле MorionQ2.doc. В схему интерфейса Q2 на плате YM120 входят микропроцессор (D1 N80C251SB16), контроллер HDLC (D7 MT8952BP), два драйвера RS-485 (D9, D10 MAX487E) и ПЛИС (D3 EPF10k20TC144-4). В ПЛИС реализованы:

-

Кодер NRZI.

-

Декодер NRZI.

-

Схема ФАПЧ (pll64.tdf).

-

Устройство управления передатчиком (q2_slave.tdf).

-

Детектор наличия платы СК120 (ckdetect.tdf).

-

Триггер master.

-

Коммутатор (ym_q2.tdf).

Кодер NRZI реализован на двух триггерах. Первый триггер фиксирует выходные данные МТ8952 по отрицательным перепадам cki2, а второй триггер выдает закодированные данные по положительному перепаду cki2. В соответствии с правилами кодирования выходной лог. Уровень меняется на противоположный при передаче лог. Нуля; при передаче лог. Единицы выходной уроверь не меняется

Декодер NRZI реализован на трех триггерах. Первые два триггера фиксируют два последних принимаемых бита (по отрицательному перепаду cki2). Третий выдает декодированные данные по положительным перепадам cki2 по следующему правилу: если два последних бита равны, значит принята лог. Единица, а если два последних бита не равны, значит принят лог. Нуль.

Схема цифровой ФАПЧ представляет собой генератор на 64кГц (сигнал cki2). Положительные перепады подстраиваются к перепадам (положительным и отрицательным) входного сигнала. Для того, чтобы из входного сигнала можно было извлекать синхронизацию применено кодирование NRZI. ФАПЧ состоит из детектоа фронтов входного сигнала, корректора фазы, схемы коррекции задержки тактирования, вычисления ошибки по фазе и схемы вычисления величины коррекции по фазе (которая представляет собой цифровой интегратор ошибки по фазе). Корректор фазы представляет собой сумматор текущей фазы внутреннего генератора (берется с выходов счетчика битов и таймслотов) и вычисленной ошибки по фазе.

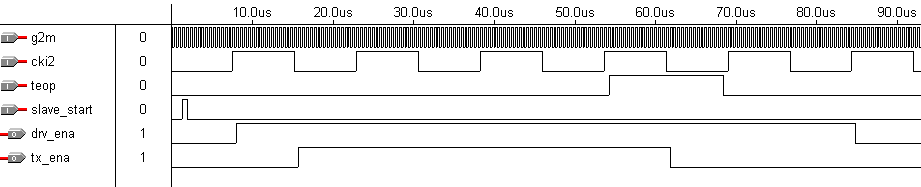

Модуль q2slave.tdf служит для синхронизации 1) микропроцессора 2) передатчика МТ8952 и 3) драйвера, подключающего передатчик к общей шине ( ym_to_ck или SRS (Slave ReSponse) ). Для запуска передатчика МП производит запись по адресу 00:FFE0h произвольного байта. Из имульса записи формируется сигнал slave_start, который и запускает автомат синхронизации. По ближайшему положительному перепаду cki2 формируется drv_ena для включения драйвера. Через половину периода cki2 появляется сигнал tx_ena, включающий передатчик МТ8952, а еще через половину периода cki2 МТ8952 начинает передачу первого бита.

В конце передачи пакета МТ8952 выставляет сигнал teop. Этот сигнал стробируется по отрицательному перепаду cki2 и выключает разрешение передачи tx_ena. Драйвер отключается еще через полтора периода, позволяя последнему биту пройти через кодер NRZI.

-

g2m синхронизация 2048кГц.

-

cki2 синхронизация МТ8952 64кГц.

-

teop – Transmit End Of Packet (выход МТ8952).

-

slave_start – запуск передатчика вторичной станции(slave) от МП.

-

drv_ena – Driver Enable. Подключение выхода МТ8952 к общей шине.

-

tx_ena - Transmit Enable. Разрешение передачи для МТ8952.

Детектор наличия платы СК120 (ckdetect.tdf) фиксирует отсутствие платы СК120 если логический уровень сигнала ym_to_ck не меняется в течение 32 битовых интервала.

Триггер master устанавливается программно по адресу 00:FFE1h в соответствии с разрядом D[0] шины данных.

Коммутатор управляет работой перечисленных блоков в зависимости от режима станции по интерфейсу Q2. Кроме двух стандартных режимов (первичная или вторичная станция) предусмотрен дополнительный режим, когда первичной станцией является плата СК-120. В этом случае YM120 работает как вторичная станция, за исключением того, что ее драйверы используются платой СК120 как это принято для первичной станции. Плата СК120 общаетя с платой YM120 с помощью сигналов TTL уровнями ck_to_ym и ym_to_ck. Перевод в этот дополнительный режим осуществляется сигналом ck_main, который вырабатывает детектор наличия платы СК120 (ckdetect.tdf). При этом состояние триггера master игнорируется.

При отсутствии сигнала ck_main режим определяется триггером master. В единичном состоянии этого триггера устанавливается режим первичной станции, иначе – вторичной.

В режиме первичной станции отключается ФАПЧ (по входу запрета pll_ban) модуля pll64k. Передатчик МТ8952 постоянно включен сигналом txce2=0, вне зависимости от сигнала tx_ena модуля q2_slave. Драйвер D9 шины MRQ(Master ReQuest) постоянно включен на передачу сигналом mde=1. Выход передатчика через кодер NRZI и драйвер D9 подключен к шине MRQ. Драйвер шины SRS постоянно включен на прием сигналом sde=0. При этом данные от других станций с шины SRS проходят через приемник драйвера D10, два мультиплексора и декодер NRZI на вход приемника МТ8952.

В режиме вторичной станции драйвер D9 шины MRQ постоянно включен на прием сигналом mde=0, И данные на вход приемника поступают уже с шины MRQ. Хотя выход передатчика (через кодер NRZI) постоянно соединен со входом драйвера D10 шины SRS, разрешение передачи на эту шину возможно только в этом режиме. Причем сигнал разрешения drv_ena формируется модулем q2_slave по команде от микропроцессора. Вместе с сигналом drv_ena формируется сигнал tx_ena для разрешения работы передатчика, как описано выше. Таким образом обеспечивется доступ к шине SRS нескольких вторичных станций.