- •Аннотация

- •1.1. Прототип модуля

- •1.2. Структура иерархического проекта

- •1.3. Иерархическое описание накапливающего сумматора.

- •Variable tr[8..1] : dff;

- •Variable tr[9..1] : dff;

- •Include "rg_a.Inc";

- •Include "add.Inc";

- •Include "rg_out.Inc";

- •Variable

- •2. Проектирование схем двоично-десятичной арифметики.

- •2.1. Двоично-десятичное представление схем.

- •2.2. Двоично-десятичный сумматор

- •Variable

- •2.2. Двоично-десятичный вычитатель

- •Variable

- •2.3. Двоично-десятичные счетчики

- •3.1. Способы задания абстрактных автоматов.

- •3.2. Описание работы автоматов на языке ahdl

- •Init, Working, Waiting, Resuming, Ending.

- •Variable

- •3.3. Проектирование счетчиков на базе абстрактных автоматов

- •Variable

- •4. Проектирование типовых схемотехнических узлов

- •Дешифратора

- •Считается, что одновременно может быть нажата только одна кнопка клавиатуры.

- •Variable

- •4.2. Схемы вычисления функций

- •4.3. Счетчики расхода, пробега

- •Variable

- •Variable

- •Include "t210.Inc";

- •Variable

- •4.4. Узлы обработки сигналов локаторов

- •Include "t210.Inc";

- •Variable

- •4.5. Часы, счетчики времени, календари

- •Variable

- •Variable

- •4.6. Частотомеры

- •Variable

- •4.7. Умножители

- •Input_b_is_constant)

- •5 Проектирование схем с магистральным вводом выводом данных

- •5.1 Правила работы с магистралью, арбитр.

- •Variable

- •5.2 Подготовка временных диаграмм.

- •5.3. Пример сумматора с магистральным вводом-выводом данных.

- •Variable

Variable

TRI_B[2..1]:TRI;

TRI_OUT[2..1]:TRI;

BEGIN

CASE (CS,ADR) IS

WHEN B”10” => TRI_OUT[].OE=VCC;

WHEN B”11” => TRI_B[].OE=VCC;

END CASE;

TRI_B[].IN=IN[];

TRI_OUT[].IN=DB[];

DB[]=TRI_B[].OUT;

OUT[]=TRI_OUT[].OUT;

END

В приведённом текстовом описании выводы группы DB[2..1] имеют тип BIDIR.

В разделеVARIABLE объявлены две переменные TRI_B и две переменные TRI_OUT каждая из которых обозначает примитив буфера с тремя состояниями TRI.

Таким образом, компилятору явно указывается, что на соответствующих выводах БИС следует использовать буферы с тремя состояниями.

Выводы CS и ADR образуют временную группу, оцениваемую в операторе CASE. Заметим, что при CS=0 и произвольном сигнале на входе ADR, значения логических функций TRI_B[] и TRI_OUT[] явно не определены.

По умолчанию их значения на данных наборах аргументов – логический нуль. Поэтому при CS=0 все буферы TRI будут находится в состоянии «Z».

Комбинационная схема, имеющая управляющие входы CS и ADR и управляющая логикой работы с магистралью фактически является арбитром.

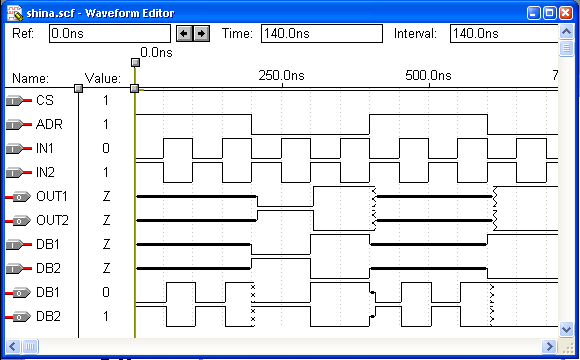

Результаты моделирования приёмопередатчика приведены на рис 5.1.3.

Рис 5.1.3. Результаты моделирования работы приёмопередатчика.

5.2 Подготовка временных диаграмм.

При подготовке временных диаграмм для моделирования магистральных устройств, следует учитывать, что двунаправленные выводы БИС присутствуют на временной диаграмме дважды: как входы и как выходы.

Поэтому на временной диаграмме, представленной на рис 5.1.3. группа отображена и как группа входов DB[2..1] так и как группа выходов DB[2..1].

Данные, поступающие на входную шину, помещаются на входную шину и при моделировании автоматически отображаются на выходной шине DB[2..1]. Данные, снимаемые с двунаправленной шины, отображаются на выходной шине, при этом входная шина должна быть в состоянии отключено «Z».

На временной диаграмме состояние «Z» отображается жирной линией, расположенной посредине между уровнем логического «0» и уровнем логической «1».

Отметим, что если в процессе вывода данных из БИС на двунаправленную шину не перевести соответствующий ей входной сигнал в состояние «Z» возникнет конфликт сигналов между входным драйвером и выходным усилителем БИС, что приведёт при моделировании работы схемы к появлению сигналов неопределённости «X», которые отображаются на временной диаграмме в виде сетки.

5.3. Пример сумматора с магистральным вводом-выводом данных.

Рассмотрим схему сумматора с магистральным вводом-выводом данных представленную на рис 5.2.1.

Сумматор

A

S

B

Регистр

A

M

M

Регистр

B

Арбитр

DON

DON

Рис 5.2.1 Структурная схема сумматора с магистральным вводом-выводом данных.

Представленная схема сумматора имеет следующие входные и выходные сигналы:

M[8..1] – восьмиразрядная двунаправленная магистраль;

CLC – вход тактового сигнала;

DON – выход сигнала окончания формирования суммы;

Работа схемы осуществляется в три такта:

на первом такте происходит считывание с магистрали M первого слагаемого и запись в регистр A;

на втором такте происходит считывание с магистрали M второго слагаемого и запись в регистр B;

на третьем такте происходит вычисление суммы и выдача результата на магистраль M.

Работой схемы управляет арбитр, обеспечивающий корректную работу с магистралью.

Рассмотрим поведенческое описание работы восьмиразрядного сумматора с магистральным вводом-выводом данных.

SUBDESIGN MSUM

(

CLK: INPUT;

M[7..0] : BIDIR;

DONE : OUTPUT;

)