Allen and Holberg - CMOS Analog Circuit Design

.pdf

Allen and Holberg - CMOS Analog Circuit Design |

Page III.2-1 |

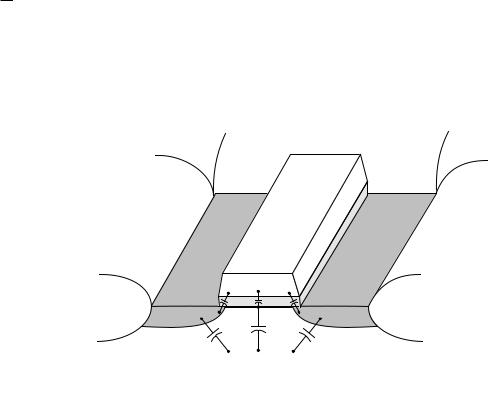

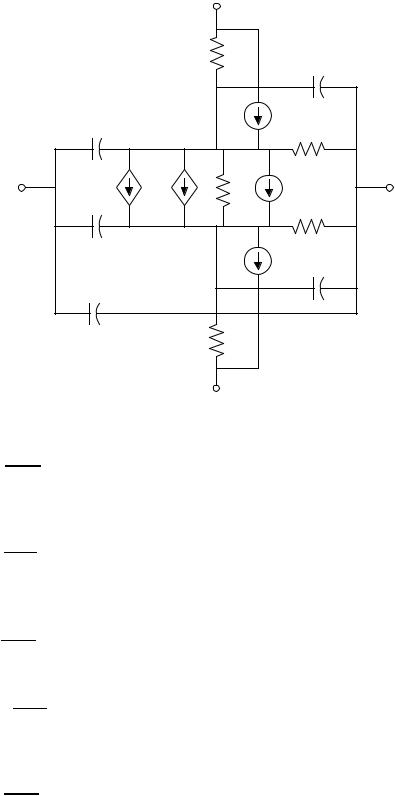

INTRINSIC CAPACITORS OF THE MOSFET

Types of MOS Capacitors

1.Depletion capacitance (CBD and CBS)

2.Gate capacitances (CGS, CGD, and CGB)

SiO2

|

|

Gate |

|

Source |

|

Drain |

|

C1 |

|

C2 |

C3 |

|

|

|

|

|

|

C4 |

|

C |

BS |

|

CBD |

|

|

|

|

Bulk

Figure 3.2-4 Large-signal, charge-storage capacitors of the MOS device.

Allen and Holberg - CMOS Analog Circuit Design |

Page III.2-2 |

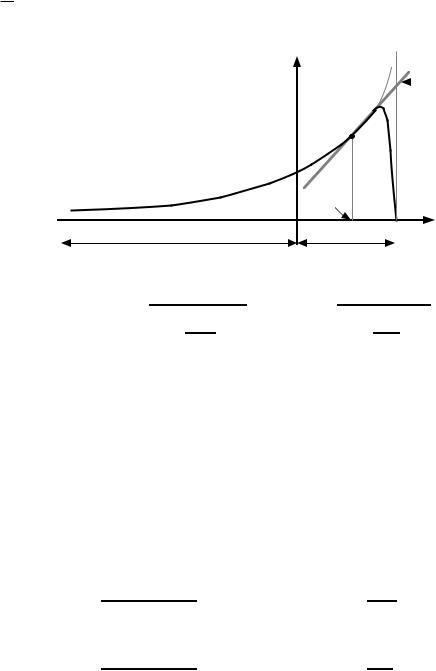

Depletion Capacitors

Bulk-drain pn junction -

CBD

Capacitance approximation for strong forward bias

CBD0xArea

|

|

|

|

|

|

|

|

. |

φ |

|

|

|

|

||

|

|

|

|

|

|

(FC) |

|

|

|

|

|||||

|

|

|

|

|

|

|

B |

|

|

|

VBD |

||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Forward |

|

φB |

||||||

|

Reverse Bias |

|

|||||||||||||

|

|

|

|

|

|

Bias |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

CBD0 ABD |

|

|

|

|

|

|

CBS0 ABS |

|||||||

CBD = |

|

vBD MJ |

andCBS = |

vBS MJ |

|||||||||||

|

|

− |

|

|

|

|

|

|

|||||||

|

1 |

|

|

|

|

|

|

1 − |

φ |

|

|||||

|

|

|

φ B |

|

|

|

|

|

|

B |

|||||

where,

ABD (ABS) = area of the bulk-drain (bulk-source)

φΒ = bulk junction potential (barrier potential)

MJ = bulk junction grading coefficient ( 0.33 ≤ MJ ≤ 0.5)

For strong forward bias, approximate the behavior by the tangent to the above CBD or CBS curve at vBD or vBS equal to (FC)·φ B.

CBD = |

CBD0ABD |

|

vBD |

, |

vBD > (FC)·φ B |

||

|

1 |

− (1+MJ)FC + FC |

|

||||

|

(1+FC)1+MJ |

|

φB |

|

|

||

and |

CBS0ABS |

|

vBS |

|

|

||

CBD = |

, |

vBS > (FC)·φ B |

|||||

|

1 |

− (1+MJ)FC + FC |

|

||||

|

(1+FC)1+MJ |

|

φB |

|

|

||

Allen and Holberg - CMOS Analog Circuit Design |

Page III.2-3 |

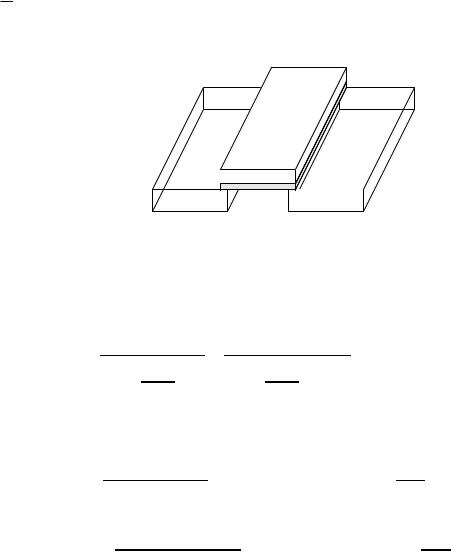

Bottom & Sidewall Approximations

Polysilicon gate |

|

|

|

H |

G |

|

D |

C |

|

|

|

Source |

Drain |

|

|

F |

|

E |

|

|

A |

B |

|

SiO2 |

|

|

Bulk |

|

|

Drain bottom = ABCD

Drain sidewall = ABFE + BCGF + DCGH + ADHE

CBX =

and

CBX =

vBX ≥

where

|

(CJ)(AX) |

+ |

(CJSW)(PX) |

, vBX ≤ (FC)(PB) |

||||

|

|

v |

|

|

v |

|

||

|

− |

|

BX MJ |

|

− |

|

BX MJSW |

|

1 |

PB |

1 |

PB |

|

||||

|

|

|

|

|

||||

|

(CJ)(AX) |

|

|

|

v |

|

|

|

|

− (1 + MJ)FC + MJ |

|

BX |

|

||

(1 − FC)1+MJ |

1 |

PB |

|

||||

|

(CJSW)(PX) |

|

|

|

vBX |

|

|

+ |

(1 − FC)1+MJSW |

1 |

− (1 + MJSW)FC + PB |

(MJSW) , |

|||

(FC)(PB)

AX = area of the source (X = S) or drain (X = D)

PX = perimeter of the source (X = S) or drain (X = D) CJSW = zero-bias, bulk-source/drain sidewall capacitance MJSW = bulk-source/drain sidewall grading coefficient

Allen and Holberg - CMOS Analog Circuit Design |

Page III.2-4 |

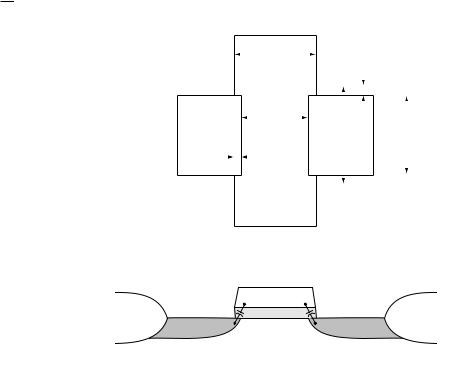

Overlap Capacitance

|

|

|

|

|

|

|

|

Mask L |

|

|

Oxide encroachment |

||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

Actual |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

L (Leff) |

|

|

|

|

Mask |

Actual |

|||||||

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

W (Weff) |

|||||||

LD |

W |

||||||||||||||||||||

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Gate

Source-gate overlap |

Drain-gate overlap |

capacitance CGS (C1) |

capacitance CGD (C3) |

|

Gate |

FOX |

FOX |

Source |

Drain |

|

Bulk |

C1 = C3 (LD)(Weff)Cox = (CGXO)Weff

Allen and Holberg - CMOS Analog Circuit Design |

Page III.2-5 |

Gate to Bulk Overlap Capacitance

Overlap |

Overlap |

C5 |

Gate |

C5 |

FOX |

FOX |

Source/Drain |

|

|

|

|

|

|

|

|

Bulk |

|

On a per-transistor basis, this is generally quite small

Channel Capacitance

C2 = Weff(L − 2LD)Cox = Weff(Leff)Cox

Drain and source portions depend upon operating condition of transistor.

Allen and Holberg - CMOS Analog Circuit Design |

Page III.2-6 |

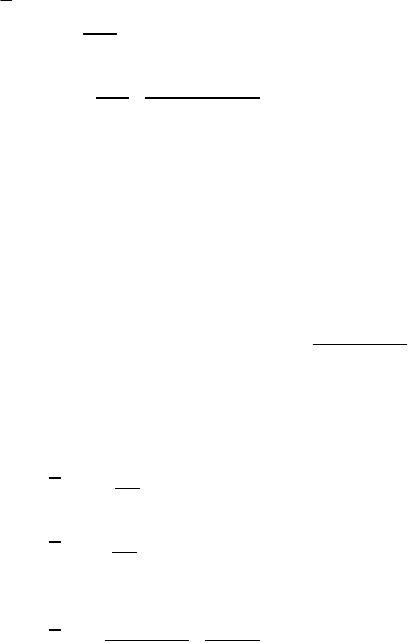

MOSFET Gate Capacitance Summary:

Capacitance |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||||||

C2 + 2C5 |

|

|

|

|

C |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||||

C |

|

+ |

2 |

|

|

|

|

|

GS |

|

|

|

|

|

|

|

1 |

_ C |

2 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

||

C |

|

+ |

1 |

|

|

|

|

|

|

|

|

C |

GS |

, C |

GD |

|

1 |

_ C |

2 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

vDS = constant |

|

||

|

|

|

|

|

|

|

CGS, CGD |

|

CGD |

|

|

vBS = 0 |

|

|||

|

|

C1, C3 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

CGB |

|

|

|

|

|

|

||||

|

|

|

2C5 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Off |

|

Saturation |

|

|

|

Non- |

vGS |

|||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

VT |

|

|

vDS +VT |

Saturation |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

iD

vDS = vGS - VT

Non-Sat

Region

Saturation

Region

|

|

|

Cutoff Region |

|

|

0 |

0.5 |

1.0 |

1.5 |

2.0 |

2.5 |

0 |

|||||

|

vDS = |

constant |

|

|

|

Allen and Holberg - CMOS Analog Circuit Design |

Page III.2-7 |

CGS, CGD, and CGB

Off

CGB = C2 + 2C5 = Cox(Weff)(Leff) + CGBO(Leff)

CGS = C1 Cox(LD)(Weff) = CGSO(Weff)

CGD = C3 Cox(LD)(Weff) = CGDO(Weff)

Saturation

CGB = 2C5 = CGBO (Leff)

CGS = C1 + (2/3)C2 = Cox(LD + 0.67Leff)(Weff)

= CGSO(Weff) + 0.67Cox(Weff)(Leff)

CGD = C3 Cox(LD)(Weff) = CGDO(Weff)

Nonsaturated

CGB = 2C5 = CGBO (Leff)

CGS = C1 + 0.5C2 = Cox(LD + 0.5Leff)(Weff)

= (CGSO + 0.5CoxLeff)Weff

CGD = C3 + 0.5C2 = Cox(LD + 0.5Leff)(Weff)

= (CGDO + 0.5CoxLeff)Weff

Allen and Holberg - CMOS Analog Circuit Design

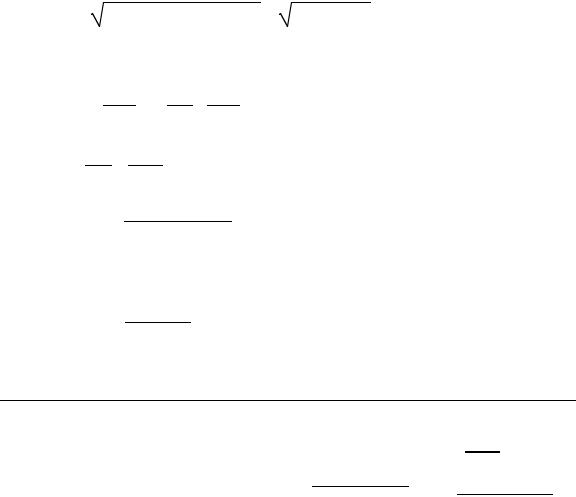

Small-Signal Model for the MOS Transistor

|

|

|

|

D |

|

|

|

|

|

|

|

|

rD |

Cbd |

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

inrD |

|

|

|

Cgd |

|

|

|

|

|

|

|

|

gmvgs |

|

|

|

gds |

|

gbd |

||

|

|

|

|

|

|

|||

G |

|

|

|

|

inD |

|

|

|

|

|

|

|

|

|

|

|

|

Cgs |

g |

v |

bs |

|

|

|

g |

bs |

|

|

mbs |

|

|

|

|

||

|

|

|

|

|

inrS |

C |

bs |

|

Cgb |

|

|

|

r |

S |

|

|

|

|

|

|

|

S |

|

|

|

|

Figure 3.3-1 Small-signal model of the MOS transistor.

gbd = ∂IBD (at the quiescent point) 0

∂VBD

and

gbs = ∂IBS (at the quiescent point) 0

∂VBS

The channel conductances, gm, gmbs, and gds are defined as

gm = ∂ID (at the quiescent point)

∂VGS

gmbs = ∂∂VIDBS (at the quiescent point)

and

g = ∂ID (at the quiescent point) ds ∂VDS

Page III.3-1

B

Allen and Holberg - CMOS Analog Circuit Design |

Page III.3-2 |

||||||||||

Saturation Region |

|

|

|

|

|

|

|

||||

gm = |

|

(2K'W/L)| ID|(1 + λ VDS) (2K'W/L)|ID| |

|

||||||||

|

|

= |

−∂I |

|

∂I |

|

∂V |

|

|

||

g |

mbs |

∂V |

|

D |

= − |

D |

|

T |

|

||

|

|

SB |

∂V |

∂V |

SB |

|

|||||

|

|

|

|

|

|

T |

|

||||

Noting that |

∂ID = |

−∂ID , we get |

|

|

|

||||||

|

∂VT |

|

∂VGS |

|

|

|

|

|

|||

|

|

|

|

|

|

γ |

|

|

|

|

|

gmbs = gm 2(2|φF| + VSB)1/2 = η gm |

|

||||||||||

gds = go = |

|

ID λ |

|

ID |

λ |

|

|||||

|

|

|

|

||||||||

|

|

|

|

|

1 + λ VDS |

|

|

|

|||

Relationships of the Small Signal Model Parameters upon the DC Values of Voltage and Current in the Saturation Region.

Small Signal |

DC Current |

DC Current and |

DC Voltage |

Model Parameters |

|

Voltage |

|

gm |

(2K' IDW/L)1/2 |

_ |

2K' W(VGS -VT) |

|

|

|

L |

gmbs |

|

γ (2IDβ)1/2 |

γ ( β (VGS −VT) ) |

|

|

2(2|φF | +VSB) 1/2 |

2(2|φF | + VSB)1/2 |

|

|

|

|

gds |

λ ID |

|

|

Allen and Holberg - CMOS Analog Circuit Design |

Page III.3-3 |

Nonsaturation region

gm = ∂Id = β VDS

∂VGS

gmbs = |

∂ID |

= |

βγVDS |

|

∂VBS |

|

2(2|φF | + VSB)1/2 |

and

gds = β(VGS − VT − VDS)

Relationships of the Small-Signal Model Parameters upon the DC Values of Voltage and Current in the Nonsaturation Region.

|

|

|

|

|

|

|

|||

|

|

|

Small Signal |

|

|

DC Voltage and/or Current |

|||

|

|

Model Parameters |

|

Dependence |

|||||

|

gm |

|

|

|

|

|

|

= β VDS |

|

|

gmbs |

|

|

|

|

|

β γ VDS |

||

|

|

|

|

|

|

|

|

|

2(2|φF | +VSB)1/2 |

|

gds |

|

|

|

|

|

|

= β (VGS −VT −VDS) |

|

Noise |

|

|

|

|

|

|

|

|

|

2 |

|

|

4kT |

|

(A2) |

|

|

||

i nrD = |

|

rD |

|

f |

|

|

|||

|

|

|

|

|

|

|

|

|

|

2 |

|

|

4kT |

|

(A2) |

|

|

||

i nrS = |

|

|

f |

|

|

||||

|

|

|

rS |

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

i nD2 = |

8kT g |

|

(1+η) |

(KF )I |

|

|

|||

|

|

m |

|

+ |

D |

|

f (A2) |

||

|

|

|

|

3 |

|

|

f Cox L2 |

|

|