- •Организация эвм и систем

- •Глава 1 эвм общего назначения

- •Структура эвм общего назначения.

- •Арифметико-логические устройства.

- •Устройства управления.

- •Risc и cisc процессоры.

- •1.5 Форматы машинных команд.

- •Inc byte ptr [40h] – одноадресная

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Глава 2

- •2.1 Микропроцессор к1810вм86.

- •2.2 Назначение входов/выходов вм86 в минимальном режиме.

- •2.3 Назначение входов/выходов вм86 в максимальном режиме.

- •Внутренняя архитектура мп вм86.

- •Сегментация памяти.

- •2.6 Программная модель мп вм86.

- •2.7 Организация оперативной памяти.

- •2.8 Организация адресного пространства портов ву.

- •2.9 Методы обмена информацией между мп и портами ву.

- •2.10 Параллельный программируемый адаптер к1810вв55 (i8255).

- •Пример использования и программирования адаптера

- •2.12 Программируемый таймер к1810ви54 (i8254).

- •2.13 Пример использования таймера.

- •2.14 Обработка прерываний.

- •2.15 Система прерываний вм86.

- •2.16 Контроллер прерываний к1810вн59 (i8259).

- •Дополнительная информация о настройке вн59.

- •Прямой доступ к памяти.

- •Программирование кпдп вт37

- •2.21 Организация процессорного модуля вм86.

- •2.20. Организация шинного интерфейса в максимальном режиме

- •2.23. Слабо связанные конфигурации.

- •2.24. Арбитр шин к1810вб89 (i8289).

- •2.25 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •2.26. Формат машинной команды вм86.

2.24. Арбитр шин к1810вб89 (i8289).

Данные микросхемы используются в многопроцессорных системах, в которых несколько процессоров разделяют между собой системную шину. При этом схемы арбитража должны разрешать конфликтные ситуации, возникающие при одновременной попытке доступа к СШ со стороны нескольких процессоров.

Каждому процессору, имеющему доступ к СШ, ставится в соответствие свой арбитр шин. В его задачу входят следующие действия:

арбитр должен определить, нуждается ли «его» процессор в системной шине, и, если нуждается, обеспечить ему доступ к шине;

доступ процессора к шине арбитр обеспечивает, вырабатывая активный (нулевой) сигнал на своем выходе AEN. Этот сигнал заводится на одноименный вход системного контроллера ВГ88, входящего в состав шинного интерфейса (см. два предыдущих раздела), и тем самым подключает процессор к системной шине;

Если системная шина свободна или занята процессором с более низким приоритетом, арбитр обеспечит доступ к шине практически сразу. Если же шина занята процессором с более высоким приоритетом, арбитр будет вынужден ждать, пока не наступят условия освобождения шины. Вместе с арбитром в этом случае должен ждать и процессор. Для того чтобы заставить процессор ожидать какое-либо событие, надо сформировать нулевой сигнал на его вход READY. Для этих целей сигнал с выхода AEN арбитра заводится на вход AEN1 (или AEN2) генератора ГФ84. В результате ГФ84 будет формировать нулевой сигнал READY, во всяком случае до тех пор, пока сигнал на выходе AEN арбитра будет оставаться пассивным.

Рис.

36

Рис.

36

Захватив шину, арбитр никогда ее не освобождает по собственной инициативе. Освобождение шины происходит либо при общем сбросе системы, либо по запросу от другого арбитра. Причем в последнем случае арбитр освобождает шину только если соблюдаются так называемые условия освобождения.

На рис 37 показано стандартное подключение микросхемы ВБ89.

Рис. 37

Далее вкратце рассмотрим назначение входов/выходов арбитра ВА86.

S2 – 0 - на эти входы заводятся сигналы состояния, характеризующие цикл шины, который выполняет МП (см. табл. 2). По этим сигналам арбитр определяет, нуждается ли МП в шине или нет.

CLK – импульсы, поступающие на этот вход с одноименного выхода генератора ГФ84, синхронизирует работу арбитра и МП.

BCLC (bus CLK) – на этот вход подаются импульсы с генератора шины. Входы BCLK всех арбитров объединяются между собой. Вход служит для синхронизации работы всех арбитров в системе.

INIT - инициализация (сброс). Этот сигнал заводится на все арбитры системы и после его поступления шина будет свободна.

Пока на входе LOCK арбитра стоит активный сигнал, арбитр ни при каких условиях не отдаст шину другому арбитру.

ANYRQST – «любой запрос». Если на этом входе активный сигнал, арбитр отдает шину по любому запросу от другого арбитра.

CBRQLCK - «блокировать вход CBRQ». Этот сигнал запрещает арбитру отдавать шину по запросам с более низким приоритетом.

AEN – активный сигнал на этом выходе означает, что арбитр обеспечил «своему» МП доступ к системной шине.

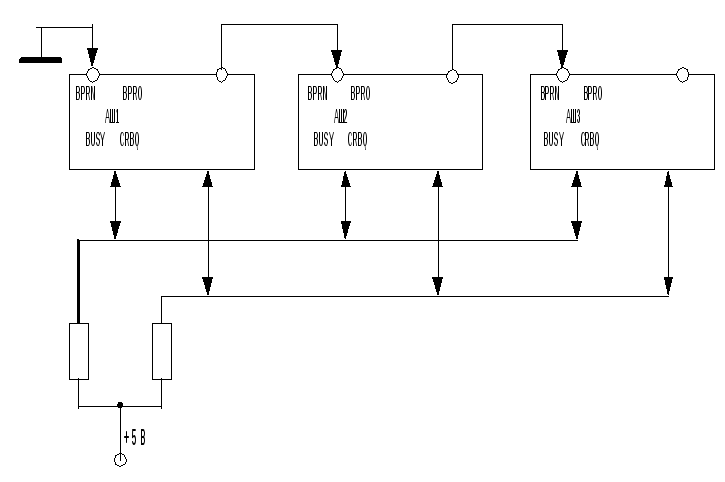

Для предотвращения конфликтов из-за доступа к СШ всем арбитрам в системе присваивается приоритет. Возможны разные схемы обработки приоритетов. Наиболее простой является последовательная обработка приоритетов (рис. 38). Здесь АШ – арбитр шин.

Рис

38

Рис

38

Если на входе BPRN (bus priority in) АШ стоит единичный сигнал, это означает, что шину удерживает арбитр с более высоким приоритетом. При этом АШ вырабатывает единичный сигнал на выходе BPRO (bus priority out), то есть передает эту информацию менее приоритетным арбитрам (см. рис 39)

Если АШi потребуется шина и на его входе BPRN стоит нулевой сигнал, этот АШ получит доступ к шине. При этом АШi вырабатывает единичный сигнал на своем выходе BPRO, запрещая доступ к шине арбитрам с более низким приоритетом. Очевидно, что таким путем можно получить доступ к СШ если она свободна или удерживается арбитром с более низким приоритетом.

Пусть АШi требуется доступ к шине, а последняя удерживается арбитром с более высоким приоритетом, то есть на входе BPRN АШi стоит единица. В этом случае АШi выставляет активный (нулевой) сигнал на линию CBRQ (common bus request –«общий запрос шины»), сообщая тем самым арбитру, удерживающему шину, что шина требуется арбитру с более низким приоритетом. При этом удерживающий шину арбитр освободит последнюю, если наступят условия освобождения шины. Рассмотрим далее условия освобождения и удержания шины арбитром АШi:

LOCK = 0 – удержание шины;

LOCK = 1, BPRN = 1 – безусловное освобождение шины;

LOCK = 1, BPRN = 0, ANYRQST = 1, CBRQ = 0 – безусловное освобождение шины;

LOCK = 1, CBRQLCK = 0, CBRQ = 0 – удержание шины;

LOCK = 1, BPRN = 0, CBRQLCK = 1, CBRQ = 0 – условное освобождение шины.

При условном освобождении удерживающий шину арбитр освободит ее когда «его» процессор начнет выполнять команду hlt или nop.

Когда АШi получает доступ к шине, он выставляет нулевой сигнал на линию BUSY («занят»), сообщая другим арбитрам, что шина занята.

Схема последовательной обработки приоритетов (рис. 38) не требует дополнительного оборудования, однако имеет существенный недостаток, заключающийся в том, что в цепочку можно соединить не более трех арбитров. Для устранения этого недостатка используются более сложные схемы параллельной обработки приоритетов, в которых задействуются выходы BREQ (bus request – «запрос шины») арбитров. При этом в систему приходится вводить внешние логические схемы, которые и обеспечивают параллельную обработку приоритетов.

Сигналы на выходах IOB (input-output bus), RESB (residential bus) и SYSB/RESB (system bus / residential bus) задают конфигурацию системы. В соответствии с ними арбитр трактует сигналы на входах S2-S0, определяя нуждается «его» МП в шине или нет. Наиболее часто используются следующие конфигурации:

IOB = 1, RESB = 0 (SYSB/RESB – безразлично) – МП, которому соответствует данный арбитр, работает только с системной шиной (см. рис. 34);

IOB = 0, RESB = 0, SYSB/RESB = 0 – МП работает с СШ и РШВВ. К какой из этих шин обращается МП, арбитр определяет по сигналу на входе S2. При S2=0 – к РШВВ, при S2 = 1 – к СШ ( см. табл. 2).

IOB = 1, RESB = 1 –МП работает с СШ и РШ. К какой из этих шин обращается МП, определяет сигнал на входе SYSB/RESB (SYSB/RESB =1 – к СШ, SYSB/RESB = 0 – к РШ). Этот сигнал снимается с выхода дешифратора адреса (см. рис 35).