- •Организация эвм и систем

- •Глава 1 эвм общего назначения

- •Структура эвм общего назначения.

- •Арифметико-логические устройства.

- •Устройства управления.

- •Risc и cisc процессоры.

- •1.5 Форматы машинных команд.

- •Inc byte ptr [40h] – одноадресная

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Глава 2

- •2.1 Микропроцессор к1810вм86.

- •2.2 Назначение входов/выходов вм86 в минимальном режиме.

- •2.3 Назначение входов/выходов вм86 в максимальном режиме.

- •Внутренняя архитектура мп вм86.

- •Сегментация памяти.

- •2.6 Программная модель мп вм86.

- •2.7 Организация оперативной памяти.

- •2.8 Организация адресного пространства портов ву.

- •2.9 Методы обмена информацией между мп и портами ву.

- •2.10 Параллельный программируемый адаптер к1810вв55 (i8255).

- •Пример использования и программирования адаптера

- •2.12 Программируемый таймер к1810ви54 (i8254).

- •2.13 Пример использования таймера.

- •2.14 Обработка прерываний.

- •2.15 Система прерываний вм86.

- •2.16 Контроллер прерываний к1810вн59 (i8259).

- •Дополнительная информация о настройке вн59.

- •Прямой доступ к памяти.

- •Программирование кпдп вт37

- •2.21 Организация процессорного модуля вм86.

- •2.20. Организация шинного интерфейса в максимальном режиме

- •2.23. Слабо связанные конфигурации.

- •2.24. Арбитр шин к1810вб89 (i8289).

- •2.25 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •2.26. Формат машинной команды вм86.

МИНИСТЕРСТВО ОБЩЕГО И ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ

РОССИЙСКОЙ ФЕДЕРАЦИИ

Организация эвм и систем

Учебное пособие

Данное учебное пособие представляет из себя конспект лекций по курсу «Организация ЭВМ и систем». Целью курса является подробное знакомство студентов с особенностью организации современных микропроцессоров, ЭВМ и ПЭВМ, освоение ими аппаратных и аппаратно-программных решений, используемых при создании подсистем и узлов вычислительных устройств.

Пособие может быть рекомендовано для изучения студентам специальностей:

22.01, 22.04, 22.06 и другим.

Глава 1 эвм общего назначения

Структура эвм общего назначения.

Любая ЭВМ содержит два основных блока:

центральный процессор (ЦП);

оперативную память (ОП).

Задачей ЦП является выполнение машинных команд, которые он выбирает из ОП. Внутренняя организация различных ЦП может серьезно отличаться друг от друга, однако любой ЦП содержит ряд стандартных блоков. К ним относятся:

дешифратор команд, позволяющий декодировать считанную из ОП команду;

арифметико-логическое устройство (АЛУ), позволяющее реализовать заданную в команде операцию;

блок регистров общего назначения (блок РОН), предназначенных для временного хранения информации. Наличие РОН позволяет резко снизить количество обращений к ОП, повышая тем самым общее быстродействие ЭВМ;

устройство управления (УУ), обеспечивающее на всех этапах выполнения команды выработку необходимых управляющих сигналов.

Оперативная память состоит из ПЗУ и ОЗУ и предназначена для хранения программ, исходных данных, а также промежуточных и конечных результатов вычислений.

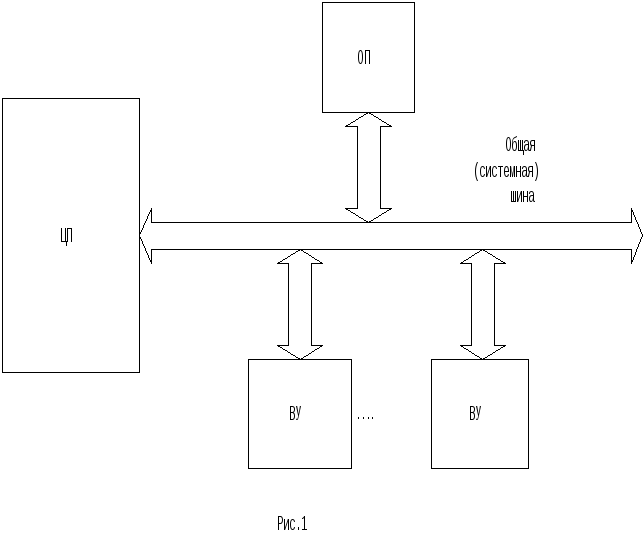

Обычно ЭВМ общего назначения организуется по так называемой схеме с общей шиной (рис. 1).

Здесь ВУ – внешнее устройство.

Системная шина (СШ) в свою очередь подразделяется на шину адреса (ША), шину данных (ШД) и шину управления (ШУ). На ША процессор выставляет адреса ячеек памяти и портов внешних устройств, к которым он обращается. На шине управления процессор формирует сигналы, управляющие передачей информации. Сама передача информации производится по ШД.

В любой конкретный момент времени к СШ может быть подключено не более двух устройств. Одно из этих устройств передает информацию, другое ее принимает. Как правило, одним из этих устройств является ЦП, который и управляет передачей информации по шине. Исключением является режим прямого доступа к памяти, когда ЦП в обмене участия не принимает, а управление обменом берет на себя стоящий в системе контроллер прямого доступа к памяти.

Арифметико-логические устройства.

АЛУ выполняет операции по преобразованию поступающей в него информации. В машинах малой и средней мощности, не имеющих отдельного блока для формирования физических адресов ОП, на АЛУ также возлагаются операции адресной арифметики.

Алгоритмы операций, выполняемых на АЛУ, включают определенную последовательность элементарных действий (микроопераций), среди которых различают прием кода операнда, преобразование этого кода, суммирование кодов двух операндов, сдвиг кода, логические операции над кодами и ряд других.

Для выполнения этих действий в АЛУ в общем случае включаются следующие функциональные узлы:

регистры для временного хранения операндов;

сдвигатели;

преобразователи прямого кода в дополнительный и обратно;

сумматор, на котором реализуются арифметические и логические операции.

Существует много различных типов АЛУ. Например, по системам счисления различают АЛУ с двоичной и десятичной арифметикой, по формам представления числовых данных–АЛУ с фиксированной и плавающей запятой и. т. д. Более подробные сведения о типах и структурах АЛУ рекомендуется искать в соответствующей литературе.