- •Организация эвм и систем

- •Глава 1 эвм общего назначения

- •Структура эвм общего назначения.

- •Арифметико-логические устройства.

- •Устройства управления.

- •Risc и cisc процессоры.

- •1.5 Форматы машинных команд.

- •Inc byte ptr [40h] – одноадресная

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Глава 2

- •2.1 Микропроцессор к1810вм86.

- •2.2 Назначение входов/выходов вм86 в минимальном режиме.

- •2.3 Назначение входов/выходов вм86 в максимальном режиме.

- •Внутренняя архитектура мп вм86.

- •Сегментация памяти.

- •2.6 Программная модель мп вм86.

- •2.7 Организация оперативной памяти.

- •2.8 Организация адресного пространства портов ву.

- •2.9 Методы обмена информацией между мп и портами ву.

- •2.10 Параллельный программируемый адаптер к1810вв55 (i8255).

- •Пример использования и программирования адаптера

- •2.12 Программируемый таймер к1810ви54 (i8254).

- •2.13 Пример использования таймера.

- •2.14 Обработка прерываний.

- •2.15 Система прерываний вм86.

- •2.16 Контроллер прерываний к1810вн59 (i8259).

- •Дополнительная информация о настройке вн59.

- •Прямой доступ к памяти.

- •Программирование кпдп вт37

- •2.21 Организация процессорного модуля вм86.

- •2.20. Организация шинного интерфейса в максимальном режиме

- •2.23. Слабо связанные конфигурации.

- •2.24. Арбитр шин к1810вб89 (i8289).

- •2.25 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •2.26. Формат машинной команды вм86.

2.20. Организация шинного интерфейса в максимальном режиме

Максимальный режим применяется в следующих трех случаях:

МП стоит в сложной однопроцессорной системе;

МП стоит в многопроцессорной системе и является ведущим, а остальные процессоры (например, арифметический сопроцессор ВМ87) – ведомыми. Это, так называемая, сильно связанная конфигурация.

МП стоит в многопроцессорной системе, в которой несколько равноправных процессоров разделяют между собой системную шину. Это, так называемая, слабо связанная конфигурация.

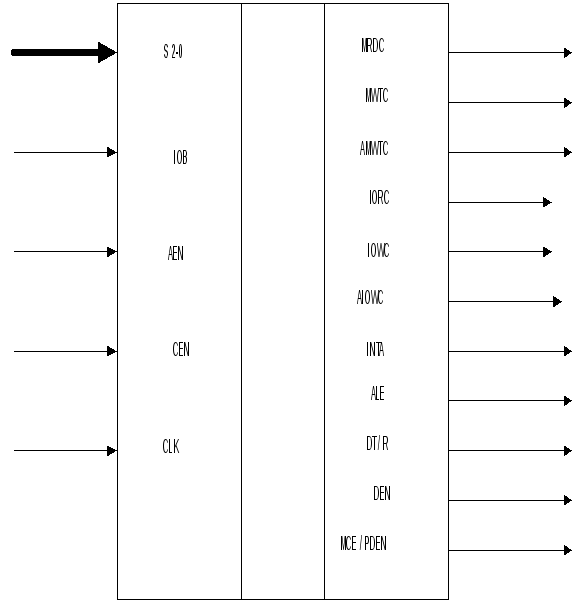

Организация шины данных и шины адреса в максимальном режиме ничем не отличается от их организации в минимальном режиме, а вот организация шины управления имеет существенные отличия. Дело в том, что в максимальном режиме ВМ86 не вырабатывает некоторые необходимые в системе управляющие сигналы. Задача выработки этих сигналов возлагается на специальную микросхему системного контроллера К1810ВГ88 (i8288). Данная микросхема приведена на рис. 33. Далее рассмотрим назначение входов-выходов этой микросхемы.

На входы S2-S0 подаются сигналы состояния с одноименных выходов ВМ86. Эти сигналы характеризуют текущий цикл шины (см. табл.2) и именно по ним контроллер определяет какие управляющие сигналы он должен в данный момент вырабатывать.

На вход CLK подается синхросерия с одноименного выхода генератора ГФ84. По этой синхросерии контроллер определяет момент выдачи управляющих сигналов.

На выходе MRDC (memory read command) контроллер формирует системный управляющий сигнал «чтение из памяти» (MR), а на выходе MWTC (memory write command) – системный управляющий сигнал «запись в память» (MW).

На выходе AMWTC (advanced memory write command) формируется опережающий сигнал «запись в память». Он вырабатывается на один такт ранее сигнала MW и его можно использовать для подготовки к записи медленнодействующих микросхем памяти.

На выходе IORC (input-output read command) контроллер формирует системный управляющий сигнал «чтение из порта ВУ» (IOR), а на выходе IOWC (input-output write command) – системный управляющий сигнал «запись в порт ВУ» (IOW).

Рис. 33

На выходе AIOWC (advanced input-output write command) контроллер формирует опережающий сигнал «запись в порт ВУ». Он вырабатывается на такт ранее IOW и его можно использовать для подготовки ВУ к записи.

Сигнал на выходе ALE (см. одноименный выход ВМ86) определяет момент записи адреса в регистры-защелки ИР82.

Сигнал на выходе DT/R (см. одноименный выход ВМ86) задает направление передачи информации через шинные формирователи ВА86.

Сигнал, снимаемый с выхода DEN (см. одноименный выход ВМ86), подключает шинные формирователи ВА86 к шине данных. Активный уровень сигнала на этом выходе контроллера противоположен активному уровню сигнала на выходе DEN ВМ86, поэтому перед подачей на шинные формирователи сигнал, снимаемый с выхода DEN ВГ88, надо проинвертировать.

INTA – выход подтверждения прерывания (см. одноименный выход ВМ86).

AEN, CEN (command enable – «команда разрешена») и IOB (input-output bus – «резидентная шина ввода-вывода») - управляющие входы контроллера. Если на входе AEN стоит активный нулевой сигнал, контроллер вырабатывает выходные сигналы, если пассивный (единица) – не вырабатывает. Вход CEN действует аналогично входу AEN, только активный сигнал на CEN имеет уровень «единица». Иначе говоря, чтобы ВГ88 вырабатывал выходные сигналы, надо обеспечить AEN=0 и CEN=1. Исключением является случай, когда на вход IOB подана единица. В последнем случае ВГ88 формирует сигналы на выходах IORC, IOWC, AIOWC и PDEN вне зависимости от уровней сигналов на входах AEN И CEN.

Комбинация сигналов на входах AEN, CEN и IOB задает контроллеру конфигурацию системы, в которой работает «его» процессор. В частности, жестко заданная комбинация AEN = IOB = 0, CEN = 1 означает что ВГ88 всегда вырабатывает выходные сигналы. Значит МП стоит в однопроцессорной системе и не разделяет СШ с другими процессорами.

Сигнал на выходе MCE/PDEN (master cascade enable/periphery data enable) трактуется в зависимости от уровня сигнала на входе IOB. Если на IOB подан ноль, сигнал на выходе MCE/PDEN рассматривается как сигнал MCE. Этот сигнал используется если в системе имеет место каскадное подключение контроллеров прерываний ВН59. Если IOB=0, сигнал на выходе MCE/PDEN рассматривается как сигнал PDEN. Назначение сигнала PDEN рассматривается ниже.