- •Московский государственный технический университет

- •Аэрокосмический факультет

- •Нейропроцессоры

- •2006 Г.

- •Краткая историческая справка.

- •Поняте нейросети.

- •Особенности нейросети как вычислительной среды.

- •Применение процессоров общего назначения для построения нейросред.

- •Применение dsp для построения нейросред.

- •Dsp фирмы Analog Devices.

- •Быстрая выборка и исполнение команд.

- •Возможность работы в мультимикропроцессорных конфигурациях.

- •Мощные блоки вычислений.

- •Simd-режим выполнения операций.

- •Применение плис для построения нейросред.

- •Применение аналоговых и гибридных решений для построения нейросред.

- •Сбис etann 80170nx.

- •Сбис clnn32/clnn64 фирмы Bellcore.

- •Применение систолических процессоров для построения нейросред.

- •Некоторые замечания по разработке систол

- •Систолический процессор sand.

- •Систолический процессор cnaps

- •Применение нейросигнальных процессоров для построения нейросред. Нейросигнальный процессор nm6403.

- •Структура нейропроцессора nm6403.

- •Возможности создания многопроцессорных вычислителей на базе nm6403.

- •Реализация нейронной сети на нейропроцессоре nm6403.

- •Задачи, для решения которых используют нейросети.

- •Сравнение быстродействия различных решений.

- •Основные достоинства и недостатки различных решений

- •Литература:

Simd-режим выполнения операций.

ADSP-21161 содержит два набора вычислительных блоков и ассоциированных с ними регистровых файлов. Как показано на рис. обрабатывающие элементы PEx и PEy поддерживают режим SIMD (Single Instruction, Multiple Data) выполнения операций.

Рис. 11: SIMD-режим выполнения операций.

В обычном режиме SISD (Single Instruction, Single Data) DSP использует только PEx. В режиме SIMD DSP параллельно выполняет следующие операции:

Направляет единственную инструкцию в оба обрабатывающих элемента

Загружает два набора данных из памяти в каждый элемент

Выполняет одну и ту же команду одновременно в двух элементах

Сохраняет результаты совместного выполнения в памяти

Оба обрабатывающих элемента содержат идентичные блоки (АЛУ, умножитель, блок сдвига, регистровый файл), выполняемая инструкция также одинакова для PEx и PEy, отличаются лишь обрабатываемые данные. Большинство регистров в PEx имеют соответствующие им регистры в PEy, выполняя инструкцию, обрабатывающие элементы используют значения из <<своих>> регистров.

Таким образом, используя SIMD-команды DSP может удвоить скорость обработки данных. В нейроприложениях это особо актуально, так как для них характерно выполнение одинаковых операций для большого набора однородных данных.

Применение плис для построения нейросред.

Приборы программируемой логики, представителями которых являются ПЛИС (Программируемые Логические Интегральные Схемы) применяются на протяжении нескольких десятилетий для построения разнообразных интерфейсных узлов, устройств управления и контроля и т.д. Однако, если еще 5 лет назад ПЛИС занимали весьма скромную нишу на рынке электронных компонентов (в первую очередь из-за небольшого быстродействия и малого количества эквивалентных логических вентилей), то сейчас ситуация кардинально изменилась. Раньше о ПЛИС говорили, в основном, как о чем-то, недостойном внимания серьезных разработчиков. Но с появлением быстродействующих ПЛИС сверхвысокой интеграции, работающих на высоких тактовых частотах, их ниша на мировом рынке значительно расширилась.

Современные образцы ПЛИС, выполненные по современной 0,22-микронной технологии, способны работать на частотах до 300 МГц и реализуют до 3 млн. эквивалентных логических вентилей. Компания Xilinx, один из мировых лидеров в данной области, уже объявила о выпуске ПЛИС в 10 млн. логических вентилей.

Столь резкое увеличение мощности ПЛИС позволяет использовать их не только для реализации простых контроллеров и интерфейсных узлов, но и для цифровой обработки сигналов, сложных интеллектуальных контроллеров и нейрочипов. Появление быстродействующих ПЛИС со сверхнизким уровнем энергопотребления открывает широкие возможности по их использованию в системах мобильной связи (в частности, непосредственно в сотовых телефонах и пейджерах), в портативных проигрывателях (например, в МР3-проигрывателях) и других автономных устройствах.

ПЛИС изготовляются многими производителями, среди которых основными являются Altera, Xilinx, Atmel, Csypres, Lattice, Lucent. Выделить продукцию какой-либо одной из этих фирм невозможно, так как по техническим характеристикам они различаются очень мало.

По принципу формирования требуемой структуры целевого цифрового устройства все основные современные ПЛИС подразделяются на две группы:

(CPLD - Complex Programmable Logic Devices). К этой группе относятся устройства, в которых требуемая структура создается программированием связей коммутирующих матриц с использованием технологий перепрограммируемых постоянных запоминающих устройств: FLASH или EPROM. CPLD содержат несколько логических блоков, объединенных коммутационной матрицей. Каждый логический блок представляет собой структуру типа ПМЛ, т.е. программируемую матрицу <<И>> и фиксированную матрицу <<ИЛИ>>. Особенность этих устройств заключается в том, что сформированная структура является энергонезависимой, то есть сохраняется при выключении питания. Для изменения структуры необходимо выполнить операции стирания и программирования новой структуры.

(FPGA - Field Programmable Gate Array). К этому классу относятся ПЛИС, которые управляются битовой последовательностью, хранящейся во внутреннем статическом ОЗУ. Особенностью устройств этого класса является то, что требуемая структура целевого устройства должна восстанавливаться (записываться во внутреннее статическое ОЗУ) после каждого включения питания, что требует принятия дополнительных мер по сохранению и восстановлению требуемой конфигурации. С одной стороны это является недостатком подобных устройств, а с другой - позволяет реализовать системы с изменяющейся архитектурой, что может быть особенно полезно для реализации нейросетей с обучением.

Рассмотрим структуру ПЛИС на примере семейства AT40K, выпускаемого компанией Atmel. Чипы этого семейства имеют следующие характеристики:

системная частота до 100 Мгц

буфер на 3 состояния для каждой ячейки

до 2Кбайт внутренней 10 нс SRAM

модификации для напряжения питания 3.3В и 5В

модификации для разных диапазонов температур

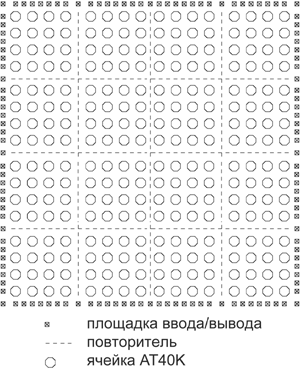

Основным архитектурным блоком является матрица одинаковых ячеек (рис. ). Массив однороден по всей площади, кроме шинных повторителей, отделяющих каждые четыре ячейки.

Рис. 26: Массив ячеек AT40K

На пересечении вертикальных и горизонтальных линеек повторителей расположен блок RAM 32x4, доступный для смежных ячеек. Эта память может быть сконфигурирована для синхронного и асинхронного доступа и для одно- и двухпортового режима работы.

Рис. 27: Плоскость шин (одна из пяти)

Сама концепция ПЛИС предполагает наличие возможности разнообразного соединения вычислительных ячеек. Весь кристалл охватывает пять идентичных плоскостей шин (рис.27), каждая из которых содержит 2 плоскости express-шин и одну плоскость local-шин. Шины функционируют благодаря повторителям. Каждый повторитель имеет соединения с двумя соседними сегментами local-шины и двумя соседними сегментами express-шины. Повторители усиливают сигналы и могут соединять любые шины данной плоскости шин.

Ячейка может соединяться с любой из восьми соседних ячеек и любой из локальных шин (вертикальных или горизонтальных). Каждая ячейка может быть соединена только с одной шиной из шинной плоскости.

Рис. 28: Связи ячейки AT40K

Основой ячейки FPGA является логическая таблица (LUT - look-up table), представляющая собой однобитное ОЗУ на 8 ячеек. Триггеры всех логических таблиц входят в состав программирующего регистра и их начальное состояние заполняется в период конфигурирования ПЛИС. Каждая ячейка содержит две логические таблицы.

В ПЛИС используются программируемые D-триггеры. При конфигурировании, обычно, можно задать такие режимы работы триггера, как триггер с начальным сбросом (R) или начальной установкой (S), с записью по фронту или спаду синхросерии, с разрешением или без разрешения записи. Различные варианты соединения логических таблиц и триггера позволяют создавать на базе ячеек различные устройства: регистры, сумматоры, умножители, счетчики.

Каждая ячейка FPGA содержит буфер с тремя состояниями. Применение шин с тремя состояниями - типичное схемное решение вычислительных устройств, реализованных на плате. Благодаря такому решению, легко достигается многомодульность и наращиваемость системы, низкие аппаратурные затраты и малые задержки в системе межсоединений. Внутри заказных СБИС редко применяются шины с тремя состояниями из-за технологических трудностей их безотказной реализации, а также увеличенной задержки на их переключение. Тем не менее, в ПЛИС широко применяются шины с тремя состояниями, хотя это существенно повышает их себестоимость. Применение шин с тремя состояниями дает следующие преимущества:

значительно упрощается подключение к чипу внешних устройств, что позволяет в конечном итоге снизить стоимость, размеры и энергопотребление системы в целом;

упрощается переход от проекта схемы на плате к схеме на кристалле;

упрощается построение распределенного ОЗУ.

Для реализации в ПЛИС модулей ОЗУ предусмотрено две возможности. Первую возможность предоставляет каждая ЛТ, которая может быть сконфигурирована как ОЗУ. Для наращивания емкости памяти выходы нескольких ячеек с модулями ОЗУ через тристабильные буферы подключаются к общим шинам. При этом требуется дополнительное оборудование только для построения схемы дешифрации адреса, которая выдает сигналы выборки той или иной логической таблицы для записи, а также того или другого тристабильного буфера для чтения. Такое ОЗУ распределено по площади кристалла и поэтому названо Distributed RAM (распределенным ОЗУ).

Вторую возможность предоставляют отдельные блоки памяти, имеющиеся в ПЛИС. Блоки двухпортовой 32x4 RAM распределены по кристаллу (рис. 26). Две четырехбитовые шины (входные данные и выходные данные) подключены к local-шинам. Пятибитные шины адреса записи и чтения подключены к пяти вертикальным express-шинам.

Преимуществами FPGA-чипов для реализации нейроустройств являются:

Высокое быстродействие и постоянный его рост. Современные FPGA-чипы работают на частотах 300МГц, чипы выполняются с использованием прогрессивных методов с технологическими нормами до 0.09 мкм на девяти слоях металла. На рынке ПЛИС существует здоровая конкуренция, поэтому все технологические новшества сразу внедряются в серийные изделия. Постоянно расширяется спектр продукции, появляются гибридные решения, например, FPGA-чипы со встроенным микроконтроллером.

Возможность реализации сложных параллельных алгоритмов. Данная технология изначально предполагает реализацию на одном кристалле множества блоков с интенсивным обменом информацией между ними. В то время как реализация параллельной обработки данных на процессорах общего назначения или цифровых сигнальных процессорах требует значительных усилий для построения мультимикропроцессорных систем, то в FPGA-системе разработчик не сталкивается с жесткими архитектурными ограничениями и может эффективно реализовать параллельные алгоритмы.

Возможность перепрограммирования в системе. Программирование FPGA задает не только алгоритм обработки данных, но и сам тип устройства, реализуемого чипом, поэтому использование этой функции может иметь очень большой эффект для гибкости системы в целом.

Совместимость при переносе алгоритмов на уровне языков описания аппаратуры. Так как реализация большого проекта с помощью FPGA вручную практически невозможна, то разработаны фирменные средства, автоматически реализующие устройство по его описанию. При этом используются стандартизированные языки описания аппаратуры (VHDL, AHDL, Verilog и др.). Эти языки не зависят от конкретной используемой FPGA-микросхемы, поэтому высока переносимость разработок. В этой области дела обстоят гораздо лучше, чем у процессоров общего назначения и цифровых сигнальных процессорах, где программа, реализующая любой алгоритм должна учитывать особенности конкретной аппаратуры.

Возможность реализации стандартного интерфейса. Любые FPGA-чипы имеют в своем составе блоки ввода/вывода, которые могут быть настроены под различные стандарты электрического соединения входов микросхем. Выходные значения могут настраиваться на уровни ТТЛ, КМОП, шины PCI и многие другие, что позволяет избежать дополнительного оборудования при встраивании FPGA-схемы в систему.

Наличие библиотек мегафункций, описывающих сложные алгоритмы. Вместе с фирменной САПР FPGA-систем поставляются макробиблиотеки стандартных элементов. Причем эти библиотеки содержат готовые сложные блоки(такие как блок быстрого преобразования Фурье).

Малое время создания нейросистем. По этому параметру FPGA-нейросистемы превосходят все заказные чипы и приближаются к системам на существующих процессорах общего назначения и цифровых сигнальных процессорах. Это является очень важным, так как на фоне постоянного роста производительности процессоров специфические аппаратные решения должны показывать преимущество в скорости работы. При традиционной разработке нейросистемы на заказных интегральных схемах результат работы может оказаться уже морально устаревшим.

Реализовать нейросистему на ПЛИС-микросхемах можно двумя различными способами:

Непосредственная реализация нейроархитектуры. При этом подходе различные участки ПЛИС реализуют отдельные нейроны, между которыми программируются межсоединения. Возможна реализация любой нейросети, в том числе с обратными связями, с разными типами нейронов, с неоднородностями в топологии межсоединений. Дополнительная гибкость обеспечивается за счет перепрограммирования ПЛИС.

Это решение имеет следующие достоинства:

возможно обеспечить высокую параллельность обработки данных

возможно реализовать любую топологию нейросети и вид нейронов

возможно менять структуру сети на аппаратном уровне

Недостатками этого решения являются

отсутствие готовых решений

высокая схемотехническая сложность реализации отдельного нейрона

Особо значим второй недостаток. На ПЛИС с интеграцией в 40 тысяч эквивалентных вентилей можно реализовать до 15 параллельно работающих нейронов, а доступны ПЛИС с интеграцией в 2.67 миллиона вентилей (EP20K1000 фирмы Altera), что дает возможность реализовать, соответственно, 1000 параллельных нейронов. Такое число нейронов уже достаточно для серьезных нейроприложений. Но при необходимости реализации сложных нейронов ситуация сильно ухудшается. Реализация умножителя требует больших затрат ресурсов ПЛИС, а каждый нейрон требует по крайней мере одного умножителя. Это ведет к созданию решений, которые используют черты традиционных архитектур. Например, один блок умножения, который используется несколькими нейронами, или один блок вычисления сложной активационной функции. Это ведет к другому типу ПЛИС-нейроархитектур.

Реализация аппаратной среды для микропрограмной реализации нейроалгоритмов. Этот тип оборудования может воплощать черты процессора общего назначения, цифрового сигнального процессора, специального нейропроцессора и периферийных блоков. Фактически, таким образом реализуется создание заказной нейросистемы. Но заказную СБИС реализовывать очень дорого и долго. Дороговизну разработки специального нейрочипа может окупить либо большая цена кристалла, либо большая серия. Но нейрочипы не нужны в массовых количествах, а сверхдорогие решения непозволительны для многих применений нейросистем. К тому же время разработки и внедрения нейрокристалла может быть настолько велико, что к моменту выпуска он может уже морально устареть.

Это исправляется использованием ПЛИС. Темпы роста вычислительной мощности ПЛИС, по крайней мере, не уступают аналогичной характеристике универсальных процессоров. ПЛИС дешевы, а проектирование устройства на базе ПЛИС занимает всего несколько месяцев. Поэтому в последние годы к ПЛИС начинают относиться как к новой надежде для нейроархитектур. Особенно это относится к странам, которые не имеют своего производства СБИС-чипов (к которым относится и Россия).

К сожалению, ПЛИС-нейросред разработано пока мало. Единственным описанным примером является модуль цифровой обработки сигналов XDSP-680-CP фирмы СканИнжинирингТелеком. Модуль XDSP-680-CP предназначен для решения задач цифровой обработки сигналов высокой производительности и, благодаря наличию трактов АЦП и ЦАП, позволяет строить полностью законченные системы обработки как цифровых, так и аналоговых сигналов с вводом-выводом данных из ПЭВМ. В качестве возможных областей применения производители указывают нейросетевые вычислители. Общая структура модуля приведена на рис. .

Рис. 29: Структура модуля XDSP-680

Модуль выполнен в виде PCI-платы. Плата содержит четыре ПЛИС XCV50-4PQ240C, служебная ПЛИС типа CPLD XC95288XL, банк SRAM 128Kx32 со временем доступа 7.5нс, FLASH 16Мбит, АЦП 12бит 80МГц, ЦАП 14бит 125МГц, два внешних цифровых порта по 16бит, компаратор тактового ввода.

Системная тактовая частота FPGA-схем может составлять 250МГц, что позволяет добиваться высокой производительности:

220 MMAC на 8 разрядных операндах

45 MMAC на 16 разрядных операндах

5 MMAC на 32 разрядных операндах