- •Московский государственный технический университет

- •Аэрокосмический факультет

- •Нейропроцессоры

- •2006 Г.

- •Краткая историческая справка.

- •Поняте нейросети.

- •Особенности нейросети как вычислительной среды.

- •Применение процессоров общего назначения для построения нейросред.

- •Применение dsp для построения нейросред.

- •Dsp фирмы Analog Devices.

- •Быстрая выборка и исполнение команд.

- •Возможность работы в мультимикропроцессорных конфигурациях.

- •Мощные блоки вычислений.

- •Simd-режим выполнения операций.

- •Применение плис для построения нейросред.

- •Применение аналоговых и гибридных решений для построения нейросред.

- •Сбис etann 80170nx.

- •Сбис clnn32/clnn64 фирмы Bellcore.

- •Применение систолических процессоров для построения нейросред.

- •Некоторые замечания по разработке систол

- •Систолический процессор sand.

- •Систолический процессор cnaps

- •Применение нейросигнальных процессоров для построения нейросред. Нейросигнальный процессор nm6403.

- •Структура нейропроцессора nm6403.

- •Возможности создания многопроцессорных вычислителей на базе nm6403.

- •Реализация нейронной сети на нейропроцессоре nm6403.

- •Задачи, для решения которых используют нейросети.

- •Сравнение быстродействия различных решений.

- •Основные достоинства и недостатки различных решений

- •Литература:

Возможности создания многопроцессорных вычислителей на базе nm6403.

Нейропроцессор NM6403 имеет следующие аппаратные средства, предназначенные для построения многопроцессорных систем на его основе:

два байтовых коммуникационных порта CP0 и CP1, каждый из которых позволяет осуществить обмен между нейропроцессором и другой системой со скоростью 20 Мбайт/с.

два программируемых интерфейса с 64 разрядными внешними шинами (локальной и глобальной), каждый из которых поддерживает три различных мультипроцессорных конфигурации внешней шины. Подключение к одной шине нескольких нейропроцессоров позволяет им обмениваться информацией через общую память, расположенную на этой же шине. Подключение к одной шине двух нейропроцессоров осуществляется без использования дополнительной управляющей аппаратуры. Скорость обмена данными через общую шину может достигать 400 Мбайт/с.

Каждая из двух внешних шин поддерживает как однопроцессорный, так и многопроцессорный режим работы, если к общей памяти подключены два процессора, то арбитраж для доступа к ней осуществляется между ними без использования внешнего контроллера.

Возможны три типа конфигурации внешней шины для многопроцессорного режима:

Банк 0 - общий, банк 1 - общий (конфигурация 1, рис. ). Доступ к памяти в каждый момент времени разрешен лишь одному процессору.

Рис. 16: Конфигурация 1 шины

Банк 0 - свой, банк 1 - общий (конфигурация 2, рис. ). Каждый процессор имеет свой банк памяти, к которому другой не имеет доступа. Общий банк доступен через буферы, обращение к нему идет поочередно.

Рис. 17: Конфигурация 2 шины

Банк 0 - свой, банк 1 - чужой (конфигурация 3, рис. ). Каждый процессор имеет свой банк памяти, но существует возможность каждому процессору обратиться к чужому банку через буфер.

Рис. 18: Конфигурация 3 шины

Хотя возможности построения мультимикропроцессорных систем на базе NM6403 довольно ограничены (по сравнению с рассмотренным выше семейством цифровых сигнальных процессоров), но все же они являются вполне достаточными для создания нейроприложений повышенной производительности. Примеры мултимикропроцессорных структур приведены на рис. .

Рис. 19: Линейная (кольцевая) и матричная мультимикропроцессорные структуры

Реализация нейронной сети на нейропроцессоре nm6403.

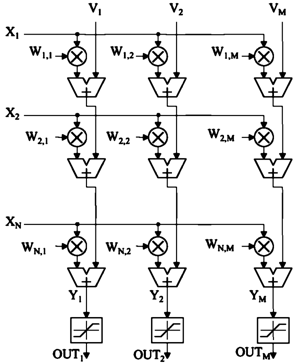

Рис. 20: Модель слоя сети NM6403

Обработка реакции сети на входное воздействие происходит в нейропроцессоре последовательно, слой за слоем. На рис.20показана модель нейронной сети, эмулируемой NM6403. В общем случае каждый слой нейросети имеетNнейронных входов и состоит изMнейронов. При этом каждый нейрон выполняет взвешенное суммирование с учетом смещения данного нейрона:

|

Затем каждый нейрон вычисляет функцию насыщения от результата взвешенного суммирования:

|

Все входные данные, весовые коэффициенты, пороговые значения и результаты представляются в дополнительном коде.

Процессор NM6403 создавался как универсальное средство для реализации нейросред. При его использовании пользователь может программно задавать множество параметров нейронной сети:

число слоев;

число нейронов и нейронных входов в каждом слое;

разрядность данных на каждом нейронном входе;

разрядность каждого весового коэффициента;

разрядность выходного значения каждого нейрона;

параметр функции насыщения для каждого нейрона.

Для эмуляции нейронной сети каждый ее слой разбивается на последовательно обрабатываемые фрагменты. Данное разбиение осуществляется следующим образом. Множество нейронных входов слоя разбивается на группы входов так, чтобы суммарная разрядность данных, подаваемых на каждую группу входов, была равна разрядности нейропроцессора - 64. Множество нейронов слоя разбивается на группы нейронов так, чтобы суммарная разрядность результатов взвешенного суммирования для каждой группы также была равна 64. Таким образом выделяются фрагменты сети двух типов с разным функциональным назначением: первый тип фрагментов осуществляет взвешенное суммирование, а второй - вычисление функции активации.

Эмуляция слоя нейронной сети на нейропроцессоре NM6403 состоит из последовательно выполняемых макроопераций, каждая из которых эмулирует один фрагмент слоя. Число выполняемых макроопераций равно числу фрагментов в слое. Обработка данных ведется нейропроцессором в пакетном режиме - по T наборов входных данных в каждом пакете. Пакет данных, подаваемых на группу нейронных входов слоя нейронной сети представляет собой вектор Xn= <X1,,Xn> , каждый элемент которого является вектором упакованных данных. Разрядность каждой из упакованных величин может принимать любое четное значение в диапазоне от 2 до 64, то есть количество элементов вектора может быть любым от 1 до 32. Ограничением является то, что суммарная разрядность всех данных, упакованных в одном векторе, должна быть равна 64.

При эмуляции фрагмента первого типа нейропроцессор выполняет следующую операцию для каждого набора входных данных: Yn=Yn-1+Xn×Wn. В качествеY0выступает смещениеV0.

64 разрядные выходные векторы содержат упакованные данные с разрядностью от Nminдо 64. Значение минимальной разрядности каждого элемента в этих векторах зависит от суммарного числа нейронных входов в слое и вытекает из необходимости избегать арифметического переполнения при сложении чисел:

|

Выполнение операции взвешенного суммирования над всеми векторами задается одной командой <<vsum>> нейропроцессора. Выполнение этой команды зависит от количества значений в обрабатываемом векторе, за один такт обрабатывается один компонент вектора.

При эмуляции фрагмента второго типа для группы нейронов процессор формирует вектор Xn= <OUT1,,OUTm> , каждый элемент которого является вектором упакованных данных. Компонентами вектораOUTiявляются результаты вычисления функции насыщения над элементомYiвектораY:

|

Вычисление функций насыщения для всех элементов всех векторов задается одной командой <<activate>> нейропроцессора. Время выполнения этой команды также составляет один такт на компонент.

Ориентация нейропроцессоров на создание нейросред значительно упрощает создание высокопроизводительных нейросетевых приложений. Разработчики нейропроцессоров создают библиотеки алгоритмов для наиболее распространенных типов нейросетей, что делает их особенно привлекательными для построения нейросред.