- •Оглавление

- •Архитектура вычислительных систем

- •Этапы развития вычислительных машин

- •Фон неймановская архитектура

- •Типы структур вычислительных машин и систем

- •Вычислительная система с общей памятью

- •Распределенная система

- •Классификация параллельных вычислительных систем

- •29.09.2011

- •Способы ускорения традиционных архитектур

- •01.10.2011

- •Супер скалярные процессоры

- •06.10.2011 Кэш-память

- •Алгоритмы замещения информации в заполненной кэш-памяти.

- •27.10.2011 Расслоенная память Блочная организация основной памяти

- •Структура основной памяти на основе блочной схемы

- •Циклическая организация

- •Блочно-циклическая схема расслоения памяти

- •Архитектура с сокращенным набором команд

- •КлассSimd

- •Структура типа память-память и регистр-регистр

- •03.11.2011 Матричные вычислительные системы

- •Контроллер массива процессоров

- •Массив процессоров

- •10.11.2011 Ассоциативные вычислительные системы

- •Вычислительные системы с систолической структурой

- •Классификация систолических структур

- •Основы теории вычислительных систем

- •Задача синтеза

- •Модели вычислительных систем

- •Статистические модели

- •Аналитические методы

- •Имитационные модели

- •Экспериментальные методы

- •24.11.2011 КлассMimd

- •Симметричные мультипроцессорные системы (smp)

- •Архитектура с общей шиной

- •Классификация кластеров

- •01.12.2011 Топологии кластеров

- •Системы с массовой параллельной обработкой (mpp-системы)

- •Транспьютеры

- •08.12.2011 Вычислительные системы с неоднородным доступом к памяти (cc-numa)

- •Вычислительные системы с обработкой по принципу волнового фронта

- •Надежность и отказоустойчивость вычислительных систем

- •Трансляторы

- •10.12.2011

- •Варианты взаимодействия двух трансляторов

- •Многопроходная трансляция

- •Однопроходная трансляция

29.09.2011

Формирование адреса следующей команду;

Для фон-неймановских машин характерно размещение соседних команд программы в смежных ячейках памяти. Если извлеченная команда не нарушает естественного порядка выполнения программы, то для вычисления адреса следующей команды достаточно увеличить значение СК на длину текущей команды.

Декодирование команды;

После выборки команды она должна быть декодирована. На этапе декодирования выясняются следующие моменты:

Находится ли в регистре полный код команды, или требуется дозагрузка остальных слов;

Какие действия требуются для выполнения команды;

Если команда требует операнды, выяснить откуда они должны быть взять и куда поместить результат.;

Вычисление адресов операндов;

Этап имеет место, если впроцесса декодирования команды выясняется, что команда использует операнды. Если операнды располагаются в основной памяти, то осуществляется вычисление их адресов с учетом указанного в команда способа адресации.

Выборка операндов;

Вычисленные на предыдущем этапе исполнительные адреса используются для считывания операндов из памяти и занесения в регистры процессора

Исполнение операции;

Запись результата;

Присутствует в цикле тех команд, которые предполагают занесение результата в регистр или ячейку основной памяти.

Способы ускорения традиционных архитектур

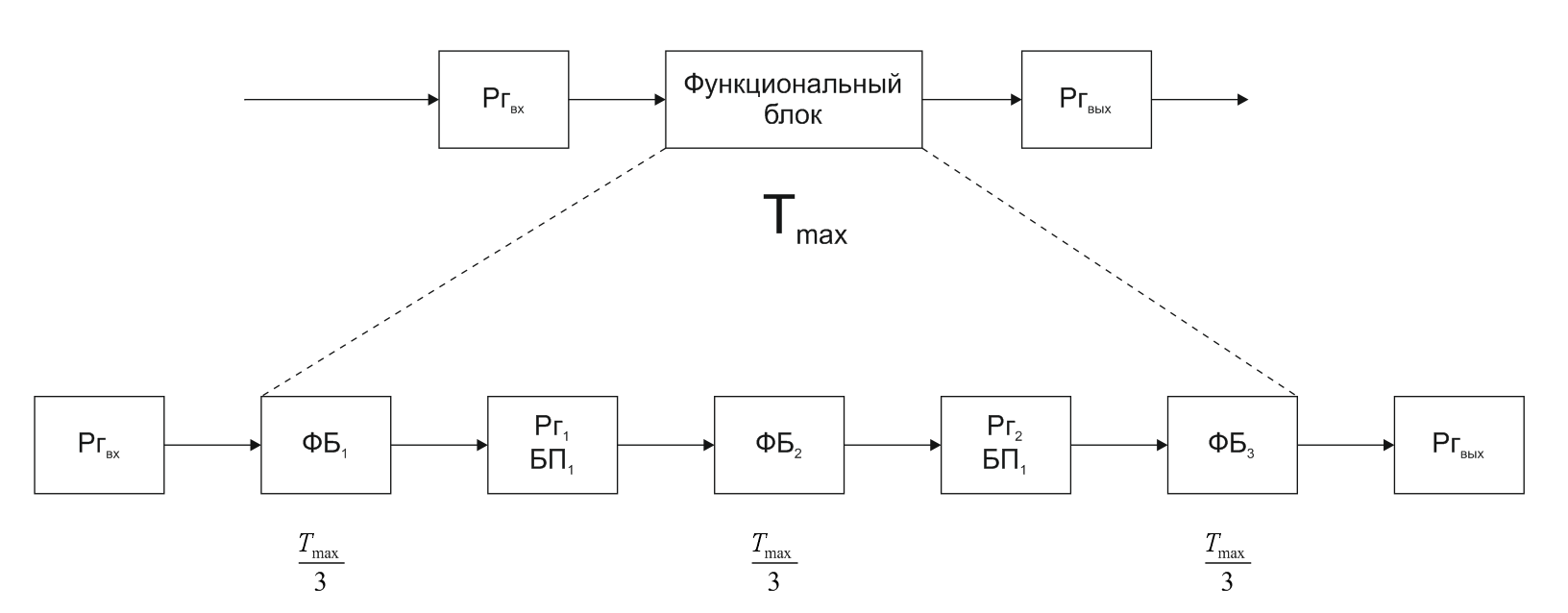

Рисунок 10 Конвейеризация

Исходные данные помещаются во входной регистр, обрабатываются в функциональном блоке, а результат обработки фиксируется в выходном регистре. Если максимальное время обработки в ФБ=Tmax, то результат может быть занесен в Ргвых не ранее, чем через Tmax.

Распределим функции, выполняемые в ФБ, между тремя независимыми блоками так, чтобы максимальное время обработки в них была одинаковыми. Между блоками разместим буферные регистры, предназначенные для хранения результатов на случай, если следующий за ней ФБ не готов использовать этот результат.

В рассмотренной

схеме данные на вход конвейера могут

подаваться с интервалом

.

На практике редко удается добиться

того, чтобы задержки в каждом ФБ были

одинаковыми. Для устранения этого

недостатка каждый буферный регистр

заменяется буферной памятью, способной

хранить множество данных и организованной

по принципуFIFO.

.

На практике редко удается добиться

того, чтобы задержки в каждом ФБ были

одинаковыми. Для устранения этого

недостатка каждый буферный регистр

заменяется буферной памятью, способной

хранить множество данных и организованной

по принципуFIFO.

Конвейер команд.

ВК – выборка команды

ДК – декодирование команды

ВА – вычисление адресов

ВО – выборка операндов

ИК – исполнение команды

ЗР – запись результата.

Рисунок 11 Конвейер команд

Конфликтные ситуации в конвейере принято обозначить термином риск. Они могут быть обусловлены:

Попуткой нескольких команд одновременно обратиться к одному и тому же ресурсу вычислительной машины;

Взаимосвязью команд по данным;

Неоднозначностью при выборе следующей команды в случае команд перехода – риск по управлению;

Структурного риска можно избежать за счет модульного построения памяти и использования кэш-памяти.

Риск по данным возникает, когда две команды в конвейере i иj предусматривают обращение к одной и той же переменной x, причем i предшествует j. Возможные риски:

Чтение после записи. Команда j читает x до того, как команда i успела записать новое значение x;

Запись после чтения. Команда j записывает новое значение x до того, как команда i успела прочитать это x;

Запись после записи. Команда j записывает новое значение x прежде, чем команда i успела записать в качестве x своё значение;

Наиболее частный вид конфликтов по данным - чтение после записи. Данный вид конфликта появляется в том случае, если командам в конвейере разрешается догонять предшествующие им команды, приостановленные из-за конфликтов.

Для борьбы с конфликтами по данным применяются программирование аппаратные методы. Программные методы ориентируются на устройстве конфликтов еще на стадии компиляции. Оптимизирующий компилятор пытается создать такой объектный код, чтобы между командами, склонными к конфликтам, находилось достаточное количество нейтральных команд. Если это не удается, то между конфликтующими командами вставляется необходимое количество NOP-ов.