- •Оглавление

- •Архитектура вычислительных систем

- •Этапы развития вычислительных машин

- •Фон неймановская архитектура

- •Типы структур вычислительных машин и систем

- •Вычислительная система с общей памятью

- •Распределенная система

- •Классификация параллельных вычислительных систем

- •29.09.2011

- •Способы ускорения традиционных архитектур

- •01.10.2011

- •Супер скалярные процессоры

- •06.10.2011 Кэш-память

- •Алгоритмы замещения информации в заполненной кэш-памяти.

- •27.10.2011 Расслоенная память Блочная организация основной памяти

- •Структура основной памяти на основе блочной схемы

- •Циклическая организация

- •Блочно-циклическая схема расслоения памяти

- •Архитектура с сокращенным набором команд

- •КлассSimd

- •Структура типа память-память и регистр-регистр

- •03.11.2011 Матричные вычислительные системы

- •Контроллер массива процессоров

- •Массив процессоров

- •10.11.2011 Ассоциативные вычислительные системы

- •Вычислительные системы с систолической структурой

- •Классификация систолических структур

- •Основы теории вычислительных систем

- •Задача синтеза

- •Модели вычислительных систем

- •Статистические модели

- •Аналитические методы

- •Имитационные модели

- •Экспериментальные методы

- •24.11.2011 КлассMimd

- •Симметричные мультипроцессорные системы (smp)

- •Архитектура с общей шиной

- •Классификация кластеров

- •01.12.2011 Топологии кластеров

- •Системы с массовой параллельной обработкой (mpp-системы)

- •Транспьютеры

- •08.12.2011 Вычислительные системы с неоднородным доступом к памяти (cc-numa)

- •Вычислительные системы с обработкой по принципу волнового фронта

- •Надежность и отказоустойчивость вычислительных систем

- •Трансляторы

- •10.12.2011

- •Варианты взаимодействия двух трансляторов

- •Многопроходная трансляция

- •Однопроходная трансляция

Вычислительная система с общей памятью

Рисунок 3 Вычислительная система с общей памятью

Данных подход имеет недостатки, аналогичные структуре вычислительных машин с общей шиной. Достоинством является то, что на обмен информацией между процессорами не связан с дополнительными операциями и обеспечивается за счет доступа к общей общим областям памяти.

Распределенная система

В распределенной системе общая память отсутствует, а каждый процессор обладает собственной локальной памятью.

Рисунок 4 Распределенная система

Классификация параллельных вычислительных систем

Классификация Флинна (1966)

В основу классификации положение понятие потока, под которым понимается последовательность элементов (команд и данных), обрабатываемая процессором. В зависимости от количества потоков команд и потоков данных Флинн выделяет 4 класса архитектур: SISD, MISD, SIMD, MIMD.

SISD – к данному классу относятся класс фон-неймановских машин (иногда векторные конвейеры, при условии, что вектор рассматривается как одна единица данных).

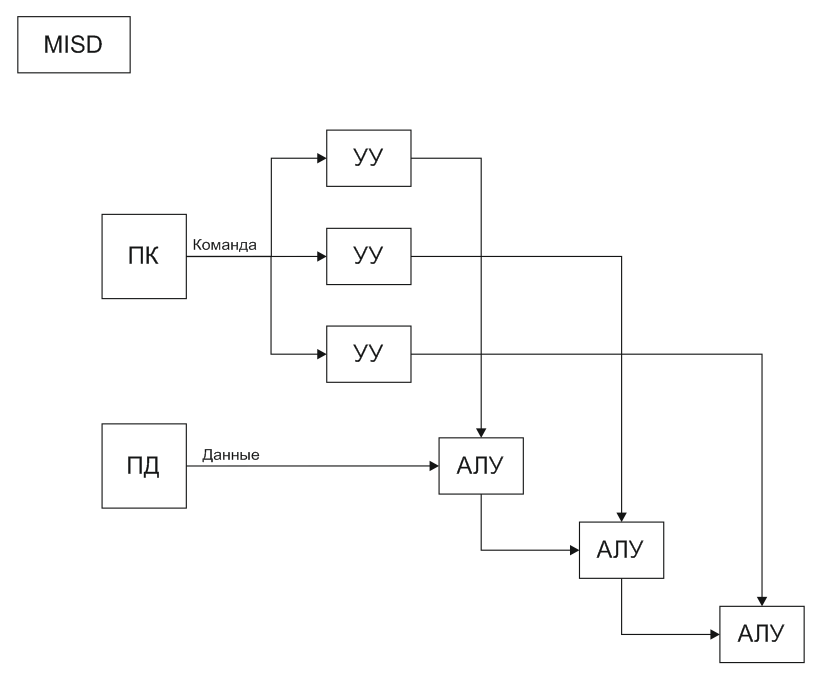

MISD – пока считается пустым

Рисунок 5SISD

Рисунок 6MISD

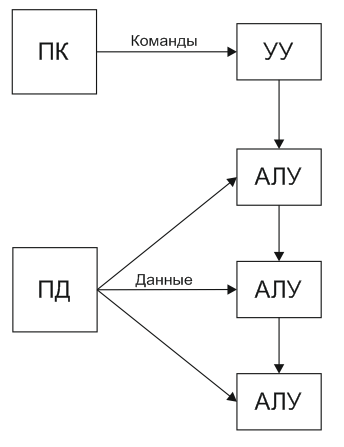

SIMD – матричные вычислительные системы (а также векторные конвейеры, если рассматривать вектор как множество элементов)

Рисунок 7 SIMD

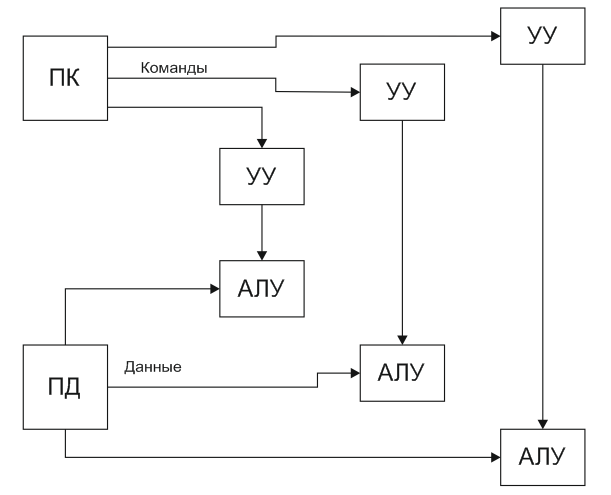

MIMD:

Рисунок 8MIMD

Большинство систем относится к MIMD.

Класс SISD

Архитектура традиционных ЭВМ:

Рисунок 9Архитектура традиционных ЭВМ

УУ – организует автоматическое управление программами и функциями вычислительной машины как единой системы.

СК – счетчик команд.

РК – регистр команд.

УС – указатель стека.

РАП – регистр адреса памяти.

РДП – регистр данных памяти.

ДкОп – дешифратор кода операции.

МПА – микропрограммный автомат.

22.09.2011

СК – счетчик команд в соответствии с фон-неймановским принципом программного управления, соседние команды программы располагаются в ячейках памяти со следующим по порядку адресами и выполняются примерно в той же очередности, в какой размещены в памяти вычислительные машины.

Перед началом вычислений в СК заносится адрес ячейки основной памяти, где хранится команда, которая должна быть выполнена первой. В процессе выполнения каждой команды в счетчике формируется адрес следующей команды путем увеличения его содержимого на длину выполняемой команды. Для изменения естественного порядка выполнения достаточно в СК занести адрес точки перехода.

РК – регистр команд. Для выполнения команды её необходимо извлечь из памяти в регистр команды. Этот этап носит название выборки команды. С момента загрузки команды она становится видимой для процессора и хранится в РК в течении всего времени её выполнения.

Любая команда содержит поле кода операции и поле адресной части. Если команда занимает несколько последовательных ячеек, то код операции всегда находится в том слове команды, которое хранится первым. По нему определяется, требуется ли считывание из памяти и загрузка в РК остальных слов.

УС – указатель стека – регистр, хранящий адрес вершины стека. Стек реализуется в виде участка основной памяти, расположенной в области наибольших адресов. Для хранения адреса ячейки, куда была произведена последняя запись, предназначен указатель стека. При выполнении операции занесений в стек содержимое указателя стека уменьшается, после чего используется в качестве адреса, по которому производится запись. Считывание из стека происходит из ячейки, на которую указывает текущий адрес УС, после чего содержимое УС увеличивается.

РАП – регистр адреса памяти – предназначен для хранения адреса ячейки основной памяти вплоть до завершения операции считывания или записи в эту ячейку. Наличие данного регистра позволяет компенсировать различие в быстродействии основной памяти и остальных устройств машины.

РДП – регистр данных памяти – призван компенсировать разницу в быстродействии ЗУ и устройств, выступающих в роли источника и потребителей данных.

ДкОп – дешифратор кода операции – преобразует код операции в форму, требуемую для работы микропрограммного автомата. Её вид зависит от организации МПА.

МПА – микропрограммных автомат – формирует последовательность сигналов управления на основе декодирования кода операции, состояния признаков (флагов) характеризующих результат предшествующих вычислений, внешних запросов на прерывание текущей программы.

ОЛБ – операционный блок – выполняет арифметические и логические операции над поданными на вход операндами. Выбор операции осуществляется с помощью сигнала, подаваемого с ДкОп. Операционные блоки АЛУ строятся как комбинационные схему, не обладающие внутренней памятью и до момента сохранения результата операнды должны присутствовать на входе блока.

Регистры операндов – обеспечивают сохранение операндов на входе блока вплоть дополучение результата операции и его записи.

Регистр признаков – предназначен для фиксации и хранения признаков, характерных результатов последней выполненной арифметической и логической операции.

Аккумулятор – регистр, выполняющих следующие функции:

Загрузка одного из операндов, участвующего в арифметической или логической операции;

Хранение результата предыдущей команды;

Хранение результата очередной операции;

Буфер операции ввода\вывода;

ОП – основная память – представляет собой массив запоминающих элементов, организованных в виде ячеек, способных хранить некую единицу информации. Каждая ячейка имеет уникальных адрес. Ячейки памяти организованы в виде матрицы. Выбор ячейки осуществляется путем подачи разрешающих сигналов на соответствующую строку и столбец матрицы. Это обеспечивается дешифратором, преобразующим поступивший из регистра адреса памяти адрес ячейки в разрешающие сигналы, подаваемые в горизонтальную и вертикальную линию, на пересечении которых расположена адресуемая ячейка.

В случае использования нескольких микросхем ЗУ процесс обращения к ячейке состоит из выбора нужной микросхемы (на основании старших разрядов адреса) и выбора ячейки внутри микросхемы (на основании младших разрядов адреса).

Модуль ввод/вывода

Портом называют схему, ответственную за передачу информации из периферийного устройства ввода в аккумулятор АЛУ (порт ввода) или из аккумулятора на периферийное устройство вывода (порт вывода).

ДВВ – дешифратор номера порта ввода/вывода – в модуле ввода вывода предполагается, что каждое периферийное устройство подключено к своему порту. Каждый порт имеет уникальных номер, который указывается в адресной части команды ввода/вывода. Дешифратор номера порта обеспечивает преобразование номера впорта в сигнал, разрешающий операции ввода или вывода на соответствующий порт.

Алгоритм работы процессора.

Цикл команды – это действия, требуемые для выборки и выполнения команды.

В общем случае цикл команды состоит из следующих этапов:

Выбор команды;

Цикл команды начинается с того, что центральный процессор извлекает из памяти по адресу, хранящемуся в счетчике команд. Двоичный код команды помещается в регистр команды и с этого момента становится видимым для процессора. Если команда занимает две или более ячеек, то этап выборки команды можно считать завершенным лишь после того, как в регистр команды будет помещен полный код.