- •Классификация Флинна

- •Дополнения Ванга и Бриггса к классификации Флинна

- •Классификация Фенга

- •Последовательные шины на базе i2c

- •Классификация прерываний

- •Порядок обслуживания прерываний

- •Регистры общего назначения

- •Сегментные регистры

- •Регистры состояния и управления

- •Устройства печати

- •Структура буфера клавиатуры

- •Асинхронный режим передачи

- •Управление потоком данных

- •Шина pci

- •Адресация устройств pci

- •Протокол шины pci

- •Определение понятия "архитектура"

- •Архитектура системы команд. Классификация процессоров (cisc и risc)

- •Параллельный интерфейс.

- •Интерфейс Centronics

- •Сигналы интерфейса Centronics

- •Стандартный параллельный порт пк

Протокол шины pci

В каждой транзакции (обмене по шине) участвуют два устройства — инициатор (initiator) обмена, он же ведущее (master) устройство, и целевое (target) устройство (ЦУ), оно же ведомое (slave). Шина PCI все транзакции трактует как пакетные: каждая транзакция начинается фазой адреса, за которой может следовать одна или несколько фаз данных. Состав и назначение интерфейсных сигналов шины приведены в табл. 1.

Таблица 1. Состав и назначение интерфейсных сигналов шины PCI.

|

Сигнал |

Назначение |

|

AD[31:0] |

Address/Data — мультиплексированная шина адреса/данных. В начале транзакции передается адрес, в последующих тактах —данные |

|

С/ВЕ[3:0]# |

Command/Byte Enable — команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла шины, задается четырехбитным кодом в фазе адреса |

|

FRAME# |

Кадр. Введением сигнала отмечается начало транзакции (фаза адреса), снятие сигнала указывает на то, что последующий цикл передачи данных является последним в транзакции |

|

DEVSEL# |

Device Select — устройство выбрано (ответ ЦУ на адресованную к нему транзакцию) |

|

IRDY# |

Initiator Ready — готовность ведущего устройства к обмену данными |

|

TRDY |

Target Ready — готовность ЦУ к обмену данными |

|

STOP# |

Запрос ЦУ к ведущему устройству на остановку текущей транзакции |

|

LOCK# |

Сигнал захвата шины для обеспечения целостного выполнения операции. Используется мостом, которому для выполнения одной операции требуется выполнить несколько транзакций PCI |

|

REQ# |

Request — запрос от ведущего устройства на захват шины |

|

GNT# |

Grant — предоставление ведущему устройству управления шиной |

|

PAR |

Parity — общий бит паритета для линий AD[31:0] и С/ВЕ[3:0]# |

|

PERR# |

Parity Error — сигнал об ошибке паритета (для всех циклов, кроме специальных). Вырабатывается любым устройством, обнаружившим ошибку |

|

РМЕ# |

Power Management Event — сигнал о событиях, вызывающих изменение режима потребления (дополнительный сигнал, введенный в PCI 2.2) |

|

CLKRUN# |

Clock running — шина работает на номинальной частоте синхронизации. Снятие сигнала означает замедление или остановку синхронизации с целью снижения потребления (для мобильных применений) |

|

PRSNT[1,2]# |

Present — индикаторы присутствия платы, кодирующие запрос потребляемой мощности. На карте расширения одна или две линии индикаторов соединяются с шиной GND, что воспринимается системной платой |

|

RST# |

Reset — сброс всех регистров в начальное состояние |

|

IDSEL |

Initialization Device Select — выбор устройства в циклах конфигурационного считывания и записи |

|

SERR# |

System Error — системная ошибка. Ошибка паритета адреса данных в специальном цикле или иная катастрофическая ошибка, обнаруженная устройством. Активизируется любым устройством PCI и вызывает NMI |

|

REQ64# |

Request 64 bit — запрос на 64-битный обмен. Сигнал вводится 64-битным инициатором, по времени он совпадает с сигналом FRAME*. Во время окончания сброса (сигналом RST*) сигнализирует 64-битному устройству о том, что оно подключено к 64-битной шине. Если 64-б.итное устройство не обнаружит этого сигнала, оно должно переконфигурироваться на 32-битный режим, отключив буферные схемы старших байтов

|

|

АСК64# |

Подтверждение 64-битного обмена. Сигнал вводится 64-битным ЦУ, опознавшим свой адрес, одновременно с DEVSEL*. Отсутствие этого подтверждения заставит инициатор выполнять обмен с 32-битной разрядностью

|

|

INTA#, INTB# INTC#, INTD# |

А, В, С, D — линии запросов прерывания, чувствительность к уровню, активный уровень — низкий, что допускает разделяемость (совместное использование)линий |

|

CLK |

Clock — тактовая частота шины. Должна лежать в пределах 20—33 МГц, В PCI2.1— до 66 МГц |

|

M66EN |

66MHz Enable — разрешение частоты синхронизации до 66 МГц |

|

SDONE |

Snoop Done — сигнал завершенности цикла слежения для текущей транзакции. Низкий уровень указывает на незавершенность цикла слежения за когерентностью памяти и кэша. Необязательный сигнал, используется только устройствами шины с кэшируемой памятью |

|

SBO# |

Snoop Backoff — попадание текущего обращения к памяти абонента шины в модифицированную строку кэша. Необязательный сигнал, используется только абонентами шины с кэшируемой памятью при алгоритме обратной записи |

|

ТСК |

Test Clock — синхронизация тестового интерфейса JTAG |

|

TDI |

Test Data Input — входные данные тестового интерфейса JTAG |

|

TDO |

Test Data Output — выходные данные тестового интерфейса JTAG |

|

TMS |

Test Mode Select — выбор режима для тестового интерфейса JTAG |

|

TRST |

Test Logic Reset — сброс тестовой логики |

В каждый момент времени шиной может управлять только одно ведущее устройство, получившее на это право от арбитра. Каждое ведущее устройство имеет пару сигналов — REQ# для запроса на управление шиной и GNT# для подтверждения предоставления управления шиной. Устройство может начинать транзакцию (устанавливать сигнал FRAME#) только при активном полученном сигнале GNT#. Снятие сигнала GNT* не позволяет устройству начать следующую транзакцию, а при определенных условиях (см. ниже) заставляет прекратить начатую транзакцию. Арбитражем запросов на использование шины занимается специальный узел, входящий в чипсет системной платы. Схема приоритетов (фиксированный, циклический, комбинированный) определяется программированием арбитра.

Для адреса и данных используются общие мультиплексированные линии AD. Четыре мультиплексированные линии С/ВЕ[3:0] обеспечивают кодирование команд в фазе адреса и разрешения байт в фазе данных. В начале транзакции ведущее устройство активизирует сигнал FRAME#, по шине AD передает целевой адрес, а по линиям С/ВЕ# — информацию о типе транзакции (команде). Адресованное ЦУ отзывается сигналом DEVSEL#. Ведущее устройство указывает на свою готовность к обмену данными сигналом IRDY#, эта готовность может быть выставлена и раньше получения DEVSEL#. Когда к обмену данными будет готово и ЦУ, оно установит сигнал TRDY#. Данные по шине AD передаются только при одновременном наличии сигналов IRDY# и TRDY#. С помощью этих сигналов ведущее устройство и ЦУ согласуют свои скорости, вводя такты ожидания. На рис. 1 приведена временная диаграмма обмена, в которой и ведущее устройство, и ЦУ вводят такты ожидания. Если бы они оба ввели сигналы готовности в конце фазы адреса и не снимали их до конца обмена, то в каждом такте после фазы адреса передавались бы по 32 бита данных, что обеспечило бы выход на предельную производительность обмена.

Количество фаз данных в пакете явно не указывается, но перед последней фазой данных ведущее устройство при введенном сигнале IRDY# снимает сигнал FRAME#. В одиночных транзакциях сигнал FRAME# активен лишь один такт. Если устройство не поддерживает пакетные транзакции в ведомом режиме, то оно должно потребовать прекращения пакетной транзакции во время первой фазы данных (введя сигнал STOP# одновременно с TRDY#). В ответ на это ведущее устройство завершит данную транзакцию и продолжит обмен последующей транзакцией с новым значением адреса. После последней фазы данных ведущее устройство снимает сигнал IRDY#, и шина переходит в состояние покоя (PCI Idle) — оба сигнала FRAME# и IRDY# находятся в пассивном состоянии. Инициатор может начать следующую транзакцию и без такта покоя, введя FRAME# одновременно со снятием IRDY#. Такие быстрые смежные транзакции (Fast Back-to-Back) могут быть обращены как к одному, так и к разным ЦУ. Первый тип поддерживается всеми устройствами PCI, выступающими в роли ЦУ. Инициатору разрешают (если он умеет) использовать быстрые смежные транзакции с разными устройствами (битом 9 регистра команд), только если все агенты шины допускают быстрые обращения.

Рис. 1. Цикл обмена на шине PCI

Протокол квитирования обеспечивает надежность обмена — ведущее устройство всегда получает информацию об отработке транзакции ЦУ. Средством повышения надежности (достоверности) является применение контроля паритета: линии AD[31:0] и С/ВЕ[3:0]# и в фазе адреса, и в фазе данных защищены битом паритета PAR (количество единичных бит этих линий, включая PAR, должно быть четным). Действительное значение PAR появляется на шине с задержкой в один такт относительно линий AD и С/ВЕ#. При обнаружении ошибки ЦУ вырабатывается сигнал PERR# (со сдвигом на такт после действительности бита паритета). В подсчете паритета при передаче данных учитываются все байты, включая и недействительные (отмеченные высоким уровнем сигнала С/ВЕх#). Состояние бит, даже и в недействительных байтах данных, во время фазы данных должно оставаться стабильным.

Каждая транзакция на шине должна быть завершена планово или прекращена, при этом шина должна перейти в состояние покоя (сигналы FRAME# и IRDY# пассивны). Завершение транзакции выполняется либо по инициативе ведущего устройства, либо по инициативе ПУ. Ведущее устройство может завершить транзакцию одним из следующих способов:

Нормальное завершение ( Camletiori) выполняется по окончании обмена данными.

Завершение по тайм-ауту (Time-out) происходит, когда во время транзакции у ведущего устройства отбирают право на управление шиной (снятием сигнала GNT#) и истекает время, указанное в его таймере Latency Timer. Это может случиться, если адресованное ЦУ оказалось непредвиденно медленным или запланирована слишком длинная транзакция. Короткие транзакции (с одной - двумя фазами данных) даже в случае снятия сигнала GNT# и срабатывания таймера завершаются нормально.

Транзакция отвергается (Master-Abort), когда в течение заданного времени ведущее устройство не получает ответа ЦУ (DEVSEL#).

Транзакция может быть прекращена по инициативе ЦУ; для этого оно может ввести сигнал STOP#. Возможны три типа прекращения:

Повтор (Retry) — сигнал STOP# вводится при пассивном сигнале TRDY# до первой фазы данных. Эта ситуация возникает, когда ЦУ из-за внутренней занятости не успевает выдать первые данные в положенный срок (16 тактов). Повтор является указанием ведущему устройству на необходимость нового запуска той же транзакции.

Отключение (Disconnect) — сигнал STOP# вводится во время или после первой фазы данных. Если сигнал STOP# введен при активном сигнале TRDY# очередной фазы данных, то эти данные передаются и на том транзакция завершается. Если сигнал STOP# введен при пассивном сигнале TRDY#, то транзакция завершается без передачи данных очередной фазы. Отключение производится, когда ЦУ неспособно своевременно выдать или принять очередную порцию данных пакета.

Отказ (Target-Abort) — сигнал STOP# вводится одновременно со снятием сигнала DEVSEL# (в предыдущих случаях во время появление сигнала STOP# сигнал DEVSEL# был активен). После этого данные уже не передаются. Отказ вводится, когда ЦУ обнаруживает фатальную ошибку или иные условия, по которым оно уже никак не сможет обслужить данный запрос.

Команды шины, адресация памяти и ввода-вывода

В каждой команде шины указывается адрес данных, передаваемых в первой фазе данных пакета. Адрес для каждой последующей фазы данных пакета увеличивается на 4 (следующее двойное слово), но в командах обращения к памяти порядок может быть иным (см. ниже). Байты шины AD, несущие действительную информацию, выбираются сигналами С/ВЕ[3:0]# в фазах данных. Внутри пакета эти сигналы могут менять состояние от фазы к фазе произвольным образом. Разрешенные байты могут быть разрозненными; возможны фазы данных, в которых не разрешено ни одного байта. В отличие от шины ISA, на PCI нет динамического изменения разрядности — все устройства должны подключаться к шине 32-разрядным способом. Если в устройстве PCI применяются функциональные схемы иной разрядности (к примеру, нужно подключить микросхему 8255, имеющую 8-битную шину данных и четыре регистра), то приходится принимать схемотехнические методы преобразования, отображающие все регистры на 32-разрядную шину AD.

Адресация памяти, портов и конфигурационных регистров различна.

♦ В циклах обращения к памяти адрес, выровненный по границе двойного слова, передается по линиям AD[31:2]; линии AD[1:0] задают порядок адресов в пакете:

00 — линейное инкрементирование; адрес последующей фазы отличается от предыдущего на число байтов шины (4 для 32-битной и 8 для 64-битной шины).

10 — Cacheline Wrap mode, сворачивание адресов с учетом длины строки кэш-памяти. В транзакции адрес для очередной фазы увеличивается до достижения границы строки кэша, после чего переходит на начало этой строки и увеличивается до адреса, предшествующего начальному. Если транзакция длиннее строки кэша, то она продолжится в следующей строке с того же смещения, что и началась. Так, при длине строки 16 байт и 32-битной шине транзакция, начавшаяся с адреса xxxxxxOSh, будет иметь последующие фазы данных, относящиеся к адресам xxxxxxOCh, xxxxxxOOh, xxxxxx04h; и далее к xxxxxxlSh, xxxxxxlCh, xxxxxxlOh, xxxxxx!4h. Длина строки кэша прописывается в конфигурационном пространстве устройства (см. п. 6.2.12). Если устройства не имеет регистра Cache Line Size, то оно должно прекратитьтранзакцию после первой фазы данных;

01 и 11 — зарезервировано, может использоваться как указание на отключение (Disconnect) после первой фазы данных.

В циклах обращения к портам ввода-вывода для адресации любого байта используются все линии AD[31:0]. При этом биты адреса AD[31:2] указывают на адрес двойного слова, к которому принадлежат передаваемые данные, а младшие биты адреса AD[1:0] должны соответствовать байтам, которые могут быть разрешены сигналами С/ВЕ[3:0]#. При AD[1:0]=00 допустимо С/ВЕ[3:0]# - хххО или 1111, приАО[1:0]«01-С/ВЕ[3:0]# = хх01или1111,приАО[1:0]=10-С/ВЕ[3:0]# = х011 или 1111, при AD[1:0]=11 — С/ВЕ[3:0]# = 0111 (передается лишь байт 3) или 1111 (ни один байт не разрешен). Эти циклы тоже могут быть пакетными, хотя на практике эта возможность используется редко.

В циклах конфигурационной записи/считывания устройство (карта расширения) выбирается индивидуальным сигналом IDSEL; функция адресуется битами AD[10:8], а конфигурационные регистры (только двойные слова) адресуются битами AD[7:2], при этом AD[1:0]=00.

Команды шины PCI определяются значениями бит С/ВЕ# в фазе адреса.

Команда подтверждения прерывания предназначена для чтения вектора прерываний. По протоколу она выглядит как команда чтения, неявно адресованная к системному контроллеру прерываний. Здесь в фазе адреса по шине AD полезная информация не передается, но ее инициатор (главный мост) должен обеспечить стабильность сигналов и корректность паритета. В PC 8-битный вектор передается в байте 0 по готовности контроллера прерываний (по сигналу TRDY#). Подтверждение прерываний выполняется за один цикл (первый холостой цикл, который процессоры х86 делают в дань совместимости со стариной, мостом подавляется).

Специальный цикл отличается от всех других тем, что является широковещательным. Однако ни один агент на него не отвечает, а главный мост или иное устройство, вводящее этот цикл, всегда завершает его способом Master Abort (на него требуется 6 тактов шины). Специальный цикл предназначен для генерации широковещательных сообщений — их могут читать любые «заинтересованные» агенты шины. Тип сообщения декодируется содержимым линий AD[15:0], на линиях AD[31:16] могут помещаться данные, передаваемые в сообщении. Фаза адреса в этом цикле для обычных устройств отсутствует, но мосты используют ее информацию для управления распространением сообщения. Сообщения с кодами OOOOh, 000lh и 0002h требуются для указания на отключение (Shutdown), остановку (Halt) процессора или специфические функции процессора х8б, связанные с кэшем и трассировкой. Коды 0003-FFFFh зарезервированы. Специальный цикл может генерироваться тем же аппаратно-программным механизмом, что и конфигурационные циклы (см. п. 6.2.11),но со специфическим значением адреса.

Команды чтения и записи ввода-вывода служат для обращения к пространству портов. Линии AD содержат адрес байта, причем декодированию подлежат и биты ADO и AD1 (несмотря на то, что имеются сигналы ВЕх#). Порты PCI могут быть 16- или 32-битными. Для адресации портов на шине PCI доступны все 32 бита адреса, но процессоры х86 могут использовать только младшие 16 бит.

Команды обращения к памяти, кроме обычного чтения и записи, включают чтение строк кэш-памяти, множественное чтение (нескольких строк), запись с инвалидацией.

Команды конфигурационного чтения и записи адресуются к конфигурационному пространству устройств (см. п. 6.2.12). Обращение производится только двойными словами. Структура содержит идентификатор устройства и производите для, состояние и команду, информацию о занимаемых ресурсах и ограничения на использование шины. Для генерации данных команд требуется специальный аппаратно-программный механизм (см. п. 6.2.11).

Чтение строк памяти применяется, когда в транзакции планируется более двух 32-битных передач (обычно это чтение до конца строки кэша).

Множественное чтение памяти используется для транзакций, пересекающих границы строк кэш-памяти.

Запись с инвалидацией применяется к целым строкам кэша и позволяет оптимизировать циклы обратной записи «грязных» строк кэша.

♦ Двухадресный цикл позволяет по 32-битной шине обращаться к устройствам с 64-битной адресацией. В этом случае младшие 32 бита адреса передаются в цикле данного типа, а за ним следует обычный цикл, определяющий тип обмена и несущий старшие 32 бита адреса. Шина PCI допускает 64-битную адресацию портов ввода-вывода (для х86 это бесполезно, но PCI существует и на других платформах).

С/ВЕ[3:0] Тип команды

0000 Interrupt

Acknowledge

— подтверждение прерывания

0000 Interrupt

Acknowledge

— подтверждение прерывания

0001 Special Cycle — специальный цикл

0010 I/O Read — чтение порта ввода-вывода

0011 I/O Write —запись в порт ввода-вывода

0100 Зарезервировано

0101 Зарезервировано

0110 Memory Read — чтение памяти

0111 Memory Write — запись в память

1000 Зарезервировано

1001 Зарезервировано

1010 Configuration Read — конфигурационное считывание

1011 Configuration Write — конфигурационная запись

1100 Multiple Memory Read — множественное чтение памяти

1101 Dual Address Cycle (DAC) — двухадресный цикл

1110 Memory-Read Line — чтение строки памяти

1111 Memory Write and Invalidate — запись с инвалидацией.

Организация прямого доступа к памяти. Цель, реализация и задачи управления контроллера прямого доступа к памяти.

Прямой доступ к памяти (ПДП) является одним из способов обмена данными с ПУ. В этом режиме обмен данными между ПУ и памятью микропроцессорной системы происходит без участия процессора. Обменом в режиме ПДП управляет не программа, выполняемая процессором, а внешнее по отношению к процессору специальное устройство, называемое контроллером ПДП (КПДП). ПДП используется для быстрого ввода/вывода блоков данных и разгрузки процессора от управления операциями ввода/вывода. Обмен блоками данных с помощью программно-управляемого обмена осуществляется относительно медленно, так как на обмен каждым байтом затрачивается несколько команд процессора. ПДП освобождает процессор от управления операциями ввода/вывода, позволяя тем самым осуществлять параллельно во времени выполнение процессором программы с обменом данными между ПУ и памятью, производить этот обмен со скоростью, ограниченной только пропускной способностью памяти или ПУ. Таким образом, ПДП, разгружая процессор от обслуживания операций ввода/вывода, способствует возрастанию общей производительности микропроцессорной системы.

Для реализации режима ПДП необходимо обеспечить непосредственную связь контроллера ПДП и памяти микропроцессорной системы, т.е. специальный информационный канал, по которому осуществляется обмен в режиме ПДП, – канал ПДП. Для этой цели можно использовать специально выделенную магистраль, связывающую контроллер ПДП с памятью. Однако такое решение нельзя признать оптимальным, так как это приведет к значительному усложнению микропроцессорной системы в целом, особенно при подключении нескольких ПУ. С целью сокращения количества линий в шинах микропроцессорной системы контроллер ПДП подключается к памяти посредством шин системной магистрали. При этом возникает проблема совместного использования шин системной магистрали процессором и контроллером ПДП. Можно выделить два основных способа ее решения:

реализация обмена в режиме ПДП с захватом цикла;

реализация обмена в режиме ПДП с блокировкой процессора.

Существует две разновидности прямого доступа к памяти с захватом цикла. Наиболее простой способ организации ПДП состоит в том, что для обмена используются те циклы процессора, в которых он не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора. Однако возникает необходимость выделения таких циклов, чтобы не произошло временного перекрытия обмена ПДП с операциями обмена, инициируемыми процессором. В некоторых процессорах формируется специальный управляющий сигнал, указывающий циклы, в которых процессор не использует память. Если процессор не формирует такого сигнала, то для выделения свободных циклов необходимо применение в контроллере ПДП специальной схемы, что приводит к усложнению последнего. Применение этого способа организации ПДП не снижает производительности системы, но при этом обмен в режиме ПДП возможен только в случайные моменты времени одиночными словами.

Наиболее распространенным является ПДП с захватом цикла и принудительным отключением процессора от шин системной магистрали. Для реализации такого режима ПДП системная магистраль дополняется двумя управляющими сигналами – «Требование прямого доступа к памяти» HOLD и «Предоставление прямого доступа к памяти» HLDA.

Управляющий сигнал HOLD формируется контроллером ПДП. Процессор, получив этот сигнал, приостанавливает выполнение текущей команды, не дожидаясь ее завершения, отключается от шин системной магистрали и выдает контроллеру ПДП управляющий сигнал HLDA. С этого момента все шины системной магистрали управляются контроллером ПДП. Контроллер ПДП, используя шины системной магистрали, осуществляет обмен одним словом данных с памятью и затем, сняв сигнал HOLD, возвращает управление системной магистралью процессору. Как только контроллер ПДП будет готов к обмену следующим словом данных, он вновь захватывает цикл процессора и т.д. В промежутках между захватами циклов контроллером ПДП процессор продолжает выполнять команды программы. Тем самым выполнение программы замедляется, но значительно в меньшей степени, чем при обмене в режиме прерывания.

Передача блока данных с использованием ПДП предполагает выполнение определенной последовательности действий (рис. 32):

начальная установка (предварительная подготовка) контроллера ПДП;

запуск контроллера ПДП;

многократное занятие цикла процессора;

завершение обмена.

Рис. 32 – Алгоритм передачи блока данных с использованием контроллера ПДП

Программа используется только для начальной установки и пуска обмена через канал ПДП. После этого процессор может выполнять основную программу, которая не связана с обменом. Во время выполнения этой программы каждый раз при поступлении запроса на ПДП контроллер ПДП будет занимать цикл процессора, и осуществлять передачу. После окончания обмена для передачи управления программе завершения обмена в режиме ПДП используется прерывание. Затем основная программа может быть продолжена.

Рассмотрим организацию контроллера ПДП, обеспечивающего ввод данных в память микропроцессорной системы в режиме ПДП (рис. 33).

Рис. 33 – Организация контроллера ПДП

Начальная подготовка к обмену в режиме ПДП состоит в выделении ПУ области памяти, используемой при обмене, и указании ее размера, т.е. количества записываемых в память или читаемых из памяти слов информации. Следовательно, контроллер ПДП должен иметь в своем составе регистр адреса и счетчик слов. Перед началом обмена с ПУ в режиме ПДП процессор должен выполнить программу загрузки, которая обеспечивает запись в указанные регистры контроллера ПДП начального адреса выделенной ПУ памяти и ее размера в словах заданной разрядности.

Таким образом, перед началом ввода из ПУ очередного блока данных процессор загружает в регистры контроллера ПДП следующую информацию: в счетчик слов – количество принимаемых слов, а в регистр адреса – начальный адрес области памяти для вводимых данных. Тем самым контроллер подготавливается к выполнению операции ввода данных из ПУ в память в режиме ПДП.

Запуск контроллера ПДП осуществляется командой вывода, по которой устанавливается в 1 триггер пуска. Триггер пуска подключает ПУ к контроллеру ПДП. После команды пуска контроллера ПДП должна быть команда разрешения прерывания. В дальнейшем ввод блока данных через канал ПДП осуществляется без участия команд программы.

Когда ПУ подготовит слово данных, оно посылается в регистр данных контроллера. При этом каждое слово сопровождается управляющим сигналом из ПУ «Ввод данных», который обеспечивает запись слова данных в регистр данных контроллера. По этому же сигналу (при установленном в 1 триггере пуска) устанавливается в 1 триггер запроса, сигнал с выхода которого поступает на вход процессора «Требование прямого доступа к памяти» HOLD. После формирования процессором ответного сигнала «Предоставление прямого доступа к памяти» HLDA следующий машинный цикл занимается под обмен. При этом осуществляется одна пересылка слова данных в ячейку памяти по адресу, находящемуся в регистре адреса контроллера. По сигналу HLDA контроллер выставляет на шины адреса и данных системной магистрали содержимое своих регистров адреса и данных соответственно. Формируя управляющий сигнал MEMWR, контроллер ПДП обеспечивает запись слова данных из своего регистра данных в память. Сигнал «Предоставление прямого доступа к памяти» HLDA используется в контроллере также для выполнения трех операций:

сброса триггера запроса;

увеличения содержимого регистра адреса на 1;

уменьшения содержимого счетчика слов на 1.

По каждому сигналу HLDA из содержимого счетчика слов вычитается 1, и когда оно становится равным 0, устанавливается в 1 триггер окончания передачи блока данных, сигнал с выхода которого используется в качестве запроса на прерывание и поступает на соответствующий вход процессора. Процессор прерывает выполнение программы и передает управление подпрограмме обработки прерывания для завершения обмена.

Завершение обмена осуществляется путем отключения ПУ от контроллера ПДП командой вывода, по которой сбрасывается в 0 триггер пуска. Кроме того, аналогичным образом сбрасывается в 0 триггер окончания передачи блока данных. По окончании обработки прерывания управление возвращается основной программе.

Если нет необходимости продолжать выполнение некоторой программы параллельно с передачей в режиме ПДП, используется в качестве сигнала готовности, который доступен процессору через регистр состояния контроллера ПДП. В этом случае прерывание не используется (выход триггера окончания передачи не подключается к входу запроса на прерывание процессора или прерывание в процессоре запрещается). В течение обмена через канал ПДП процессор находится в цикле ожидания окончания передачи, опрашивая соответствующий разряд готовности регистра состояния контроллера ПДП по команде ввода. Как только процессор обнаружит готовность, он переходит к процедуре завершения обмена (шаг 4 рассмотренной выше последовательности), после чего выполнение программы продолжается.

Завершение обмена путем отключения ПУ от контроллера ПДП – сброс в 0 триггера пуска – может осуществляться не по команде вывода в подпрограмме обработки прерывания, а автоматически, когда содержимое счетчика слов становится равным 0 (также как и установка в 1 триггера окончания передачи). В этом случае в контроллере ПДП отпадает необходимость в триггере пуска, а подключение/отключение ПУ к контроллеру осуществляется в зависимости от состояния счетчика слов. При загрузке в счетчик количества принимаемых слов сигнал «0=» устанавливается в 1 и подключает ко входу S триггера запроса управляющий сигнал из ПУ «Ввод данных». После передачи всех слов содержимое счетчика становится равным 0, сигнал «0=» сбрасывается в 0 и запрещает поступление управляющего сигнала из ПУ «Ввод данных» на вход S триггера запроса, отключая тем самым ПУ от контроллера ПДП.

Выше были рассмотрены только процесс подготовки контроллера ПДП и непосредственно передача данных в режиме ПДП. На практике любой сеанс обмена данными с ПУ в режиме ПДП всегда включает также и этап подготовки ПУ к обмену. На этом этапе процессор в режиме программно-управляемого обмена опрашивает состояние ПУ, проверяя его готовность к обмену, и посылает в ПУ команды, обеспечивающие его подготовку к обмену данными по каналу ПДП. Такая подготовка может сводиться, например, к перемещению головок на требуемую дорожку в НМД. Затем выполняется загрузка регистров контроллера ПДП, после чего обмен данными в режиме ПДП начинается либо по инициативе контроллера ПДП, как это было рассмотрено выше, либо по инициативе ПУ.

Следует отметить, что использование в микропроцессорной системе обмена в режиме ПДП с захватом цикла требует от программиста очень ясного понимания процессов, происходящих в системе при выполнении программы, и четкой синхронизации процесса выполнения программы и ввода /вывода по каналу ПДП.

Прямой доступ к памяти с блокировкой процессора отличается от режима ПДП с захватом цикла тем, что управление системной магистралью передается контроллеру ПДП не на время передачи одного слова, а на время обмена блоком данных. Такой режим ПДП необходим в тех случаях, когда время между двумя сигналами «Требование прямого доступа к памяти» HOLD сопоставимо с циклом процессора. В этом случае процессор не успевает выполнить хотя бы одну команду между очередными операциями обмена в режиме ПДП.

В микропроцессорной системе можно использовать несколько ПУ, работающих в режиме ПДП. Предоставление таким ПУ шин системной магистрали для обмена данными производится на приоритетной основе. В этом случае приоритеты ПУ реализуются так же, как и при обмене данными в режиме прерывания. Как правило, для каждого ПУ используется своя пара управляющих сигналов «Требование прямого доступа к памяти» HOLD и «Предоставление прямого доступа к памяти» HLDA и отдельный канал в контроллере ПДП.

Фон-неймановская (принстонская) и гарвардская архитектуры. Организация пространств памяти и ввода-вывода. Основные методы снижения энергопотребления микропроцессорных ЭВМ.

Под организацией понимают состав компонентов (аппаратных или программных средств), связи между ними и их функциональные характеристики.

ЭВМ имеет многоуровневую иерархическую организацию со своими составными компонентами на каждом уровне:

1) нижний уровень − уровень физических компонентов − физическая организация (представляется в виде принципиальной схемы);

2) уровень реализуемых в ЭВМ функций − логическая (функциональная) организация (представляется в виде функциональной схемы);

3) верхний уровень − уровень аппаратуры (состав, функциональные связи и характеристики аппаратных модулей) − структурная организация (представляется в виде структурной схемы).

Все компоненты микропроцессорной системы представляются для процессора в виде набора ячеек памяти или портов ввода/вывода, которые образуют два основных пространства: соответственно пространство памяти и пространство ввода/вывода.

Фон-неймановская (принстонская) и гарвардская архитектуры. В большинстве современных микропроцессорных систем для хранения программ и данных используется общая шина памяти. Такая организация получила название архитектуры Дж. фон Неймана, предложившего кодирование программ в формате, соответствующем формату данных. ЭВМ с такой архитектурой называют машинами фон-неймановского или принстонского типа. В них области для хранения программ (Program Space – PS) и данных (Data Space – DS) образуют единое пространство и могут размещаться в любом месте общей памяти. При этом нет никаких признаков, указывающих на тип информации в ячейке памяти. Содержимое ячейки интерпретируется ЦП, и задача программиста − следить за тем, чтобы данные и программа обрабатывались по-разному. Фон-неймановская архитектура характерна для универсальных МП.

В специализированных МП и микроконтроллерах используется другая схема, известная как архитектура Гарвардской лаборатории или гарвардская архитектура. В ее классическом варианте программы и данные хранятся в двух раздельных памятях, что позволяет полностью совмещать во времени выборку и исполнение команд. ЭВМ, спроектированные в соответствии с концепцией разделения памяти на два вида, называют машинами гарвардского типа. В таких системах память программ и память данных разделены и имеют свои собственные адресные пространства и способы доступа к ним. Программа находится всегда в одной памяти, а данные − в другой. Такое разделение позволяет повысить быстродействие и упростить схемотехническую реализации микропроцессорной системы.

Дальнейшее совершенствование архитектур обоих типов состояло в выделении специального пространства данных небольшого объема, которое представляет собой набор программно-доступных регистров (Register Space). В отличие от памяти и портов ввода/вывода регистры располагаются всегда внутри МП вместе с АЛУ, что обеспечивает быстрый физический доступ к информации, хранящейся в них. В некоторые интервалы времени программа наиболее интенсивно работает лишь с небольшим объемом данных. Для временного хранения этих данных и предназначена регистровая область – набор программно доступных регистров.

Регистровая область может быть как полностью изолирована от пространства данных DS, так и частично пересекаться с ним, что дает возможность рассматривать отдельные регистры МП как обычные ячейки памяти данных. Такая организация является целесообразной, если в МП поддерживается быстрый доступ ко всей или хотя бы к некоторой части памяти данных.

Все современные МП имеют регистровые области независимо от того, к какому типу они принадлежат: принстонскому или гарвардскому. Внутренняя логическая организация регистровой области очень разнообразна и зависит от типа МП. Функциональная структура регистровой области будет рассмотрена позже. Пока отметим в ее составе лишь один регистр, который называется программным счетчиком PC (Program Counter). Данный регистр является обязательным для всех МП и связан с адресацией памяти программ. Он служит указателем следующего элемента программной последовательности, подлежащего выборке и исполнению.

Пространство ввода/вывода представляет набор адресуемых буферных схем и регистров, которые называются портами и через которые осуществляется связь с внешними и внутренними аппаратными средствами микропроцессорной системы.

В микропроцессорной системе может использоваться два варианта организации пространства ввода-вывода:

изолированный ввод-вывод. Порты ввода/вывода размещены в специальном пространстве ввода/вывода (Input/Output Space – IOS), изолированном от других пространств данных. В этом случае МП имеет специальный набор команд ввода/вывода.

совмещенный ввод-вывод или ввод-вывод с отображением на память. В этом случае изолированное пространство ввода/вывода отсутствует, а в пространстве памяти данных DS выделяются области, в которых размещаются порты. Организация доступа к портам в такой микропроцессорной системе ничем не отличается от процесса обращения к данным в памяти.

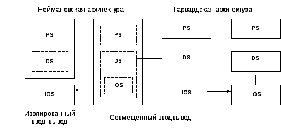

На рис. 4 представлены четыре типовых набора областей для хранения программ и данных. Стрелками показан процесс изоляции отдельных областей, приводящий к появлению нового типового набора. Все наборы существуют реально, каждый имеет свои преимущества и недостатки, учет которых позволяет создавать высокоэффективные системы различного назначения.

В отличие от регистровой области пространства памяти программ PS и данных DS, а также область ввода-вывода IOS организованы проще. Память представляет собой линейно упорядоченный набор n-разрядных ячеек с произвольным доступом (одномерный массив) − линейная память. Все ячейки пронумерованы, таким образом каждой ячейке набора соответствует число, называемое ее адресом. Все адреса занимают целочисленный диапазон от 0 до 2m-1 (m − разрядность адреса), который образует адресное пространство памяти. В большинстве случаев процессор может адресоваться к памяти с точностью до одного байта, т.е. наименьшей адресуемой единицей является байт и память имеет байтовую организацию.

Рис. 4 – Области микропроцессора для хранения программ и данных

Организация пространства памяти показана на рис. 5. При этом память изображается таким образом, чтобы ячейки со старшими адресами располагались ниже, чем с младшими. Нумерация отдельных разрядов в ячейке производится справа налево начиная с нуля, при этом разряд с нулевым номером является младшим.

Рис. 5 - Организация пространства памяти

Программные объекты (команды и операнды) могут иметь длину, превышающую один байт, например, два байта – 16-разрядное слово или просто слово, четыре байта – 32-разрядное слово или двойное слово, восемь байтов – 64-разрядное слово или учетверенное слово. Такие объекты располагаются в смежных ячейках пространства памяти, причем обычно младший байт размещается в ячейке с меньшим адресом. Адресом объекта служит наименьший из адресов ячеек, занимаемых им, т.е. в данном случае адрес его младшего байта. Такой порядок называется Little-Endian Memory Format. Он используется в микропроцессорах с архитектурой x86. В других семействах процессоров применяют и обратный порядок – Big-Endian Memory Format, в котором объекты располагаются в смежных ячейках памяти, начиная со старшего байта, а младшие байты размещаются в последующих ячейках (например, в микроконтроллерах семейства 68HC11 фирмы Motorola). В этом случае адресом объекта является адрес его старшего байта. Для взаимного преобразования форматов объектов в процессорах имеются специальные команды. Операция обращения к памяти предполагает считывание или запись всего объекта как единого целого. Например, 16-разрядные слова в памяти хранятся в двух соседних ячейках. Старший байт слова занимает ячейку с большим адресом, а младший − ячейку с меньшим адресом. При этом адрес младшего байта служит адресом слова (см. рис. 5).

Часто организация памяти предусматривает определенные ограничения на возможное расположение многобайтовых объектов. Например, слова в памяти могут находиться только по четным адресам. Тогда при доступе к слову значение младшего разряда его адреса, указывающего на байт в слове, во внимание не принимается, т.е. такая память имеет границу слов.

Например, в МП 8086 любые два смежных байта в памяти могут рассматриваться как 16-разрядное слово. Таким образом, слова данных можно свободно размещать по любому адресу, что позволяет экономить память благодаря её плотной упаковки. Однако для экономии времени выполнения программы целесообразно размещать слова данных в памяти по четным адресам, так как МП передает такие слова за один цикл шины. Слова с нечетными адресами (не выровненные) также допустимы, но для их передачи требуется уже два цикла шины, что снижает производительность МП. Особенно важно иметь выровненные слова для операций со стеком, так как в них участвуют только слова. Поэтому указатель стека SP необходимо всегда инициализировать на четный адрес. Команды в МП 8086 всегда выбираются словами по четным адресам, за исключением первой выборки после передачи управления по нечетному адресу, когда выбирается один байт. Поток команд разделяется на байты внутри МП, так что выравнивание команд не влияет на производительность и поэтому не используется.

В процессорах фирмы Intel, начиная с 486, на уровне привилегий 3 может быть включен контроль выравнивания операндов по соответствующей границе: слова по четному адресу, двойного слова по адресу, кратному четырем, учетверенного слова по адресу, кратному восьми. На уровнях привилегий 0, 1, 2 контроль выравнивания не производится.

Рассмотренная организация памяти соответствует нижнему (физическому) уровню представления памяти. Пространство ввода-вывода имеет такую же организацию. Существует более высокий (логический) уровень организации памяти, на котором работает программист и который связан с архитектурой процессораже.

Магистрально-модульный принцип организации микропроцессорной системы. Большинство современных микропроцессорных систем построено по магистрально-модулъному принципу. В соответствии с этим принципом память и подсистема ввода/вывода выполняются в виде отдельных функционально законченных модулей, которые подключаются к единой внутрисистемной магистрали.

В подсистеме памяти выделяют модули постоянных запоминающих устройств (ПЗУ), которые используются для хранения программ и констант, модули оперативных запоминающих устройств (ОЗУ), предназначенных для хранения переменных и загружаемого извне программ.

В составе подсистемы ВВ в простейшем случае выделяются адресуемые МП буферные схемы и регистры – порты ввода/вывода. Они предназначены для связи с простыми внешними устройствами, такими как светодиодные индикаторы, переключатели и т.п. Более сложные модули подсистемы ввода/вывода, предназначенные для управления внешним интерфейсным оборудованием и реализации специальных функций ввода/вывода, строятся на основе портов ввод/вывод и называются адаптерами или контроллерами периферийных устройств.

Наиболее сложными из модулей подсистемы ввода/вывода являются процессоры (сопроцессоры) ввода/вывода, которые работают по собственным программам, хранящимся в памяти, и по сути дела представляют собой отдельные микропроцессорные системы.

В зависимости от способа подключения отдельных модулей микропроцессорной системы к системной магистрали различают три типовые структуры микропроцессорных систем:

магистральная;

магистрально-каскадная;

магистрально-радиальная.

В магистральной структуре все модули подсистем памяти и ввода/вывода подключаются непосредственно к системной магистрали. Это наиболее простая структура. Недостатками магистральной структуры являются:

все модули должны поддерживать протокол обмена по системной магистрали и содержать средства сопряжения с ней, которые в зависимости от микропроцессора могут быть достаточно сложными;

небольшое быстродействие, т.к. медленные периферийные устройства могут надолго занимать системную магистраль.

В магистрально-каскадной и магистрально-радиальной структурах отдельные модули подключаются с помощью специальных контроллеров (адаптеров) шин, основное назначение которых – реализовать приоритетные соотношения при использовании магистрали.

В магистрально-каскадной структуре отдельные модули подключаются к контроллеру шины с помощью дополнительного общего канала, например, магистрали или шины ввода/вывода, т.е. по магистральной схеме. В магистрально-радиальной структуре каждый модуль подключается к контроллеру шины с помощью индивидуального канала, т.е. по радиальной схеме.

Архитектура с иерархией шин. В настоящее время примерно одинаковое распространение получили два способа построения вычислительных машин: с непосредственными связями и на основе шины.

В системах, построенных по первому способу, между взаимодействующими устройствами (процессор, память, устройство ввода/вывода) имеются непосредственные связи. Особенности связей (число линий в шинах, пропускная способность и т.п.) определяются видом информации, характером и интенсивностью обмена. Достоинством архитектуры с непосредственными связями можно считать возможность развязки узких мест путем улучшения структуры и характеристик только определенных связей, что экономически может быть наиболее выгодным решением. У фон-неймановских ЭВМ таким узким местом является канал пересылки данных между процессором и памятью, и развязать его достаточно непросто. Кроме того, системы с непосредственными связями плохо поддаются реконфигурации.

В варианте с общей шиной все устройства вычислительной машины подключаются к системной магистрали, служащей единственным трактом для потоков команд, данных и управления. Наличие общей шины существенно упрощает реализацию ЭВМ, позволяет легко менять состав и конфигурацию машины. Благодаря этим свойствам шинная архитектура получила широкое распространение в микроЭВМ. Вместе с тем, именно с шиной связан и основной недостаток архитектуры: в каждый момент передавать информацию по шине может только одно устройство. Основную нагрузку на шину создают обмены между процессором и памятью, связанные с извлечением из памяти команд и данных и записью в память результатов вычислений. На операции ввода/вывода остается лишь часть пропускной способности шины. Практика показывает, что даже при достаточно быстрой шине для 90% приложений этих остаточных ресурсов обычно не хватает, особенно в случае ввода или вывода больших массивов данных.

Поэтому при сохранении фон-неймановской концепции последовательного выполнения команд программы шинная архитектура в чистом ее виде оказывается недостаточно эффективной. Более распространена архитектура с иерархией шин, где помимо системной шины имеется еще несколько дополнительных шин. Они могут обеспечивать непосредственную связь между устройствами с наиболее интенсивным обменом, например процессором и кэш-памятью. Другой вариант использования дополнительных шин – объединение однотипных устройств ввода/вывода с последующим выходом с дополнительной шины на системную. Это позволяет снизить нагрузку на общую шину и более эффективно расходовать ее пропускную способность. Наибольшее распространение получили микропроцессорные системы с одной шиной, с двумя или тремя видами шин.

В структурах с одной шиной имеется одна системная шина, обеспечивающая обмен информацией между процессором и памятью, а также между устройствами ввода/вывода, с одной стороны, и процессором либо памятью – с другой. Для такого подхода характерны простота и низкая стоимость. Однако одношинная организация не в состоянии обеспечить высокую скорость обмена, причем узким местом становится именно шина.

Хотя контроллеры устройств ввода/вывода могут быть подсоединены непосредственно к системной шине, больший эффект достигается применением одной или нескольких шин ввода/вывода. Устройства ввода/вывода подключаются к шинам ввода/вывода, которые берут на себя основной обмен, не связанный с выходом на процессор или память. Подключение осуществляется с помощью адаптеров шин, которые обеспечивают буферизацию данных при их пересылке между системной шиной и контроллерами устройств ввода/вывода. Это позволяет микропроцессорной системе поддерживать работу множества устройств ввода/вывода и одновременно развязать обмен информацией по тракту процессор-память и обмен информацией с устройствами ввода/вывода. Подобная схема существенно снижает нагрузку на скоростную шину процессор-память и способствует повышению общей производительности микропроцессорной системы.

Для подключения быстродействующих периферийных устройств в систему шин может быть добавлена высокоскоростная шина расширения. Шины ввода/вывода подключаются к шине расширения, а уже с нее через адаптер к шине процессор-память. Схема еще более снижает нагрузку на шину процессор-память. Такую организацию шин называют архитектурой с «пристройкой» (mezzanine architecture).

Особенности организации архитектур CISC и RISC. Основные достоинства и недостатки.