Семейство микроконтроллеров MSP430X1XX, руководство пользователя (2004)

.pdf

MSP430x1xxFamily

АЦП10

Модуль АЦП10 представляет собой высокоэффективный 10-разрядный аналого-цифровой преобразователь. В этом разделе описывается АЦП10. АЦП10 реализован в устройствах MSP430x11x2 и MSP430x12x2.

18.1. Введение в АЦП10

Модуль АЦП10 обеспечивает быстрые 10-разрядные аналого-цифровые преобразования. Модуль имеет 10-разрядное ядро с регистром последовательного приближения SAR, схему выборки, опорный генератор и контроллер переноса данных (DTC).

DTC позволяет выборкам АЦП10 преобразовываться и сохраняться в любом месте памяти без вмешательства ЦПУ. Модуль может конфигурироваться программным обеспечением пользователя для поддержки разнообразных приложений.

АЦП10 обладает следующими возможностями:

•Максимальная скорость преобразования свыше 200 ksps (200000 преобразований в сек.)

•Монотонный 10-разрядный преобразователь без ошибочных кодов

•Выборка и хранение с программируемыми периодами выборки

•Преобразование инициируется программным обеспечением или таймером А

•Программно выбираемый интегрированный генератор опорного напряжения (1,5 В или 2,5 В)

•Программно выбираемый внутренний или внешний опорный источник

•Восемь индивидуально конфигурируемых внешних входных каналов

•Каналы преобразования для внутреннего температурного датчика, AVCC и внешних опорных источников

•Выбираемый источник тактирования преобразований

•Одноканальный, повторный одноканальный, последовательный и пов- торно-последовательный режимы преобразования

•Ядро АЦП и опорное напряжение могут выключаться раздельно

•Контроллер переноса данных для автоматического сохранения результатов преобразований

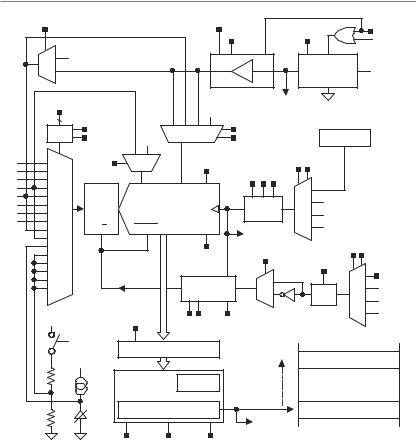

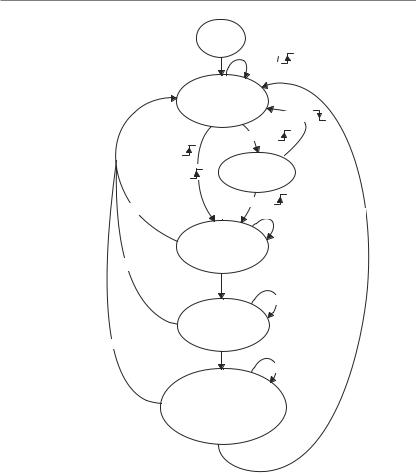

Блок-схема АЦП10 показана на рис. 18-1.

332 |

|

Библиотека Компэла |

|

Раздел XVIII. |

|

|

|

|

|

|

|

|

|

|

АЦП10 |

|

|

REFOUT |

Ve REF+ |

|

|

|

REFBURST |

|

|

|

|

|

|

|

|

|

|

|

|

ADC10SR |

|

2_5V |

REFON |

|||

|

|

|

|

|

|

|

|

|

|

|

|

INCHx=0Ah |

|

0 |

V REF+ |

|

|

|

|

|

|

|

|

Включение |

|

|

1 |

|

|

|

|

|

|

|

Опорный источник |

A VCC |

||

|

|

|

|

|

|

|

|

|

||||

|

|

V REF –/ |

Ve REF |

– |

|

|

|

|

|

на 1,5 В или 2,5 В |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

INCHx |

|

|

|

|

A VCC |

|

Ref_x |

|

|

||

|

4 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Auto |

CONSEQx |

|

11 |

10 01 00 |

|

SREF1 |

|

|

|

|

|

|

A VSS |

|

SREF0 |

|

|

ADC10OSC |

|

|||||

|

|

|

|

|

|

|

|

|

|

|||

A0 |

0000 |

SREF2 |

1 |

0 |

|

ADC10ON |

|

|

|

ADC10SSELx |

|

|

A1 |

0001 |

|

|

|

|

|

|

ADC10DIVx |

|

|

|

|

A2 |

0010 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

A3 |

0011 |

Выборка |

V R – |

|

V R+ |

|

|

|

00 |

|

|

|

A4 |

0100 |

|

|

|

|

|

|

|||||

и |

|

|

|

|

|

Делитель |

01 |

ACLK |

|

|||

A5 |

0101 |

|

10•разрядный SAR |

|

|

|||||||

A6 |

0110 |

хранение |

|

/1 .. /8 |

10 |

MCLK |

|

|||||

|

|

|

|

|

|

|

||||||

A7 |

0111 |

S/H |

Convert |

|

|

|

|

|

11 |

SMCLK |

|

|

|

1000 |

|

|

|

ADC10CLK |

|

||||||

|

1001 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1010 |

|

|

|

|

|

|

ISSH |

|

SHSx |

|

|

|

1011 |

|

|

|

|

BUSY |

|

|

|

|

||

|

1100 |

|

|

|

|

|

|

|

|

|

ENC |

|

|

1101 |

|

|

|

|

|

|

|

|

|

00 |

ADC10SC |

|

1110 |

SAMPCON |

|

|

Таймер выборки |

SHI |

0 |

|

||||

|

|

|

|

01 |

TA1 |

|||||||

|

1111 |

|

|

|

|

/4/8/16/64 |

|

1 |

|

|||

|

|

|

|

|

|

|

|

Sync |

TA0 |

|||

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

A VCC |

|

ADC10DF |

ADC10SHTx |

MSC |

|

|

|

11 |

TA2 |

||

|

|

|

|

|

|

|

||||||

INCHx=0Bh |

|

|

|

|

|

|

ADC10MEM |

|

|

Ref_x |

|

|

|

|

R |

Контроллер |

n |

ОЗУ, флэш, периферия |

|

|

переноса |

|

||

|

|

|

|

|

|

данных |

|

|

|

R |

|

ADC10SA |

|

|

|

|

|

Останов |

|

|

|

|

|

|

|

|

|

|

ЦПУ |

A VSS |

ADC10CT |

ADC10TB |

ADC10B1 |

|

Рис. 18-1. Блок-схема АЦП10

18.2. Функционирование АЦП10

Модуль АЦП10 конфигурируется программным обеспечением пользователя. Настройка и работа АЦП10 рассматриваются в следующих далее разделах.

18.2.1. 10-разрядное ядро АЦП

Ядро АЦП преобразует аналоговый входной сигнал в 10-разрядное цифровое представление и сохраняет результат в регистре ADC10MEM. Ядро использует два программно выбираемых уровня напряжений (VR+ и VR-) для задания верхнего и нижнего пределов преобразования. Цифровой выход (NADC)

Библиотека Компэла |

|

333 |

|

MSP430x1xxFamily

составляет полную шкалу (03FFh), когда входной сигнал равен или выше VR+, и равен нулю, когда входной сигнал равен или ниже VR-. Входной канал и опорные уровни напряжений (VR+ и VR-) задаются в памяти управления преобразованиями. Результаты преобразования могут быть представлены в натуральном двоичном формате или формате с дополнением до двух. Формула преобразования для результата АЦП NADC с использованием натурального двоичного формата выглядит следующим образом:

NADC |

= 1023 |

Vin • VR` |

||

VR+ |

• VR` |

|||

|

|

|||

Ядро АЦП12 конфигурируется двумя управляющими регистрами: ADC10CTL0 и ADC10CTL1. Ядро включается битом ADC10ON. За некоторыми исключениями биты управления АЦП10 могут быть модифицированы только когда ENC=0. ENC должен быть установлен в 1 перед выполнением любого преобразования.

Выбор тактирования преобразования

ADC10CLK используется как для тактирования преобразования, так и для генерации периода выборки. Для выбора источника тактирования АЦП10 используются биты ADC10SSELx, а частота этого источника может быть поделена на 1-8 с помощью битов ADC10DIVx. Возможны следующие источники ADC10CLK: SMCLK, MCLK, ACLK и внутренний осциллятор ADC10OSC.

Внутренне генерируемая частота ADC10OSC лежит в диапазоне 5 МГц, на варьируется в зависимости от конкретного устройства, напряжения питания и температуры. См. справочное руководство конкретного устройства для уточнения значения ADC10OSC.

Пользователь должен гарантировать, что выбранный источник тактирования для ADC10CLK останется активным до конца преобразования. Если тактовые сигналы будут сняты во время преобразования, операция не будет завершена и любой результат будет неверным.

18.2.2. Входы АЦП10 и мультиплексор

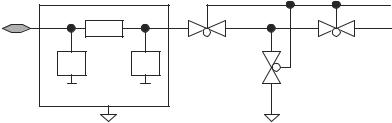

Восемь внешних и четыре внутренних аналоговых сигнала выбираются как канал для преобразования входным аналоговым мультиплексором. Входной мультиплексор имеет тип break-before-make (разрыв перед включением), что уменьшает инжекцию шумов от канала к каналу, возникающую при переключении каналов, как показано на рис. 18-2. Входной мультиплексор также является Т-переключателем, минимизирующим взаимосвязь между каналами. Невыбранные каналы изолированы от АЦП, а промежуточный узел подключен к аналоговой земле (AVSS), поэтому паразитная емкость заземляется, что помогает устранить перекрестные помехи.

334 |

|

Библиотека Компэла |

|

Раздел XVIII. |

АЦП10 |

R ~ 100 Oм |

INCHx |

Ax |

Вход |

|

|

Защита от электростатического |

|

разряда |

|

Рис. 18-2. Аналоговый мультиплексор

АЦП10 использует метод перераспределения заряда. Когда входы внутренне переключаются, переключение может привести к переходным процессам на входном сигнале. Эти переходные процессы затухают и устанавливаются до появления ошибочного преобразования.

Выбор аналогового порта

Внешние входы АЦП10 c A0 по А4, VeREF+ и VeREF- мультиплексированы с ножками порта Р2, являющимися цифровые КМОП ячейками. Опциональные входы с А5 по А7 являются у некоторых устройств общими с портом Р3 (см. справочные данные конкретного устройства). Когда аналоговые сигналы прикладываются к цифровым КМОП-схемам, может течь паразитный ток от VCC к GND. Этот паразитный ток появляется, когда величина входного напряжения находится около переходного уровня ячейки. Отключение буфера ножки порта устраняет протекание паразитного тока и вследствие этого уменьшает общий потребляемый ток. Биты ADC10AEx дают возможность отключать входные и выходные буфера ножек порта.

;P2.3 конфигурируется как аналоговый вход

BIS.B #4h,&ADC10AE |

;P2.3 включен как функция АЦП10 |

18.2.3. Генератор опорного напряжения

Модуль АЦП10 содержит встроенный генератор опорного напряжения с двумя выбираемыми уровнями напряжения: 1,5 В и 2,5 В. Любое из этих опорных напряжений может быть использовано внутренне или внешне на

выводе VREF+.

Внутренний опорный источник включается при установке REFON=1. Когда REF2_5V=1, внутреннее опорное напряжение равно 2,5 В, при REF2_5V=0 опорное напряжение равно 1,5 В.

Библиотека Компэла |

|

335 |

|

MSP430x1xxFamily

Внешние опорные источники могут быть задействованы для VR+ и VR- через выводы А4 и А3 соответственно.

Маломощные приложения

Внутренний генератор опорного напряжения АЦП10 разработан для маломощных приложений и имеет особые возможности для быстрого запуска. Для правильной работы не требуется внешнего накопительного конденсатора

исвязанного с ним времени смещения. Общее время включения опорного источника меньше 30 мкС. Для нормальной развязки источника питания требуется только комбинация параллельно включенных конденсаторов на 10 мкФ

и100 нФ.

•Когда VCC и VSS используются как опорные напряжения, внутренний опорный источник должен быть полностью выключен установкой REFON=0.

•Когда используется внешний опорный источник, внутренний источник должен быть полностью выключен. Внешние опорные источники могут быть задействованы для VR+ и VR- через выводы А4 и А3 соответственно.

•Когда используется внутренний источник и максимальная скорость преобразования ниже 50 ksps, установка ADC10SR=1 уменьшает потребление тока внутренним опорным буфером примерно на 50%.

•Когда оба бита REFOUT=1 и REFBURST=1, опорный источник представлен снаружи только во время периода выборки и преобразования. Когда REFOUT1=1, а REFBURST=0 очищен, опорное напряжение присутствует внешне постоянно.

18.2.4. Тактирование выборки и преобразования

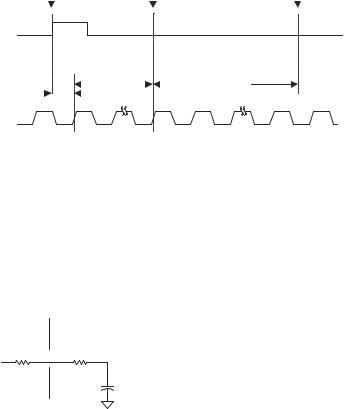

Аналого-цифровое преобразование инициируется по нарастающему фронту входного сигнала выборки SHI. Источник для SHI выбирается с помощью битов SHSx и может быть таким:

•Бит ADC10SC

•Модуль вывода 1 таймера А

•Модуль вывода 0 таймера А

•Модуль вывода 2 таймера А

Полярность источника сигнала SHI может быть инвертирована битом ISSH. Биты SHTx выбирают период выборки tsample равным 4, 8, 16 или 64 цикла ADC10CLK. Таймер выборки устанавливает SAMPCON в высокий уровень для выбранного периода выборки после синхронизации с ADC10CLK. Общее время

выборки составляет tsample плюс tsync. Переход SAMPCON с высокого уровня на низкий стартует аналого-цифровое преобразование, которому необходимо 13

циклов ADC10CLK, как показано на рис. 18-3.

336 |

|

Библиотека Компэла |

|

MSP430x1xxFamily

К примеру, если RS равно 10 кОм, tsample должно быть больше 2,63 мкс при ADC10SR = 0 или 4,33 мкс при ADC10SR = 1.

tsample |

( RS + 2 кОм ) |

7,625 |

20 |

пФ + 800 нс |

(ADC10SR = 0) |

tsample |

( RS + 2 кОм ) |

7,625 |

20 |

пФ + 2,5 мкс |

(ADC10SR = 1) |

18.2.5. Режимы преобразования

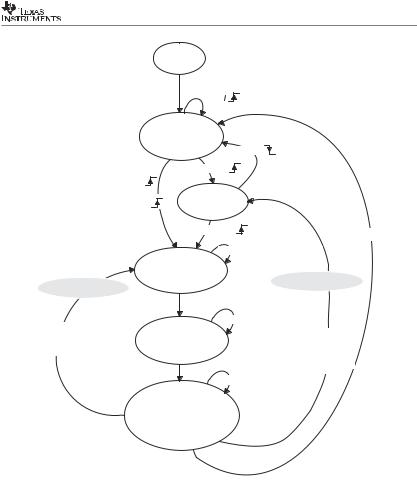

ADC10 имеет четыре режима работы, выбираемые битами CONSEQx так, как описано в таблице 18-1.

Таблица 18-1. Сводный перечень режимов преобразования

CONSEQx |

Режим |

Операция |

|

00 |

Одноканальный с одиночным |

Выполняется одно преобразование в одном |

|

преобразованием |

канале. |

||

|

|||

01 |

Последовательность каналов |

Выполняются однократные преобразования после- |

|

довательности каналов. |

|||

|

|

||

10 |

Повторяющийся одноканаль- |

Выполняется повторяющееся преобразование в |

|

ный |

одном канале. |

||

|

|||

11 |

Повторяющаяся последова- |

Выполняются повторяющиеся преобразования |

|

тельность каналов |

последовательности каналов. |

||

|

Одноканальный режим с одиночным преобразованием

В одном канале, выбранном INCHx, однократно выполняется выборка и преобразование. Результат АЦП записывается в регистр ADC10MEM. На рис. 18-5 показан процесс одноканального режима с одиночным преобразованием. Если преобразование запускается ADC10SC, поочередные преобразования могут быть запущены битом ADC10SC. Когда используется другой источник запуска, ENC должен переключаться между каждым преобразованием.

Режим последовательности каналов

Врежиме последовательности каналов однократно выполняется выборка

ипреобразование. Последовательность запускается с выбранного INCHx каналом и декрементируется к каналу А0. Каждый результат АЦП записывается в ADC10MEM. Последовательность останавливается после преобразования в канале А0. На рис. 18-6 показан режим последовательности каналов. Если последовательность запускается ADC10SC, поочередные преобразования могут запускаться битом ADC10SC. Когда используется любой другой источник запуска, ENC должен переключаться между каждой последовательностью.

Повторяющийся одноканальный режим

В одном канале, выбранном INCHx, непрерывно выполняются выборка и преобразование. Каждый результат АЦП записывается в ADC10MEM. На рис. 18- 7 показан повторяющийся одноканальный режим.

338 |

|

Библиотека Компэла |

|

Раздел XVIII. |

|

АЦП10 |

|

CONSEQx = 00 |

ADC10 |

|

|

выключен |

|

||

|

|

||

|

|

ENC = |

|

ADC10ON = 1 |

|

|

|

|

x = INCHx |

|

|

|

ожидание |

|

|

SHS = 0 |

включения |

ENC = |

|

|

ENC = |

||

и |

|

||

ENC = 1 или |

|

|

|

и |

Ожидание |

||

ADC10SC = |

|||

запуска |

|||

|

|||

ENC = 0 |

SAMPCON = |

||

|

(4/8/16/64) x ADC10CLK |

||

|

|

||

Выборка, входной канал

ENC = 0*

12 x ADC10CLK

Преобразование

ENC = 0*

1 x ADC10CLK

Преобразование

завершено, результат в ADC10MEM,

ADC10IFG установлен

x = входной канал Ax

* Результат преобразования непредсказуем

Рис. 18-5. Одноканальный режим одиночного преобразования

Режим повторяющейся последовательности каналов

Непрерывно выполняются выборка и преобразование последовательности каналов. Последовательность начинается с канала, выбранного INCHx и декрементируется к каналу А0. Каждый результат АЦП записывается в ADC10MEM. Последовательность останавливается после преобразования в канале А0, а следующий сигнал запуска стартует последовательность снова. На рис. 18-8 показан режим повторяющейся последовательности каналов.

Библиотека Компэла |

|

339 |

|

MSP430x1xxFamily

|

CONSEQx = 01 |

|

ADC10 |

|

|

|

|

выключен |

|

||

|

|

|

|

|

|

|

ADC10ON = 1 |

|

|||

|

|

|

|

ENC = |

|

|

|

|

|

x = INCHx |

|

|

|

ожидание включения |

|

||

|

SHS = 0 |

|

|

ENC = |

|

|

|

|

ENC = |

|

|

|

и |

|

|

|

|

|

|

|

|

|

|

|

ENC = 1 или |

|

|

|

|

|

и |

|

|

Ожидание |

|

|

ADC10SC = |

|

|||

|

запуска |

|

|||

|

|

|

|

|

|

|

|

|

|

SAMPCON = |

x = 0 |

|

|

|

|

|

|

|

|

|

|

(4/8/16/64) x ADC10CLK |

|

|

|

|

|

Выборка, |

|

|

|

|

входной канал Ax |

если x > 0 то x = x • 1 |

|

если x > 0 то x = x • 1 |

|

|

|

||

|

|

|

|

||

MSC = 1 |

|

|

12 x ADC10CLK |

|

|

|

|

|

|

||

и |

0 |

|

|

Преобразование |

MSC = 0 |

x |

|

|

|

и |

|

|

|

|

|

|

|

|

|

|

|

|

x 0 |

|

|

|

|

1 x ADC10CLK |

|

|

|

|

|

Преобразование |

|

|

|

завершено, результат |

|

||

|

|

|

|

в ADC10MEM, |

|

|

|

ADC10IFG установлен |

|

||

x = входной канал Ax

Рис. 18-6. Режим последовательности каналов

Использование бита MSC

Для конфигурирования преобразователя на выполнение автоматических поочередных преобразований с максимальной быстротой можно воспользоваться функцией множественных выборок и преобразований. Если MSC=1 и CONSEQx>1, первый фронт сигнала SHI запустит первое преобразование. Поочередные преобразования запускаются автоматически после завершения предыдущего преобразования. Дополнительные фронты на SHI игнорируются, пока последовательность не закончена в режиме одиночной последовательнос-

340 |

|

Библиотека Компэла |

|