Семейство микроконтроллеров MSP430X1XX, руководство пользователя (2004)

.pdfРаздел XIV. |

|

|

Периферийный интерфейс USART, режим SPI |

|

|

|

|

|

|

Включение синхронного режима |

|

SYNC |

Бит 2 |

0 – Режим UART |

|

|

|

1 |

– Режим SPI |

|

|

Режим ведущего |

|

MM |

Бит 1 |

0 – USART ведомый |

|

|

|

1 |

– USART ведущий |

|

|

Включение программного сброса |

|

SWRST |

Бит 0 |

0 |

– Отключен. Сброс USART исключен из работы |

|

|

1 |

– Разрешен. Логика USART удерживается в состоянии сброса |

*Применимо к USART0 только в устройствах MSP430x15x и MSP430x16x.

UxTCTL, регистр управления передачей USART

7 |

|

6 |

|

|

5 |

|

4 |

3 |

|

2 |

|

1 |

|

0 |

|

||

|

CKPH |

|

CKPL |

|

|

|

SSELx |

|

Не |

|

Не |

|

STC |

|

TXEPT |

|

|

|

|

|

|

|

|

используется |

используется |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

rw•0 |

rw•0 |

rw•0 |

rw•0 |

rw•0 |

rw•0 |

rw•0 |

rw•1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

Выбор фазы тактирования. Управляет фазой UCLK. |

|

|

||||||||

|

CKPH |

Бит 7 |

|

0 |

– Обычная схема тактирования UCLK |

|

|

|

|

||||||||

|

|

|

|

|

|

|

1 |

– Сигнал UCLK отстает на один полупериод |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Выбор полярности тактового сигнала. |

|

|

|

|

||||||

|

|

|

|

|

|

|

0 |

– Неактивный уровень низкий; вывод данных происходит по |

|||||||||

|

|

|

|

|

|

|

нарастающему фронту UCLK; входные данные защелкиваются по |

||||||||||

|

CKPL |

Бит 6 |

|

спаду UCLK. |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

1 |

– Неактивный уровень высокий; вывод данных происходит по |

|||||||||

|

|

|

|

|

|

|

спаду UCLK; входные данные защелкиваются по нарастающему |

||||||||||

|

|

|

|

|

|

|

фронту UCLK. |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

Выбор источника. Эти биты выбирают источник тактирования для |

||||||||||

|

|

|

|

|

|

|

BRCLK |

|

|

|

|

|

|

|

|

|

|

|

SSELx |

Биты 5-4 |

|

00 – Внешний UCLK (действует только в режиме ведомого) |

|||||||||||||

|

|

01 – ACLK (справедливо только для режима ведущего) |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

10 – SMCLK (справедливо только для режима ведущего) |

|

|

||||||||

|

|

|

|

|

|

|

11 – SMCLK (справедливо только для режима ведущего) |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Не |

Бит 3 |

|

Не используется |

|

|

|

|

|

|

|

|

|||||

используется |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Не |

Бит 2 |

|

Не используется |

|

|

|

|

|

|

|

|

|||||

используется |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

Управление передачей ведомого. |

|

|

|

|

|

|

||||

|

STC |

Бит 1 |

|

0 |

– 4-х выводной режим SPI: STE включен |

|

|

|

|

||||||||

|

|

|

|

|

|

|

1 |

– 3-х выводной режим SPI: STE выключен |

|

|

|

|

|||||

|

|

|

|

|

|

|

Флаг опустошения передатчика. Флаг TXEPT не используется в |

||||||||||

|

TXEPT |

Бит 0 |

|

режиме ведомого. |

|

|

|

|

|

|

|

|

|||||

|

|

0 |

– Передача активна и/или в UxTXBUF находятся данные |

||||||||||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

1 |

– UxTXBUF и сдвиговый регистр TX пусты |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Библиотека Компэла |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

261 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

MSP430x1xxFamily

UxRCTL, регистр управления приемом USART

7 |

|

6 |

|

5 |

4 |

3 |

2 |

1 |

0 |

|

||

|

FE |

|

Не |

|

OE |

Не |

Не |

Не |

Не |

Не |

|

|

|

используется |

|

используется |

используется |

используется |

используется |

используется |

|

||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw•0 |

|

rw•0 |

rw•0 |

rw•0 |

rw•0 |

rw•0 |

rw•0 |

rw•0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Флаг ошибки фрэйма. Этот бит указывает на конфликт шины, |

||||||

|

|

|

|

|

|

когда MM=1 и STC=0. FE не используется в режиме ведомого. |

||||||

|

FE |

|

Бит 7 |

|

0 – Конфликт не обнаружен |

|

|

|

|

|||

|

|

|

|

|

|

1 – На STC появился отрицательный фронт, указывая на конфликт |

||||||

|

|

|

|

|

|

при обращении к шине |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Не |

|

Бит 6 |

|

Не используется |

|

|

|

|

|

||

|

используется |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Флаг ошибки переполнения. Этот бит устанавливается, когда сим- |

||||||

|

|

|

|

|

|

вол перемещен в UxRXBUF до завершения чтения предыдущего |

||||||

|

OE |

|

Бит 5 |

|

символа. OE автоматически сбрасывается, когда UxRXBUF прочи- |

|||||||

|

|

|

тан, когда SWRST=1, а также может быть сброшен программно. |

|||||||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

0 – Нет ошибки |

|

|

|

|

|

|

|

|

|

|

|

|

1 – Произошла ошибка переполнения |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Не |

|

Бит 4 |

|

Не используется |

|

|

|

|

|

||

|

используется |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Не |

|

Бит 3 |

|

Не используется |

|

|

|

|

|

||

|

используется |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Не |

|

Бит 2 |

|

Не используется |

|

|

|

|

|

||

|

используется |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Не |

|

Бит 1 |

|

Не используется |

|

|

|

|

|

||

|

используется |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Не |

|

Бит 0 |

|

Не используется |

|

|

|

|

|

||

|

используется |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

UxBR0, регистр 0 управления скоростью передачи USART

7 |

6 |

5 |

4 |

3 |

2 |

|

1 |

0 |

|

|

||||||||

|

27 |

|

26 |

25 |

24 |

23 |

22 |

|

21 |

20 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw |

|

rw |

|

rw |

|

rw |

|

rw |

|

rw |

rw |

|

rw |

|||

UxBR1, регистр 1 управления скоростью передачи USART |

|

|

|

|

|

|||||||||||||

7 |

6 |

5 |

4 |

|

2 |

|

1 |

0 |

|

|

||||||||

|

3 |

|

|

|

||||||||||||||

|

|

215 |

|

214 |

|

213 |

|

212 |

|

211 |

|

210 |

|

29 |

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw |

|

rw |

|

rw |

|

rw |

|

rw |

|

rw |

rw |

|

rw |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Библиотека Компэла |

||||

262 |

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||

Раздел XIV. |

Периферийный интерфейс USART, режим SPI |

Генератор скорости передачи использует содержимое UxBRx {UxBR1+UxBR0} для установки скорости передачи. Возможна

некорректная работа SPI в случае установки UxBR < 2.

UxMCTL, регистр управления модуляцией USART

7 |

|

6 |

|

5 |

4 |

3 |

|

2 |

1 |

0 |

|

||

|

m7 |

|

m6 |

|

m5 |

m4 |

m3 |

|

m2 |

m1 |

m0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw |

rw |

rw |

rw |

rw |

rw |

rw |

rw |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UxMCTLx |

Биты 7-0 |

|

Регистр управления модуляцией не используется в режиме SPI и |

|||||||||

|

|

должен быть установлен на 000h. |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UxRXBUF, регистр буфера приема USART

7 |

|

6 |

5 |

|

4 |

|

3 |

|

2 |

1 |

0 |

|

|

|

27 |

|

26 |

25 |

|

24 |

|

23 |

|

22 |

21 |

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

r |

r |

r |

r |

r |

r |

r |

r |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буфер принятых данных доступен пользовате- |

|||||

|

|

|

|

|

|

|

|

лю и содержит последний принятый из сдвиго- |

|||||

|

|

|

|

|

|

|

|

вого регистра приема символ. Чтение UxRXBUF |

|||||

|

UxRXBUFx |

|

Биты 7-0 |

|

|

сбрасывает бит OE и флаг URXIFGx. В режиме |

|||||||

|

|

|

|

|

|

|

|

7-разрядных данных, UxRXBUF выравнивается |

|||||

|

|

|

|

|

|

|

|

по младшему разряду, а старший разряд всегда |

|||||

|

|

|

|

|

|

|

|

сбрасывается. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UxTXBUF, регистр буфера передачи USART

7 |

|

6 |

5 |

|

4 |

3 |

2 |

1 |

0 |

|

|

|

27 |

|

26 |

25 |

|

24 |

23 |

22 |

21 |

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw |

rw |

rw |

rw |

rw |

rw |

rw |

rw |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буфер передаваемых данных доступен поль- |

||||

|

|

|

|

|

|

|

зователю и содержит текущие передаваемые |

||||

|

|

|

|

|

|

|

данные. Когда используется длина символа в 7 |

||||

|

UxTXBUFx |

|

Биты 7-0 |

|

бит, данные необходимо выровнять по старше- |

||||||

|

|

|

|

|

|

|

му разряду перед перемещением их в UxTXBUF. |

||||

|

|

|

|

|

|

|

Данные передаются начиная со старшего разря- |

||||

|

|

|

|

|

|

|

да. Запись в UxTXBUF очищает UTXIFGx. |

||||

|

|

|

|

|

|

|

|

|

|

|

|

Библиотека Компэла |

|

263 |

|

MSP430x1xxFamily

ME1, регистр 1 включения модуля

7 |

6 |

|

5 |

|

4 |

|

3 |

2 |

1 |

|

0 |

|

|||

|

|

USPIE0* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw•0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Бит 7 |

|

Этот бит может быть использован другими модулями. См. спра- |

||||||||||

|

|

|

|

вочные данные конкретного устройства. |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

Включение USART0 SPI. Этот бит включает режим SPI для |

|

|

|||||||

|

USPIE0* |

|

Бит 6 |

|

USART0. |

|

|

|

|

|

|

|

|

||

|

|

|

0 – Модуль выключен |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 – Модуль включен |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Биты 5-0 |

|

Эти биты могут быть использованы другими модулями. См. спра- |

||||||||||

|

|

|

|

вочные данные конкретного устройства. |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||||

* Не используется в устройствах MSP430x12xx. См. ME2 для битов включения модуля USART0 MSP430x12xx.

ME2, регистр 2 включения модуля

7 |

|

6 |

|

5 |

|

4 |

|

3 |

2 |

1 |

0 |

|

||

|

|

|

|

|

|

|

USPIE1 |

|

|

|

|

USPIE0** |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw•0 |

|

|

|

rw•0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Биты 7-5 |

|

Эти биты могут использоваться другими модулями. См. справоч- |

|||||||||

|

|

|

|

ные данные конкретного устройства. |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Включение USART1 SPI. Этот бит включает режим SPI для |

||||||||

|

USPIE1 |

Бит 4 |

|

USART1. |

|

|

|

|

|

|

|

|||

|

|

0 – Модуль выключен |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 – Модуль включен |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Биты 3-1 |

|

Эти биты могут использоваться другими модулями. См. справоч- |

|||||||||

|

|

|

|

ные данные конкретного устройства. |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Включение USART0 SPI. Этот бит включает режим SPI для |

||||||||

|

USPIE0** |

Бит 0 |

|

USART0. |

|

|

|

|

|

|

|

|||

|

|

0 – Модуль выключен |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 – Модуль включен |

|

|

|

|

|

|||

** Только устройства MSP430x12xx |

|

|

|

|

|

|

|

|||||||

IE1, регистр 1 разрешения прерываний

7 |

|

6 |

5 |

4 |

3 |

2 |

|

1 |

0 |

|

|

|

UTXIE0* |

URXIE0* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw•0 |

rw•0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Библиотека Компэла |

||

264 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||||

Раздел XIV. |

|

|

Периферийный интерфейс USART, режим SPI |

|

|

|

|

||

|

|

Разрешение прерывания при передаче USART0. Этот бит разреша- |

||

UTXIE0* |

Бит 7 |

ет прерывание UTXIFG0. |

||

0 |

– Прерывание не разрешено |

|||

|

|

|||

|

|

1 |

– Прерывание разрешено |

|

|

|

|

||

|

|

Разрешение прерывания при приеме USART0. Этот бит разрешает |

||

URXIE0* |

Бит 6 |

прерывание URXIFG0. |

||

0 |

– Прерывание не разрешено |

|||

|

|

|||

|

|

1 |

– Прерывание разрешено |

|

|

|

|

||

|

Биты 5-0 |

Эти биты могут быть использованы другими модулями. См. спра- |

||

|

вочные данные конкретного устройства. |

|||

|

|

|||

|

|

|

||

* Не используется в устройствах MSP430x12xx. См. IE2 для битов разрешения прерывания |

||||

USART0 MSP430x12xx. |

|

|

||

IE2, регистр 2 разрешения прерывания

7 |

|

6 |

|

5 |

|

4 |

|

3 |

|

2 |

1 |

0 |

|

||

|

|

|

|

UTXIE1 |

URXIE1 |

|

|

|

|

UTXIE0** |

URXIE0** |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

rw•0 |

rw•0 |

|

|

|

rw•0 |

rw•0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Биты 7-6 |

|

Эти биты могут использоваться другими модулями. См. справоч- |

||||||||||

|

|

|

|

ные данные конкретного устройства. |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Разрешение прерывания при передаче USART1. Этот бит разреша- |

|||||||||

|

UTXIE1 |

Бит 5 |

|

ет прерывание UTXIFG1. |

|

|

|

|

|||||||

|

|

0 |

– Прерывание не разрешено |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

1 |

– Прерывание разрешено |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Разрешение прерывания при приеме USART1. Этот бит разрешает |

|||||||||

|

URXIE1 |

Бит 4 |

|

прерывание URXIFG1. |

|

|

|

|

|

|

|||||

|

|

0 |

– Прерывание не разрешено |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

1 |

– Прерывание разрешено |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Биты 3-2 |

|

Эти биты могут использоваться другими модулями. См. справоч- |

||||||||||

|

|

|

|

ные данные конкретного устройства. |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Разрешение прерывания при передаче USART0. Этот бит разреша- |

|||||||||

|

UTXIE0** |

Бит 1 |

|

ет прерывание UTXIFG0. |

|

|

|

|

|||||||

|

|

0 |

– Прерывание не разрешено |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

1 |

– Прерывание разрешено |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Разрешение прерывания при приеме USART0. Этот бит разрешает |

|||||||||

|

URXIE0** |

Бит 0 |

|

прерывание URXIFG0. |

|

|

|

|

|

|

|||||

|

|

0 |

– Прерывание не разрешено |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

1 |

– Прерывание разрешено |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

** Только устройства MSP430x12xx |

|

|

|

|

|

|

|

|

|||||||

Библиотека Компэла |

|

265 |

|

MSP430x1xxFamily

IFG1, регистр 1 флагов прерываний

7 |

6 |

|

5 |

4 |

3 |

|

2 |

1 |

0 |

|

||||

|

UTXIFG0* |

URXIFG0* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw•1 |

|

rw•0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Флаг прерывания при передаче USART0. UTXIFG0 устанавливает- |

||||||||

|

UTXIFG0* |

|

Бит 7 |

|

ся, когда U0TXBUF пуст. |

|

|

|

|

|||||

|

|

|

0 |

– Прерывание не ожидается |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

1 |

– Прерывание ожидается |

|

|

|

|

|||

|

|

|

|

|

|

Флаг прерывания при приеме USART0. URXIFG0 устанавливается, |

||||||||

|

URXIFG0* |

|

Бит 6 |

|

когда в U0RXBUF принят полный символ. |

|

|

|

||||||

|

|

|

0 |

– Прерывание не ожидается |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

1 |

– Прерывание ожидается |

|

|

|

|

|||

|

|

|

Биты 5-0 |

|

Эти биты могут быть использованы другими модулями. См. спра- |

|||||||||

|

|

|

|

вочные данные конкретного устройства. |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||||||

* Не используется в устройствах MSP430x12xx. См. IFG2 для битов флагов прерывания USART0 MSP430x12xx.

IFG2, регистр 2 флагов прерываний

7 |

|

|

6 |

5 |

|

4 |

3 |

|

2 |

1 |

0 |

|

|||

|

|

|

|

|

|

UTXIFG1 |

|

URXIFG1 |

|

|

|

UTXIFG0** |

URXIFG0** |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw•1 |

|

rw•0 |

|

|

|

|

rw•1 |

rw•0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Биты 7-6 |

Эти биты могут использоваться другими модулями. См. спра- |

|||||||||

|

|

|

|

|

вочные данные конкретного устройства. |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

Флаг прерывания при передаче USART1. UTXIFG1 устанавли- |

||||||||

|

UTXIFG1 |

|

|

Бит 5 |

вается, когда U1TXBUF пуст. |

|

|

|

|

|

|||||

|

|

|

0 |

– Прерывание не ожидается |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

1 |

– Прерывание ожидается |

|

|

|

|

|

||

|

|

|

|

|

|

|

Флаг прерывания при приеме USART1. URXIFG1 устанавлива- |

||||||||

|

URXIFG1 |

|

|

Бит 4 |

ется, когда в U1RXBUF принят полный символ. |

|

|

||||||||

|

|

|

0 |

– Прерывание не ожидается |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

1 |

– Прерывание ожидается |

|

|

|

|

|

||

|

|

|

|

|

Биты 3-2 |

Эти биты могут использоваться другими модулями. См. спра- |

|||||||||

|

|

|

|

|

вочные данные конкретного устройства. |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

Флаг прерывания при передаче USART0. UTXIFG0 устанавли- |

||||||||

|

UTXIFG0** |

|

|

Бит 1 |

вается, когда U0TXBUF пуст. |

|

|

|

|

|

|||||

|

|

|

0 |

– Прерывание не ожидается |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

1 |

– Прерывание ожидается |

|

|

|

|

|

||

|

|

|

|

|

|

|

Флаг прерывания при приеме USART0. URXIFG0 устанавлива- |

||||||||

|

URXIFG0** |

|

|

Бит 0 |

ется, когда в U0RXBUF принят полный символ. |

|

|

||||||||

|

|

|

0 |

– Прерывание не ожидается |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

1 |

– Прерывание ожидается |

|

|

|

|

|

||

** Только устройства MSP430x12xx |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Библиотека Компэла |

||

266 |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

MSP430x1xxFamily

Периферийный интерфейс USART, режим I2C

Универсальный синхронно/асинхронный приемопередающий (USART) периферийный интерфейс поддерживает связь по I2C в модулях USART0. Этот раздел описывает режим I2C. Режим I2C реализован в устройствах MSP430x15x и MSP430x16x.

15.1. Введение в модуль I2C

Модуль управления взаимообменом между интегральными схемами (I2C) обеспечивает интерфейс между MSP430 и I2C-совместимыми устройствами через последовательную двухпроводную шину I2C. Внешние компоненты, присоединенные к шине I2C последовательно передают и/или принимают последовательные данные в/из USART через 2-х проводной I2C-интерфейс.

Модуль I2C имеет следующие возможности:

–Соответствует спецификации I2C v2.1 Philips Semiconductor

• Формат передачи байт/слово

• 7-разрядный и 10-разрядный режимы адресации устройств

• Общий вызов

• Старт/рестарт/стоп

• Режим приемника передатчик/ведущий со многими ведущими

• Режим передатчика приемник/ведомый со многими ведущими

• Комбинированный режим ведущего передача/прием и прием/передача

• Поддержка стандартного режима до 100 кбод и быстрого режима до 400 кбод

–Встроенный FIFO для буферирования чтения и записи

–Программируемая генерация тактовых импульсов

–16-разрядный доступ к данным для увеличения пропускной способности шины

–Автоматический подсчет количества байт данных

–Разработан для работы при пониженном энергопотреблении

–Определение условия СТАРТ ведомого приемника для автоматического выхода из режимов LPMx

–Расширенные возможности прерываний

–Реализован только в USART0

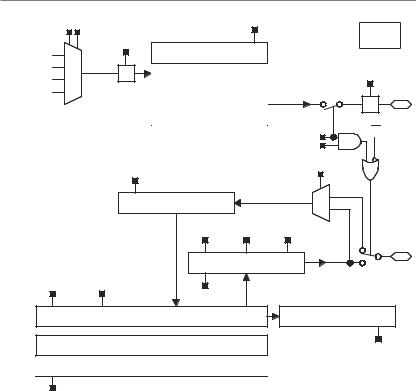

На рис. 15-1 показана блок-схема модуля I2С.

15.2. Функционирование модуля I2C

Модуль I2С поддерживает любые ведущие или ведомые устройства, совместимые с I2С. На рис. 15-2 показан пример шины I2С. Каждое устройство I2С

268 |

|

Библиотека Компэла |

|

Раздел XV. |

|

Периферийный интерфейс USART, режим I2C |

||||

I2CSSELx |

|

I2CEN |

|

|

|

|

|

|

|

SYNC = 1 |

|

||

|

|

|

|

|

|

|

|

|

I2CBUSY |

|

|

I2C = 1 |

|

Нет |

00 |

Тактовый генератор I2C |

|

|

|

|

тактирования |

|

|

|

|

|

|

|

|

|

|

|

|

|

ACLK |

01 |

I2CIN |

|

|

|

|

SMCLK |

10 |

I2CPSC |

|

|

I2CSCLLOW |

|

|

|

|

|

|

||

SMCLK |

11 |

I2CSCLL |

|

I2CCLK |

1 |

SCL |

|

|

|

|

|

||

|

|

I2CSCLH |

|

|

|

|

|

|

|

|

|

R/W |

|

|

|

|

|

|

MST |

|

|

|

|

|

I2CTRX |

|

|

|

|

I2CRXOVR |

|

|

LISTEN |

|

|

|

|

|

|

|

|

|

|

Сдвиговый регистр приема |

|

|

0 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

I2CSTP |

I2CSTT |

I2CSTB |

|

|

|

|

|

|

|

0 |

SDA |

|

|

Сдвиговый регистр передачи |

1 |

|

||

|

|

|

|

|

|

|

I2CWORD |

|

I2CSBD |

|

|

|

|

|

|

I2CTXUDF |

|

|

|

|

|

|

I2CDRW |

|

|

I2CNDATx |

|

|

|

I2COA |

|

|

I2CRM |

|

|

|

I2CSA |

|

|

|

|

XA

Рис. 15-1. Блок-схема USART: режим I2C

обладает уникальным адресом и может работать и как передатчик и как приемник. Устройство, подключенное к шине I2С, во время передачи данных может рассматриваться как ведущее или ведомое. Ведущий инициирует передачу данных и генерирует тактовый сигнал SCL. Любое устройство, адресованное ведущим, рассматривается как ведомый.

При обмене данными на I2С используется вывод последовательных данных (SDA) и вывод последовательного тактирования (SCK). Оба вывода SDA и SCL являются двунаправленными и должны подключаться к положительному источнику питания с использованием нагрузочного резистора.

Примечание: Уровни SDA и SCL

Уровни напряжения на выводах SDA и SCL не должны быть выше уровня VCC MSP430.

Библиотека Компэла |

|

269 |

|

MSP430x1xxFamily

VCC

VCC |

Устройство |

MSP430 |

A |

|

Последовательные данные (SDA)

Последовательное тактирование (SCL)

Устройство |

Устройство |

B |

С |

Рис. 15-2. Схема подключений на шине I2C

15.2.1. Инициализация модуля I2C

Модуль I2C является частью периферии USART. Индивидуальный бит устанавливает, когда USART0 используется в режиме I2C, а не в режимах SPI или UART. Значение по умолчанию в регистре U0CTL устанавливает режим UART. Для работы с I2C необходимо установить биты SYNC и I2C. После инициализации модуля, модуль I2C готов для выполнения приема или передачи. Установка I2CEN разрешает работу модуля I2C.

Конфигурирование и переконфигурирование модуля I2C всегда должно выполняться только при I2CEN=0, во избежание непредсказуемого поведения. Установка I2CEN=0 вызывает следующие эффекты:

•связь по I2C останавливается;

•линии SDA и SCL переводятся в высокоимпедансное состояние;

•в регистре I2CTCTL очищаются биты 3-0, а биты 7-4 не изменяются;

•очищаются регистры I2CDCTL и I2CDR;

•сдвиговые регистры приема и передачи очищаются;

•регистры U0CTL, I2CNDAT, I2CPSC, I2CSCLL, I2CSCLH не изменяются;

•регистры I2COA, I2CSA, I2CIE, I2CIFG и I2CIV не изменяются.

Когда USART переконфигурируется из режима I2C в режимы UART или SPI, первыми должны быть очищены биты I2C, SYNC и I2CEN, затем должен быть установлен SWRST и только потом можно начать процедуру инициализации UART или SPI. Нарушение этой последовательности может привести к непредсказуемым результатам.

Примечание: конфигурирование модуля USART для работы в режиме I2C после сброса:

270 |

|

Библиотека Компэла |

|