Семейство микроконтроллеров MSP430X1XX, руководство пользователя (2004)

.pdfРаздел V. |

|

|

|

Контроллер флэш-памяти |

||

|

|

|

|

|||

|

|

|

Пароль FCTLx. Всегда читается как 096h. Должен записывать- |

|||

FWKEY |

Биты 15-8 |

ся как 0A5h, в противном случае будет генерироваться сигнал |

||||

|

|

|

PUC. |

|||

|

|

|

||||

Зарезервировано |

Биты 7-6 |

Зарезервировано. Всегда читается как 0. |

||||

|

|

|

|

|||

|

|

|

Аварийный выход |

|||

EMEX |

Бит 5 |

0 – Нет аварийного выхода |

||||

|

|

|

1 |

– Аварийный выход |

||

|

|

|

|

|||

|

|

|

Блокировка. Этот бит разблокирует флэш-память для выпол- |

|||

|

|

|

нения записи или стирания. Бит LOCK может быть установлен |

|||

|

|

|

в любой момент во время записи байта/слова или операции |

|||

|

|

|

стирания, при этом выполняемая операция будет нормально |

|||

LOCK |

Бит 4 |

завершена. В режиме блочной записи, если бит LOCK уста- |

||||

|

|

|

навливается, когда BLKWRT=WAIT=1, биты BLKWRT и WAIT |

|||

|

|

|

сбрасываются и режим нормально заканчивается. |

|||

|

|

|

0 |

– Разблокировано |

||

|

|

|

1 |

– Заблокировано |

||

|

|

|

|

|||

|

|

|

Ожидание. Указывает, что происходит запись флэш-памяти. |

|||

WAIT |

Бит 3 |

0 |

– Флэш-память не готова для записи следующего байта/сло- |

|||

ва. |

||||||

|

|

|

||||

|

|

|

1 |

– Флэш-память готова для записи следующего байта/слова. |

||

|

|

|

|

|||

|

|

|

Флаг прерывания при нарушении прав доступа |

|||

ACCVIFG |

Бит 2 |

0 – Прерывание не ожидается |

||||

|

|

|

1 |

– Ожидание прерывание |

||

|

|

|

|

|||

|

|

|

Ключ нарушения безопасности флэш. Этот бит показывает, |

|||

|

|

|

что был записан неправильный пароль FCTLx в любой регистр |

|||

KEYV |

Бит 1 |

управления флэш-памятью и при его установке генерируется |

||||

сигнал PUC. Бит KEYV должен быть сброшен программно. |

||||||

|

|

|

||||

|

|

|

0 |

– Был записан корректный пароль FCTLx |

||

|

|

|

1 |

– Был записан некорректный пароль FCTLx |

||

|

|

|

|

|||

|

|

|

Занято. Этот бит показывает состояние тактового генератора |

|||

BUSY |

Бит 0 |

флэш. |

||||

0 |

– Не занят |

|||||

|

|

|

||||

|

|

|

1 |

– Занят |

||

|

|

|

|

|

|

|

Библиотека Компэла |

|

|

|

|

||

|

|

|

131 |

|||

|

|

|

||||

MSP430x1xxFamily

IE1, регистр 1 разрешения прерывания

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

ACCVIE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rw–0 |

|

|

|

|

|

|

Биты 7-6, |

Эти биты могут быть использованы для других модулей. См. |

|

|

4-0 |

справочной руководство конкретного устройства. |

|

|

|

|

|

|

|

Разрешение прерывания при нарушении доступа к флэш-па- |

|

|

|

мяти. Этот бит разрешает прерывание от ACCVIFG. Поскольку |

|

|

|

остальные биты в IE1 могут быть использованы для других |

|

ACCVIE |

Бит 5 |

модулей, рекомендуется устанавливать и очищать этот бит с |

|

помощью команд BIS.B или BIC.B, вместо команд MOV.B |

|||

|

|

||

|

|

или CLR.B. |

|

|

|

0 – Прерывание запрещено |

|

|

|

1 – Прерывание разрешено |

|

|

|

|

132 |

|

Библиотека Компэла |

|

Супервизор напряжения питания

Раздел VI.

MSP430x1xxFamily

MSP430x1xxFamily

Супервизор напряжения питания

В этом разделе описывается работа супервизора напряжения питания (SVS1). Модуль SVS реализован в устройствах MSP430x15x и MSP430x16x.

6.1. Введение в SVS

Супервизор напряжения питания (SVS) используется для мониторинга напряжения питания AVCC или внешнего напряжения. SVS может быть сконфигурирован так, чтобы выполнялась установка флага или генерировался сигнал сброса POR, когда напряжение питания или внешнее напряжение снижаются ниже порога, установленного пользователем.

SVS обладает следующими возможностями:

•Мониторинг AVCC;

•Возможность генерации сигнала POR;

•Программно доступный вывод компаратора SVS;

•Программно доступное условие фиксации при низком напряжении;

•Выбор из 14 возможных пороговых уровней;

•Внешний канал мониторинга внешнего напряжения.

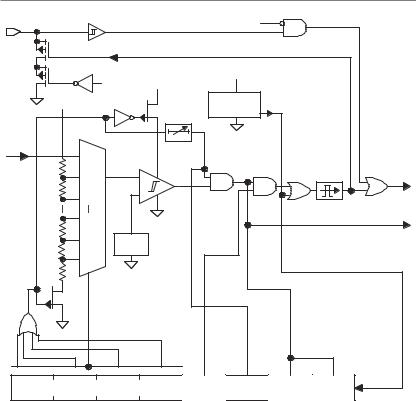

Блок-схема SVS показана на рис. 6.1.

6.2. Функционирование SVS

SVS определяет снижение напряжения AVCC ниже заданного уровня. Модуль SVS можно сконфигурировать на выработку сигнала POR или установку флага при снижении напряжения. После сигнала BOR модуль SVS отключается, чтобы сохранить потребление тока.

6.2.1. Конфигурирование SVS

Биты VLDx используются для включения/выключения SVS и выбора одного из 14 пороговых уровней (V(SYS_IT-)) для сравнения с AVCC. SVS выключен, когда VLDx=0 и включен, когда VLDx>0. Бит SVSON не включает SVS. Он показывает включенное/выключенное состояние модуля SVS и может использоваться для определения, включен ли SVS.

При VLDx=1111 выбирается внешний канал SVSin. Напряжение на SVSin сравнивается с внутренним уровнем напряжения, равным приблизительно 1,2 В.

6.2.2. Функционирование компаратора SVS

Состояние пониженного напряжения появляется, когда AVCC понижается меньше выбранного порога или когда внешнее напряжение снижается ниже

1 SVS – Supply Voltage Supervisor.

134 |

|

Библиотека Компэла |

|

Раздел VI. |

|

|

|

|

|

Супервизор напряжения питания |

||

|

|

|

|

|

NMI |

|

|

|

D |

|

Tau ~ 50 нс |

|

|

|

|

|

|

U |

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

VCC |

|

|

|

U |

G |

|

|

|

|

|

|

|

TCK |

|

VCC |

|

|

|

|

||

S |

|

|

|

|

|

|||

|

|

|

|

|

|

|||

|

VCC |

|

|

D |

Сброс при |

|

|

|

|

|

|

понижении |

|

|

|

||

|

|

|

G |

S |

напряжения |

|

|

|

P6.7/A7 |

|

|

|

~ 50us |

|

|

|

|

|

|

1111 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Установка |

|

|

1101 |

– |

|

|

|

|

POR |

|

|

1100 |

+ |

|

|

|

|

|

|

|

|

|

|

|

tсброса ~ 50 нс |

|

|

|

|

0011 |

|

|

|

|

Выход SVS |

|

|

|

|

|

|

|

|

|

|

|

|

0010 |

1.25V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0001 |

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

G |

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Установка SVSFG |

|

|

|

|

|

|

|

|

|

Сброс |

|

|

VLD |

|

PORON |

SVSON |

SVSOP |

SVSFG |

|

Биты SVSCTL

Рис. 6-1. Блок схема модуля SVS

порога в 1,2 В. Любое состояние пониженного напряжения устанавливает бит SVSFG.

Бит PORON включает или выключает функцию сброса устройства от SVS. Если PORON=1, при установке бита SVSFG генерируется сигнал POR. Если PORON=0, состояние пониженного напряжения устанавливает SVSFG, но не приводит к генерации сигнала POR.

Бит SVSFG при установке фиксируется. Благодаря этому пользователь может определить, что ранее произошло понижение напряжения. Бит SVSFG должен сбрасываться программным обеспечением пользователя. Если состояние пониженного напряжение остается в момент сброса бита SVSFG, он немедленно устанавливается снова модулем SVS.

Библиотека Компэла |

|

135 |

|

MSP430x1xxFamily

6.2.3. Изменение битов VLDx

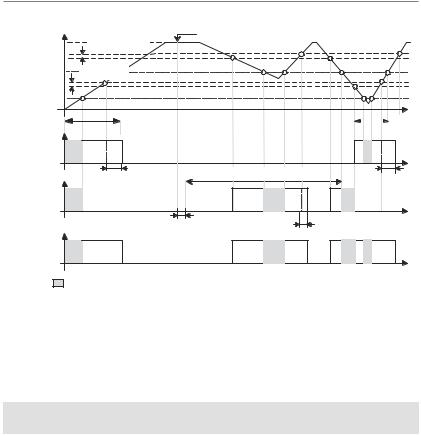

После изменения битов VLDx выдерживаются две установочных задержки, позволяющие установиться схеме SVS. В течение каждой задержки SVS не будет устанавливать SVSFG. Задержки td(SVSon) и tsettle показаны на рис. 6.2. Задержка td(SVSon) действует, когда VLDx изменяются от нуля к любому отличному от нуля значению, и составляет примерно 50 мкС. Задержка tsettle действует при изменении битов VLDx от любого ненулевого значения к любому другому ненулевому значению и составляет максимум ~12 мкС. Точные значения задержек см. в руководстве по конкретному устройству.

VLDx

15

14

4

3

2

1

0

0 |

1 |

2 |

2 |

15 |

3 |

|

|

|

|

|

VLD |

|

|

|

|

|

в зависимости |

|

td(SVSon) |

tsettle |

|

tsettle |

от времени |

1 |

|

tsettle |

|||

|

|

|

|

|

|

SVSON |

|

|

|

|

|

0 |

|

|

|

|

|

Рис. 6-2. Состояние бита SVSON при изменении VLDx

Во время задержек SVS не устанавливает флаг состояния пониженного напряжения и не сбрасывает устройство, а бит SVSON остается очищенным. Программное обеспечение может проверять бит SVSON для определения момента окончания задержки и начала достоверного мониторинга напряжения модулем SVS.

6.2.4. Рабочий диапазон SVS

Каждый уровень SVS имеет гистерезис для уменьшения чувствительности к малым изменениям питающего напряжения, когда величина AVCC близка к установленному порогу. Работа SVS и SVS/Brownout1 взаимодействие показано на рис. 6.3.

1 Brownout - понижение напряжения.

136 |

|

Библиотека Компэла |

|

Раздел VI. |

|

Супервизор напряжения питания |

|

AV |

Vhys(SVS_IT– ) |

Программная установка при VLD>0 |

|

|

|

||

CC |

|

|

|

V(SVS_IT – ) |

|

|

|

V(старт SVS) |

Vhys(B_IT–) |

|

|

V (B_IT – ) |

|

|

|

VCC(старт) |

|

|

|

|

Область |

|

Область |

Brownout |

Brownout |

|

Brown•Out |

1 |

|

|

|

0 |

|

|

|

SVSout |

td(BOR) |

Активность схемы SVS |

td(BOR) |

1 |

|

|

|

0 |

td(SVSon) |

td(SVSR) |

|

Установка POR |

|||

|

|

||

1 |

|

|

|

0 |

|

|

неопределенное состояние

Рис. 6-3. Рабочие уровни для SVS и схемы Brownout/сброс

6.3. Регистры SVS

Перечень регистров SVS приведен в таблице 6.1.

|

|

|

|

|

|

|

|

|

|

|

Таблица 6-1. Регистры SVS |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Регистр |

|

Краткое обозна- |

|

Тип регистра |

|

Адрес |

|

Исходное состо- |

|

|||||||

|

|

|

|

чение |

|

|

|

|

|

яние |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Управляющий |

|

|

|

SVSCTL |

|

|

Чтение/запись |

|

055h |

|

Сбрасывается пос- |

|

||||

|

регистр SVS |

|

|

|

|

|

|

|

|

ле POR |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

SVSCTL, регистр управления SVS |

|

|

|

|

|

|

|

|

|

|

|||||||

7 |

6 |

|

5 |

|

|

4 |

3 |

2 |

1 |

0 |

|

|

|||||

|

|

|

|

VLDx |

|

|

|

PORON |

|

SVSON |

SVSOP |

|

SVSFG |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

rw–0 |

rw–0 |

|

rw–0 |

|

|

rw–0 |

rw–0 |

|

r |

r |

|

rw–0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

Детектируемый уровень напряжения. Эти биты включают SVS |

|

||||||||||

|

VLDx |

|

Биты7-4 |

и позволяют выбрать номинальный пороговый уровень напря- |

|

||||||||||||

|

|

жения SVS. Точные параметры см. в руководстве на |

|

||||||||||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

0000 – SVS выключен |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Библиотека Компэла |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

137 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

MSP430x1xxFamily

|

|

0001 |

– 1.9В |

||

|

|

0010 |

– 2.1В |

||

|

|

0011 |

– 2.2В |

||

|

|

0100 |

– 2.3В |

||

|

|

0101 |

– 2.4В |

||

|

|

0110 |

– 2.5В |

||

|

|

0111 |

– 2.65В |

||

VLDx |

Биты 7-4 |

1000 |

– 2.8В |

||

1001 |

– 2.9В |

||||

|

|

||||

|

|

1010 |

– 3.05В |

||

|

|

1011 |

– 3.2В |

||

|

|

1100 |

– 3.35В |

||

|

|

1101 |

– 3.5В |

||

|

|

1110 |

– 3.7В |

||

|

|

1111 |

– Сравнение внешнего напряжения на входе SVSin со |

||

|

|

значением 1.2В |

|||

|

|

Включение POR. Этот бит разрешает флагу SVSFG вызывать |

|||

PORON |

Бит 3 |

сброс устройства сигналом POR. |

|||

0 |

– SVSFG не вызывает POR |

||||

|

|

||||

|

|

1 |

– Установка SVSFG приводит к генерации POR |

||

|

|

Включение SVS. Этот бит отражает состояние работы SVS. Этот |

|||

SVSON |

Бит 2 |

бит НЕ ВКЛЮЧАЕТ SVS. SVS включается установкой VLDx > 0. |

|||

0 |

– SVS выключен |

||||

|

|

||||

|

|

1 |

– SVS включен |

||

|

|

|

|||

|

|

Выход SVS. Этот бит отражает выходное значение компаратора |

|||

SVSOP |

Бит 1 |

SVS. |

|

||

0 |

– Выход компаратора SVS имеет высокий уровень |

||||

|

|

||||

|

|

1 |

– Выход компаратора SVS имеет низкий уровень |

||

|

|

Флаг SVS. Этот бит показывает состояние пониженного напря- |

|||

|

|

жения. Бит SVSFG остается установленным после устранения |

|||

|

|

состояния пониженного напряжения до сброса программным |

|||

SVSFG |

Бит 0 |

обеспечением. |

|||

|

|

0 |

– Состояние пониженного напряжения не произошло |

||

|

|

1 |

– Произошло либо уже присутствует состояние пониженного |

||

|

|

напряжения |

|||

Примечание: некорректная информация

Исходное состояние регистра SVSCTL указано неправильно. Содержимое регистра SVSCTL сбрасывается только по brownout-условию. Значение SVSCTL сохраняется при генерации сигнала POR и в случае низкого уровня на выводе RST/NMI (аппаратный сброс), и в случае, когда POR генерируется самим модулем SVS.

138 |

|

Библиотека Компэла |

|

Аппаратный умножитель

Раздел VII.

MSP430x1xxFamily

MSP430x1xxFamily

Аппаратный умножитель

В этом разделе описывается аппаратный умножитель. Аппаратный умножитель реализован в устройствах MSP430x14x и MSP430x16x.

7.1. Введение в аппаратный умножитель

Аппаратный умножитель является периферийным устройством и не является частью ЦПУ MSP430. Это означает, что его действия не пересекаются с действиями ЦПУ. Регистры умножителя – это периферийные регистры, которые загружаются и читаются командами ЦПУ.

Аппаратный умножитель поддерживает:

•Умножение без знака;

•Умножение со знаком;

•Умножение без знака с накоплением;

•Умножение со знаком и накоплением;

•16×16 бит, 16×8 бит, 8×16 бит, 8×8 бит.

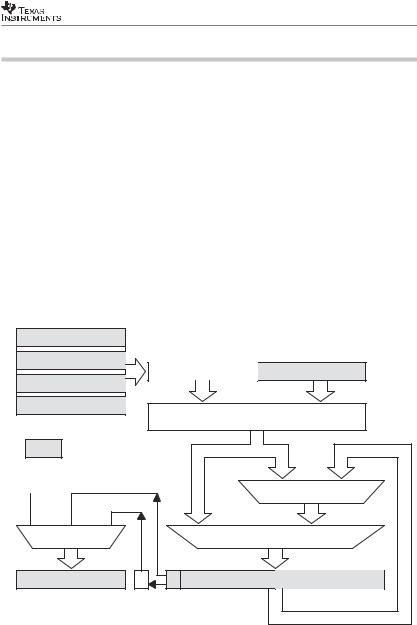

Блок-схема аппаратного умножителя показана на рис. 7.1.

150 rw

MPY 130h

|

MPYS 132h |

|

|

15 |

rw |

0 |

|

|

|

|

|

|

|

|

|

|

|

OP1 |

OP2 138h |

|

|

MAC 134h |

|

|

|

|

|

|

MACS 136h |

|

|

|

|

|

|

|

|

|

16 x 16 Умножитель |

|

|

|

Доступный |

|

|

|

|

|

|

регистр |

|

|

|

|

|

MPY = 0000 |

MACS MPYS |

|

|

32•разряднфй умножитель |

|

|

|

|

|

|

|

||

|

|

MAC |

|

|

|

|

|

|

|

|

MPY, MPYSMAC, MACS |

|

|

|

Мультиплексор |

|

|

32•разрядный умножитель |

|

|

SUMEXT 13Eh |

C |

S |

RESHI 13Ch |

RESLO 13Ah |

|

|

15 |

r |

0 |

31 |

rw |

rw |

0 |

|

Рис. 7-1. Блок-схема аппаратного умножителя |

|

||||

140 |

|

Библиотека Компэла |

|