- •И.А. Дубров

- •Содержание

- •Введение

- •Лабораторная работа 1 Изучение интегрированной среды разработки mplab

- •Методика выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 2 Изучение запоминающих устройств микроконтроллеровPic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 3 Изучение работы параллельных портов микроконтроллеровPic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 4 Изучение работы последовательных портов микроконтроллеров pic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 5 Изучение работы таймеров микроконтроллеров pic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 6 Изучение работы аналого-цифрового преобразователя микроконтроллеровPic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа 7 Изучение работы модуля захвата/сравнения/шим микроконтроллеровPic-micro

- •Порядок выполнения работы

- •Содержание отчета

- •Библиографический список

- •Приложение 1. Схема лабораторного макета

- •Bтfss— Условный переход при единичном битеbрегистраf

- •Call— Вызов подпрограммы

- •Goto— Переход по адресу

- •Incf— Декремент регистраf

- •Incfsz— Декремент регистраfи пропуск в случае нулевого результата

- •Iorlw— Побитное «или»Wи константыk

- •Retlw— Выход из подпрограммы с загрузкой в регистрWконстантыk

- •Return— Выход из подпрограммы

- •Rlf— Циклический сдвиг регистраfвлево через флаг переносаС

- •Rrf— Циклический сдвиг регистраfвправо через флаг переносаС

- •Sleep— Перейти в спящий режим

- •Основы микропроцессорной техники

- •620034, Екатеринбург, ул. Колмогорова 66.

Содержание отчета

В отчете необходимо привести постановку задачи, блок-схему алгоритма и текст программы на языке Ассемблер с исправлениями, возникшими на этапе отладки.

Контрольные вопросы

Что называется мультиплексированием портов ввода/вывода? Из-за чего оно понадобилось?

Какое значение надо записать в регистр TRISB, чтобы настроить вывод 3 порта PORTB как выход?

Лабораторная работа 4 Изучение работы последовательных портов микроконтроллеров pic-micro

Цель работы: изучение работы и программирование последовательных портов микроконтроллера PIC16F873A.

Микроконтроллер PIC16F873A имеет два последовательных порта ввода-вывода: синхронный последовательный порт MSSP и универсальный синхронно-асинхронный передатчик USART.

Синхронный последовательный порт MSSP предназначен для организации связи микроконтроллера с периферийными микросхемами или другими микроконтроллерами. При этом возможно использование двух интерфейсов: последовательный периферийный интерфейс SPI, либо двухпроводная последовательная шина для связи интегральных микросхем I2C. Для соединения через SPI используются четыре вывода микроконтроллера: -SS – выбор ведомого, SCK – тактовый сигнал, SDI – вход принимаемых данных и SDO – выход передаваемых данных. Для подключения к последовательной шине I2C используются два вывода: SCL – тактовый сигнал и SDA – данные. В лабораторном макете порт MSSP не задействован.

Универсальный синхронно-асинхронный приемопередатчик USART предназначен для организации связи микроконтроллера с персональным, либо промышленным компьютером по интерфейсам RS-232, RS-422 или RS-485. В лабораторном макете реализован интерфейс RS-232 без аппаратного управления потоком, позволяющий передавать и принимать какую либо информацию от COM порта персонального компьютера. При этом в схеме задействованы выводы микроконтроллера: TX – выход передаваемых данных и RX – вход принимаемых данных, а также микросхема ILX232N, предназначенная для согласования уровней сигналов на выводах последовательного порта микроконтроллера и персонального компьютера. Кроме того, к выводам TX и RX через инверторы подключены светодиоды HL8 и HL9, позволяющие контролировать наличие сигналов передачи и приема.

Передача и прием информации по интерфейсу RS-232 осуществляются в асинхронном дуплексном режиме.

Для управления работой портов ввода-вывода используются следующие РСН:

TXREG – регистр данных передатчика;

RCREG – регистр данных приемника;

TXSTA – регистр управления и статуса передатчика;

RCSTA – регистр управления и статуса приемника;

SPBRG – регистр генератора скорости обмена.

Если в программе используется обработка прерываний, то дополнительно задействуются регистры:

PIR1 – регистр флагов прерываний периферийных модулей;

PIE1 – регистр масок прерываний периферийных модулей.

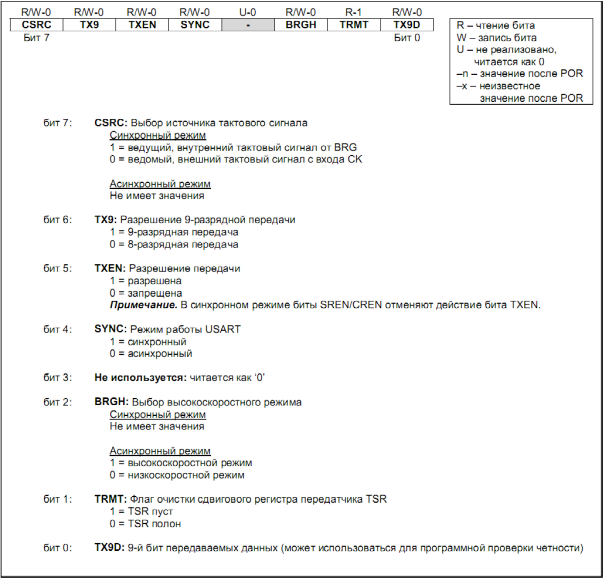

Назначение отдельных разрядов регистра TXSTA представлено на рис. 4.1, а RCSTA – на рис. 4.2.

Рис 4.1. Регистр управления и статуса передатчика TXSTA

В асинхронном

режиме скорость обмена информацией

зависит от коэффициента деления

генератора скорости обмена, который

задается записью определенного числа

в регистр SPBRG

и «0» либо «1» в разряд BRHG

регистра TXSTA.

Если BRHG

= 0, то скорость обмена определяется по

формуле ![]() ,

где FOSC

– частота тактового генератора, а X

– число, записанное в регистр генератора

скорости обмена SPBRG.

Если BRHG

= 1, то скорость обмена определяется по

формуле

,

где FOSC

– частота тактового генератора, а X

– число, записанное в регистр генератора

скорости обмена SPBRG.

Если BRHG

= 1, то скорость обмена определяется по

формуле ![]() .

.

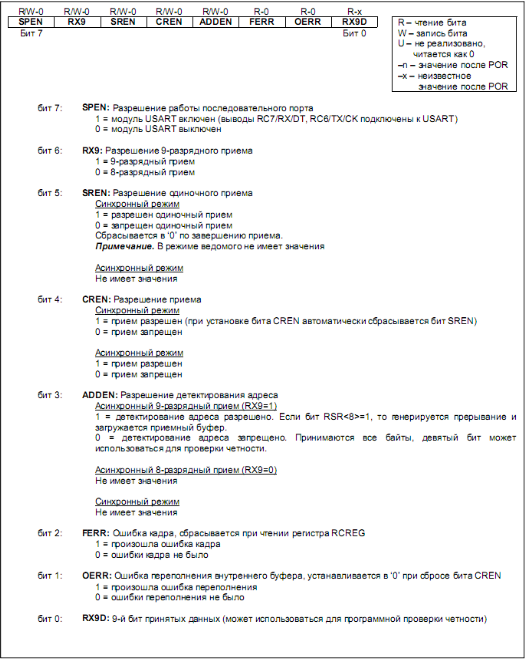

Рис. 4.2. Регистр управления и статуса приемника RCSTA

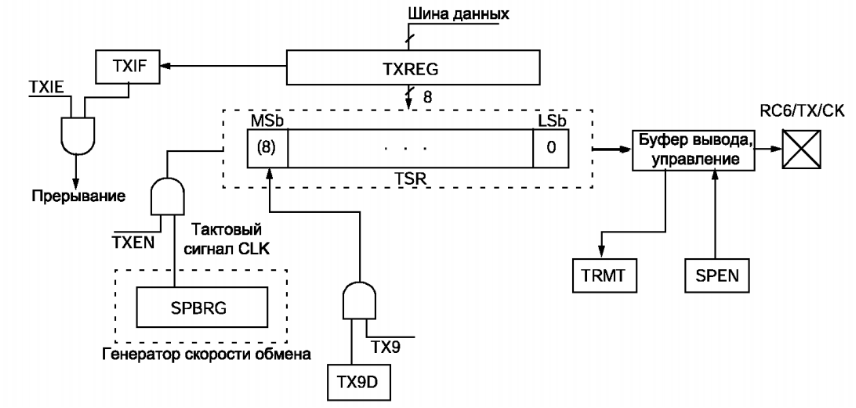

Структурная схема передатчика USART в асинхронном режиме приведена на рис. 4.3. Основным элементом в этой схеме является программно не доступный сдвиговый регистр передатчика TSR, осуществляющий преобразование информации из параллельного вида в последовательный. Для загрузки данных в регистр TSR используется буферный регистр специального назначения TXREG, расположенный в банке 0. После записи данных в регистр TXREG проверяется, что регистр TSR свободен (предыдущая передача завершена) и содержимое регистра TXREG копируется в регистр TSR. Освобождение регистра TXREG для новой информации подтверждается установкой в «1» флага TXIF в регистре PIR1. Если передача разрешена записью «1» в разряд TXEN регистра TXSTA, то на вход синхронизации регистра TSR начинают поступать импульсы от генератора скорости обмена, которые осуществляют сдвиг информации в TSR от старших разрядов к младшим. Из нулевого разряда регистра TSR данные поступают через буферную схему на вывод TX.

Скорость передачи зависит от коэффициента деления генератора скорости обмена, который задается записью определенного числа в регистр SPBRG и «0» либо «1» в разряд BRHG регистра TXSTA.

Рис. 4.3. Структурная схема передатчика USART

В дополнение к восьми разрядам, копируемым из регистра TXREG, может передаваться девятый разряд, обыкновенно используемый для обнаружения ошибок при передаче путем проверки на четность. Если разряд TX9 регистра TXSTA сброшен, то девятый разряд не передается, если взведен, то передается. Значение же самого девятого разряда задается программно, записью «0» или «1» в разряд TX9D регистра TXSTA. Кроме того к передаваемому байту информации автоматически в начале добавляется нулевой стартовый бит, а в конце – единичный стоповый После окончания передачи и освобождения регистра TSR взводится флаг TRMT регистра TXSTA.

Работа USART может быть полностью запрещена записью «0» в разряд SPEN регистра RCSTA.

Для передачи одного информации через USART необходимо выполнить следующую последовательность действий:

– установить требуемую скорость передачи с помощью регистра SPBRG и бита BRHG в регистре TXSTA;

– выбрать асинхронный режим сбросом бита SYNC в «0» и установкой бита SPEN в «1»;

– если необходимо, разрешить прерывания установкой бита TXIE в регистре PIE1 в «1» (биты GIE и PEIE в регистре INTCON так же должны быть установлены в «1»);

– если передача 9-разрядная, установить бит TX9 в «1» и записать 9-й бит данных в TX9D;

– разрешить передачу установкой бита TXEN в «1»;

– записать данные в регистр TXREG;

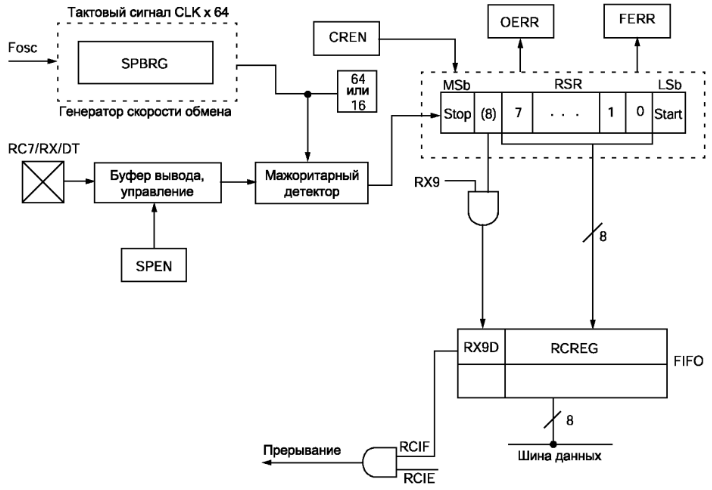

Структурная схема приемника USART в асинхронном режиме приведена на рис. 4.4.

Рис. 4.4. Структурная схема приемника USART

В этой схеме главным является сдвиговый регистр RSR, осуществляющий преобразование последовательного кода, поступающего на вход приемника, в параллельный. Работа приемника, так же как и передатчика разрешается либо запрещается записью, соответственно, «1» или «0» в разряд SPEN регистра RCSTA, а так же установкой либо сбросом разряда CREN регистра RCSTA. Если прием разрешен, то сигнал с входа RX попадает на мажоритарный детектор, назначение которого – с максимальной достоверностью определить логический уровень сигнала, поступающего в данном импульсе. Далее последовательный код поступает на вход сдвигового регистра RSR. На вход синхронизации этого-же регистра поступают тактовые импульсы от генератора скорости обмена. Частота следования этих импульсов равна частоте синхронизации передатчика (скорость приема и передачи одинаковы).

После поступления стопового импульса и заполнения регистра RSR, байт данных копируется в двухуровневый буфер приемника, построенный по принципу «Первым пришел – первым вышел» FIFO, но только в том случае если он заполнен не полностью. Считать данные из этого буфера можно обратившись к РСН RCREG (чтобы считать оба байта необходимо команду считывания повторить). Девятый бит копируется в разряд RX9D регистра RCSTA, но только в том случае, если это разрешено записью «1» в разряд RX9 этого же регистра.

Окончание приема информации приводит так же к установке в единичное значение флага RCIF в регистре PIR1 и генерации запроса прерывания, если это прерывание было разрешено записью «1» в разряд RCIE регистра PIE1.

При наличии помех в линии связи возможно нарушение правильной работы приемника. В микроконтроллере PIC16 детектируются всего два вида ошибок: ошибка кадра и переполнение буфера FIFO. Ошибка кадра возникает при потере стартового или стопового импульсов, при этом недостоверная информация из регистра RSR не копируется, но взводится флаг FERR в регистре RCSTA. Переполнение буфера FIFO может произойти, если предыдущая информация не была из него вовремя считана, при этом данные, находящиеся в регистре RSR, будут потеряны, но взведется флаг OERR в регистре RCSTA.

Рекомендуемые действия при приеме данных в асинхронном режиме:

Установить требуемую скорость передачи с помощью регистра SPBRG и бита BRHG в регистре TXSTA.

Выбрать асинхронный режим сбросом бита SYNC в «0» и установкой бита SPEN в «1».

Если необходимо, разрешить прерывания установкой бита RCIE в регистре PIE1 в «1» (биты GIE и PEIE в регистре INTCON так же должны быть установлены в «1»).

Если прием 9-разрядный, установить бит RX9 в «1».

Разрешить прием установкой бита CREN в «1».

Ожидать установку бита RCIF, или прерывание, если оно было разрешено.

Проверить флаги ошибок и, если прием 9-разрядный, считать 9-й разряд из бита RX9D.

Считать 8 бит данных из регистра RCREG.

При возникновении ошибки переполнения буфера FIFO сбросить бит RCEN в «0».

Для работы с последовательным портом персонального компьютера можно воспользоваться программой Hyper Terminal, входящей в состав операционной системы Windows. При этом в свойствах COM порта необходимо указать: Скорость (бит/с): 19200, Биты данных: 8, Четность: Нет, Стоповые биты: 1, Управление потоком: Нет.