2. Автомати з пам`яттю

Автомати з пам`яттю – це такі дискретні пристрої, в яких крім логічних елементів містяться елементи пам’яті. Автомати з пам’яттю забезпечують зберігання інформації, чого не могли виконати комбінаційні схеми.

Для зберігання інформації використовують спеціальні елементи пам’яті, які зберігають 1 біт інформації й називаються тригерами. Комбінаційні схеми іноді називають однотактними автоматами, їх вихідний сигнал формується тільки при наявності вхідного сигналу.

Автомати з пам’яттю – багатотактні автомати, які функціонують в дискретному часі. Це означає, що автомати з пам’яттю виконують перетворення інформації в окремі дискретні моменти часу.

Дискретні моменти часу можуть задаватися зовнішніми подіями.

Якщо дискретні моменти часу задаються зовнішніми подіями, то може бути побудований асинхронний автомат з пам’яттю. На відміну від комбінаційної схеми автомат з пам’яттю зберігає свою передісторію. Крім того, вихідні сигнали автомата з пам’яттю існують навіть тоді , коли відсутні вхідні сигнали.

В залежності від способа формування вихідних сигналів автомати з пам’яттю ділять на 2 класи:

- автомати Мілі

- автомати Мура

У автоматів Мілі вихідний сигнал залежить від вхідного сигналу та внутрішнього стану на попередньому такті.

У автоматів Мура вихідний сигнал залежить тільки від внутрішнього стану.

Автомати Мілі і Мура відрізняються записом функції переходів.

2.1. Реверсивний лічільник,працюючий в коді Грея с М=14 (АП1)

Лічильник імпульсів - автомат з пам'яттю, призначений для підрахунку імпульсів. На вхід надходить імпульс. Кожному підрахованому імпульсу відповідає код внутрішнього стану. На виході паралельный двійковий код.

Основним

параметром є N-модуль

рахунку - число імпульсів для підрахунку

яких призначений лічильник.

Основним

параметром є N-модуль

рахунку - число імпульсів для підрахунку

яких призначений лічильник.

Розрізняють наступні види лічильників:

що складають (підсумовуючі)- прямого рахунку

що віднімають - зворотного рахунку

реверсивні (комбіновані)

по модулю - визначають кількість станів

двійково-десяткові

працюючі в коді Грея

Основні етапи проектування лічильників:

Виходячи із заданого модуля визначається число тригерів

n = ]log2N[, де ][- найближче більше ціле число

2. Число тригерів визначає розмірність кодів внутрішнього стану

3.Скласти граф переходів-виходів лічильника

4. Вибрати тип тригера

5. Побудувати функціональну таблицю лічильника, користуючись графом переходів-виходів і таблицею збудження обраного типа тригера

6. З функціональної таблиці одержати рівняння для функцій, що описують вхідні сигнали тригерів

7.Вибрати базис для побудови комбінаційної частини

8. Побудувати схему

9. Перевірити правильність роботи.

У

своїй роботі я буду реалізовувати

рверсивний лічильник,

працюючий в коді Грея с М=14 за допомогою

![]() тригерів та мікросхеми1533ЛЕ1, виходячи

з того, що модуль дорівнює 14, то

використовується 4 тригери. Закодуємо

14 значень кодів внутрішнього стану в

коді Грея, як це зробила показано на

Рисунку 2.11. Будуємо графф переходів

виходів (Рисунок 2.12),талиця збудження

вибраного мною тригера зображена в

Таблиці 2.11, а функціональна таблиця

буде виглядати так, як це показано в

Таблиці 2.12.

тригерів та мікросхеми1533ЛЕ1, виходячи

з того, що модуль дорівнює 14, то

використовується 4 тригери. Закодуємо

14 значень кодів внутрішнього стану в

коді Грея, як це зробила показано на

Рисунку 2.11. Будуємо графф переходів

виходів (Рисунок 2.12),талиця збудження

вибраного мною тригера зображена в

Таблиці 2.11, а функціональна таблиця

буде виглядати так, як це показано в

Таблиці 2.12.

|

A |

t |

t+1 |

Тригери | |||||||||||||

|

y1 |

y2 |

y3 |

y4 |

y1 |

y2 |

y3 |

y4 |

|

|

|

|

|

|

|

| |

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

~ |

1 |

~ |

1 |

~ |

0 |

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

~ |

1 |

~ |

0 |

1 |

~ |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

10 |

1 |

0 |

1 |

~ |

0 |

1 |

~ |

1 |

1 |

~ |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

~ |

1 |

~ |

~ |

1 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

~ |

1 |

1 |

~ |

1 |

~ |

|

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

~ |

~ |

1 |

1 |

~ |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

~ |

~ |

1 |

~ |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

~ |

1 |

~ |

1 |

~ |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

~ |

1 |

~ |

1 |

~ |

|

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

~ |

1 |

0 |

1 |

1 |

~ |

~ |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

~ |

1 |

0 |

1 |

~ |

|

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

~ |

1 |

1 |

~ |

1 |

0 |

~ |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

~ |

1 |

1 |

0 |

1 |

~ |

1 |

~ |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

~ |

1 |

1 |

~ |

~ |

1 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

~ |

|

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

~ |

1 |

1 |

0 |

~ |

1 |

~ |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

~ |

1 |

~ |

1 |

~ |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

~ |

1 |

~ |

1 |

~ |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

~ |

1 |

~ |

~ |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

~ |

1 |

~ |

1 |

0 |

~ |

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

~ |

~ |

1 |

1 |

~ |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

~ |

1 |

1 |

~ |

~ |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

~ |

1 |

0 |

~ |

1 |

1 |

~ |

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

~ |

~ |

1 |

~ |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

~ |

1 |

0 |

1 |

1 |

~ |

1 |

~ |

|

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

~ |

1 |

1 |

~ |

0 |

1 |

~ |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

~ |

1 |

1 |

~ |

1 |

0 |

1 |

~ |

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

~ |

1 |

0 |

1 |

~ |

1 |

~ |

1 |

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

~ |

1 |

1 |

~ |

1 |

~ |

|

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

~ |

1 |

1 |

0 |

1 |

~ |

~ |

1 |

|

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

~ |

1 |

1 |

0 |

1 |

0 |

1 |

~ |

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

~ |

1 |

~ |

1 |

~ |

1 |

Таблиця 2.12

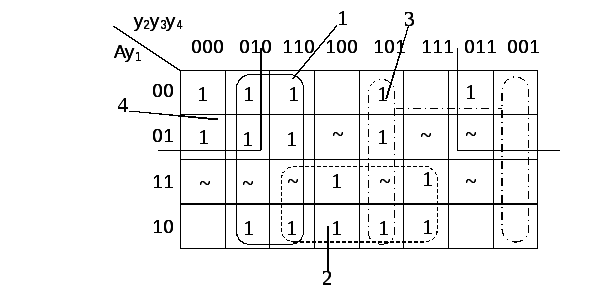

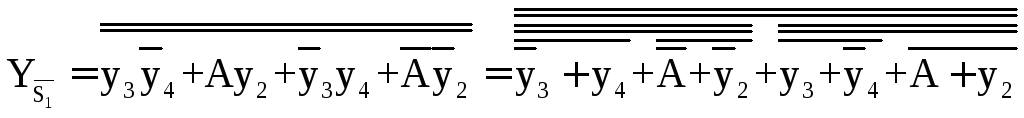

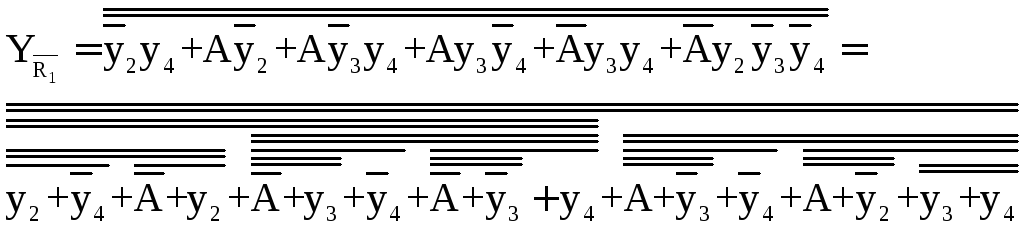

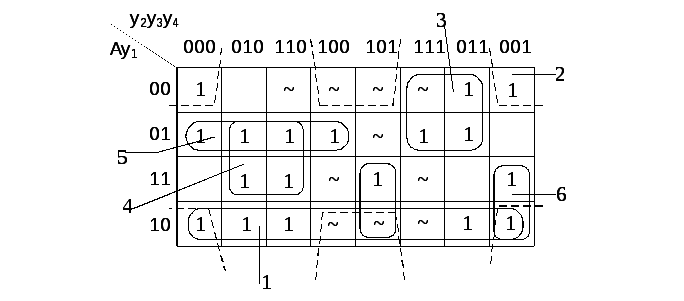

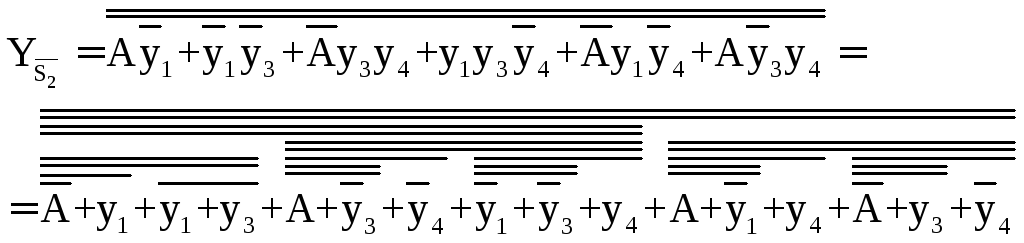

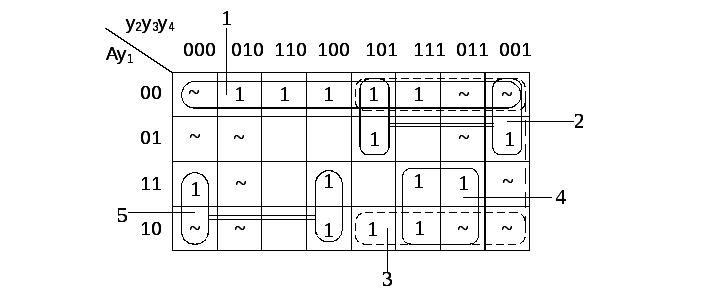

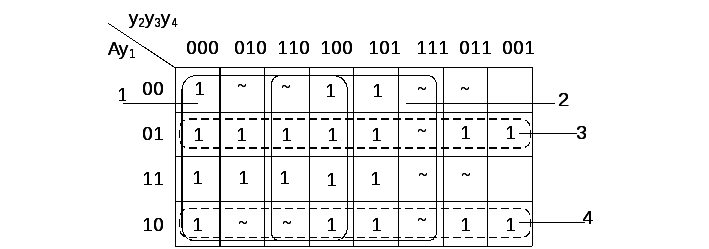

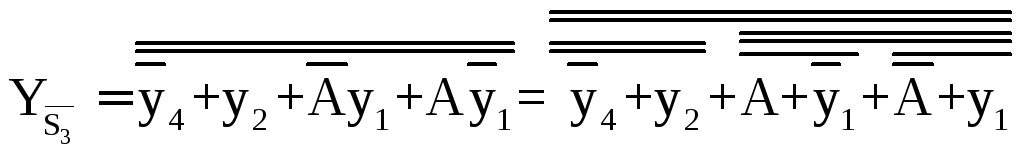

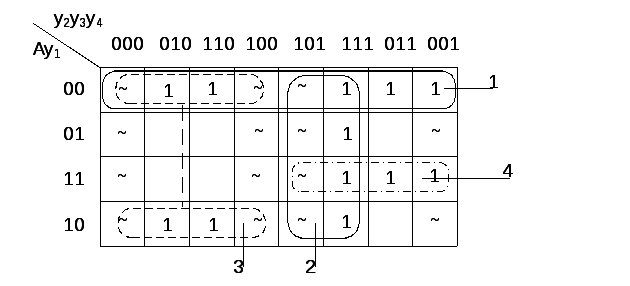

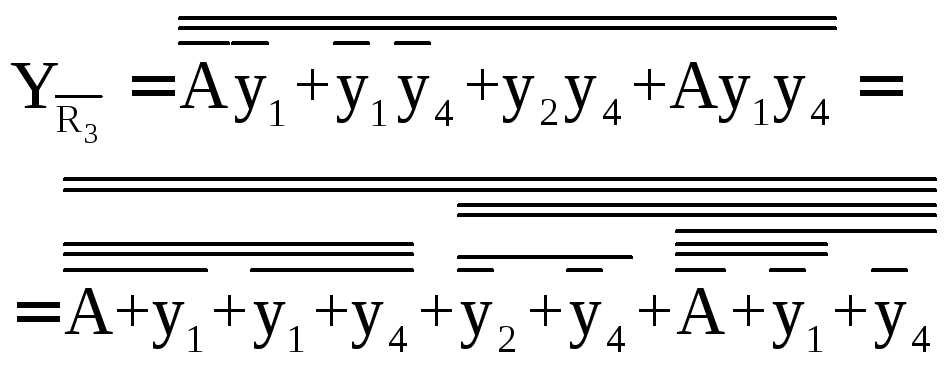

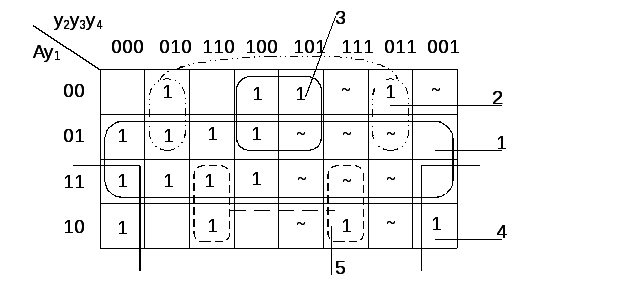

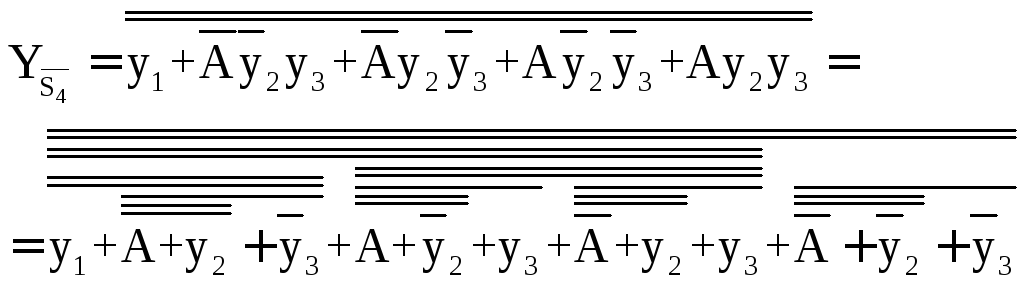

За

допомогою функціональної таблиці

будуємо карти Карно, визначаємо підкуби,

їх внески, приводимо до відповідного

базису та реалізовуємо автомат з

пам’яттю на схемі.

За

допомогою функціональної таблиці

будуємо карти Карно, визначаємо підкуби,

їх внески, приводимо до відповідного

базису та реалізовуємо автомат з

пам’яттю на схемі.

Побудвана схема представлена в Додатку Б.