2.1 П’ятирозрядний регістр зсуву вліво (ап2)

Регістр зсуву – це автомат з пам’ятю, який зсуває сигнали, які подаються на вхід, 0 або 1 від молодшого розряду до старшого.

Регістр розглядається, як пристрій для запам’ятовування даних. Визначаю, що для реалізації даної схеми потрібно взяти 5 тригерів. По завданню використовую JK – тригери. Потім будую функціональну таблицю (таблиця 8) та визначаю які сигнали потрібно подавати на входи JK – тригерів для отримання потрібного результату.

Таблиця 8 – функціональна таблиця п’ятирозрядного регістру здвигу:

|

X |

t |

t+1 |

Тр.1 |

Тр.2 |

Тр.3 |

Тр.4 |

Тр.5 |

|||||||||||||

|

y1 |

y2 |

y3 |

y4 |

y5 |

y1 |

y2 |

y3 |

y4 |

y5 |

J1 |

K1 |

J2 |

K2 |

J3 |

K3 |

J4 |

K4 |

J5 |

K5 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

1 |

0 |

~ |

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

0 |

~ |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

~ |

1 |

~ |

~ |

1 |

0 |

~ |

0 |

~ |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

~ |

1 |

~ |

~ |

1 |

1 |

~ |

~ |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

~ |

1 |

~ |

~ |

0 |

~ |

1 |

0 |

~ |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

~ |

1 |

~ |

~ |

0 |

~ |

0 |

~ |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

~ |

~ |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

~ |

~ |

1 |

0 |

~ |

1 |

~ |

~ |

1 |

|

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

~ |

~ |

1 |

1 |

~ |

~ |

1 |

0 |

~ |

|

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

~ |

~ |

1 |

1 |

~ |

~ |

0 |

~ |

1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

~ |

~ |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

~ |

~ |

0 |

~ |

1 |

1 |

~ |

~ |

1 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

~ |

~ |

0 |

~ |

0 |

~ |

1 |

0 |

~ |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

~ |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

Продовження

таблиці 8:

Продовження

таблиці 8:

|

X |

t |

t+1 |

Тр.1 |

Тр.2 |

Тр.3 |

Тр.4 |

Тр.5 |

|||||||||||||

|

y1 |

y2 |

y3 |

y4 |

y5 |

y1 |

y2 |

y3 |

y4 |

y5 |

J1 |

K1 |

J2 |

K2 |

J3 |

K3 |

J4 |

K4 |

J5 |

K5 |

|

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

~ |

1 |

0 |

~ |

1 |

~ |

~ |

1 |

0 |

~ |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

~ |

1 |

0 |

~ |

1 |

~ |

~ |

0 |

~ |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

~ |

1 |

1 |

~ |

~ |

1 |

0 |

~ |

0 |

~ |

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

~ |

1 |

1 |

~ |

~ |

1 |

1 |

~ |

~ |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

~ |

1 |

1 |

~ |

~ |

0 |

~ |

1 |

0 |

~ |

|

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

~ |

1 |

1 |

~ |

~ |

0 |

~ |

0 |

~ |

1 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

~ |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

|

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

~ |

0 |

~ |

1 |

0 |

~ |

1 |

~ |

~ |

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

~ |

0 |

~ |

1 |

1 |

~ |

~ |

1 |

0 |

~ |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

~ |

0 |

~ |

1 |

1 |

~ |

~ |

0 |

~ |

1 |

|

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

1 |

~ |

~ |

1 |

|

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

0 |

~ |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

~ |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

1 |

1 |

~ |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

0 |

~ |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

~ |

1 |

~ |

~ |

1 |

0 |

~ |

1 |

~ |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

~ |

1 |

~ |

~ |

1 |

1 |

~ |

~ |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

~ |

1 |

~ |

~ |

0 |

~ |

1 |

1 |

~ |

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

~ |

1 |

~ |

~ |

0 |

~ |

0 |

~ |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

~ |

~ |

1 |

0 |

~ |

0 |

~ |

1 |

~ |

|

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

~ |

~ |

1 |

0 |

~ |

1 |

~ |

~ |

0 |

Продовження

таблиці 8:

Продовження

таблиці 8:

|

X |

t |

t+1 |

Тр.1 |

Тр.2 |

Тр.3 |

Тр.4 |

Тр.5 |

|||||||||||||

|

Y1 |

y2 |

y3 |

y4 |

y5 |

y1 |

y2 |

y3 |

y4 |

y5 |

J1 |

K1 |

J2 |

K2 |

J3 |

K3 |

J4 |

K4 |

J5 |

K5 |

|

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

~ |

~ |

1 |

1 |

~ |

~ |

1 |

1 |

~ |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

~ |

~ |

1 |

1 |

~ |

~ |

0 |

~ |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

~ |

~ |

0 |

~ |

1 |

0 |

~ |

1 |

~ |

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

~ |

~ |

0 |

~ |

1 |

1 |

~ |

~ |

0 |

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

~ |

~ |

0 |

~ |

0 |

~ |

1 |

1 |

~ |

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

~ |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

~ |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

~ |

|

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

~ |

1 |

0 |

~ |

0 |

~ |

1 |

~ |

~ |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

~ |

1 |

0 |

~ |

1 |

~ |

~ |

1 |

1 |

~ |

|

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

~ |

1 |

0 |

~ |

1 |

~ |

~ |

0 |

~ |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

~ |

1 |

1 |

~ |

~ |

1 |

0 |

~ |

1 |

~ |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

~ |

1 |

1 |

~ |

~ |

1 |

1 |

~ |

~ |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

~ |

1 |

1 |

~ |

~ |

0 |

~ |

1 |

1 |

~ |

|

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

~ |

1 |

1 |

~ |

~ |

0 |

~ |

0 |

~ |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

~ |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

1 |

~ |

|

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

~ |

0 |

~ |

1 |

0 |

~ |

1 |

~ |

~ |

0 |

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

~ |

0 |

~ |

1 |

1 |

~ |

~ |

1 |

1 |

~ |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

~ |

0 |

~ |

1 |

1 |

~ |

~ |

0 |

~ |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

~ |

0 |

~ |

0 |

~ |

1 |

0 |

~ |

1 |

~ |

|

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

~ |

0 |

~ |

0 |

~ |

1 |

1 |

~ |

~ |

0 |

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

1 |

~ |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

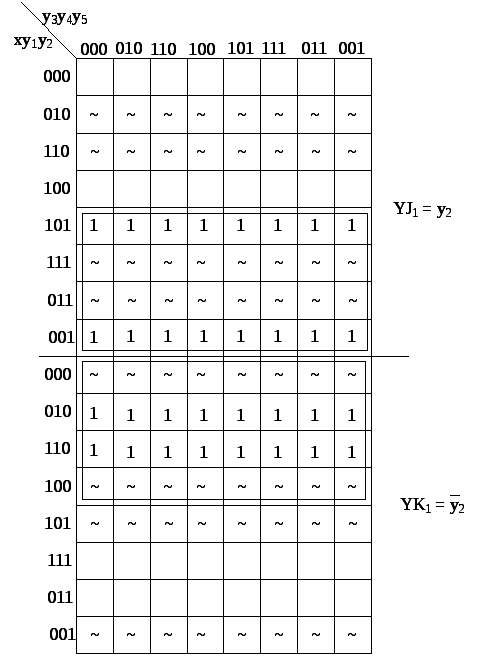

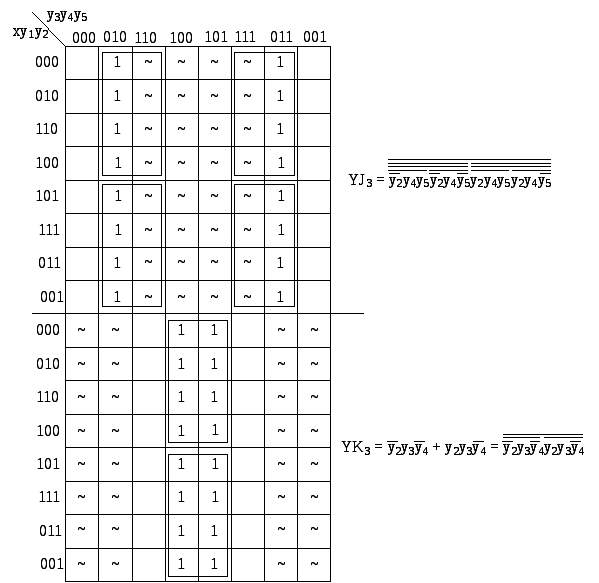

Будую карти Карно та одержую функції для кожного входу кожного тригера.

Перший

тригер:

Перший

тригер:

Другий

тригер:

Другий

тригер:

Третій

тригер:

Третій

тригер:

Четвертий

тригер:

Четвертий

тригер:

П’ятий

тригер:

П’ятий

тригер:

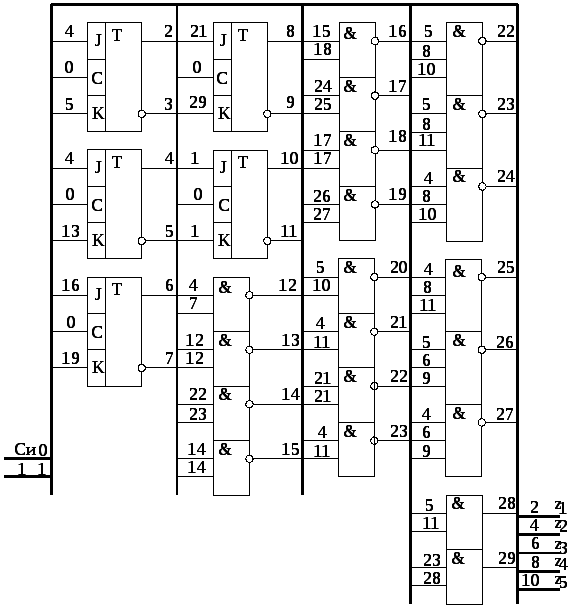

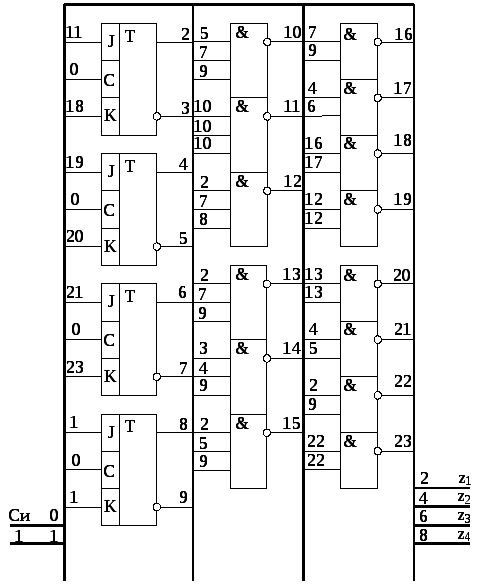

Схема п’ятирозрядного регістру зсуву вліво зображено на рисунку 6.

Рисунок

6 – п’ятирозрядний регістр зсуву вліво

Рисунок

6 – п’ятирозрядний регістр зсуву вліво

2.2 Двійковий лічильник зворотнього рахунку М = 10 (АП1)

Лічильник імпульсів – це автомат з пам’ятю, який підраховує число імпульсів. Лічильники використовуються для управління послідовністю операцій. Вихідні сигнали тригерів, які входять у лічильник, розглядаються спільно, визначаючи при цьому стани лічильника в цілому.

За

завданням курсового проекту мені треба

розробити двійковий лічильник зворотнього

рахунку за модулем 10 (М = 10).

За

завданням курсового проекту мені треба

розробити двійковий лічильник зворотнього

рахунку за модулем 10 (М = 10).

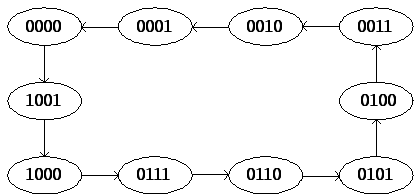

Будую граф переходу (Рисунок 7).

Рисунок 7 – граф переходу

Так як построїти схему мені потрібно на JK – тригерах будую функціональну таблицю для JK – тригерів. (Таблиця 9)

Таблиця 9

-

y(t)

y(t+1)

Тр.1

Тр.2

Тр.3

Тр.4

y1

y2

y3

y4

y1

y2

y3

y4

J1

K1

J2

K2

J3

K3

J4

K4

0

0

0

0

1

0

0

1

1

~

0

~

0

~

1

~

0

0

0

1

0

0

0

0

0

~

0

~

0

~

~

1

0

0

1

0

0

0

0

1

0

~

0

~

~

1

1

~

0

0

1

1

0

0

1

0

0

~

0

~

~

0

~

1

0

1

0

0

0

0

1

1

0

~

~

1

1

~

1

~

0

1

0

1

0

1

0

0

0

~

~

0

0

~

~

1

0

1

1

0

0

1

0

1

0

~

~

0

~

1

1

~

0

1

1

1

0

1

1

0

0

~

~

0

~

0

~

1

1

0

0

0

0

1

1

1

~

1

1

~

1

~

1

~

1

0

0

1

1

0

0

0

~

0

0

~

0

~

~

1

Двійковий лічильник зворотнього рахунку з М = 10 має шість заборонених станів 1010, 1011, 1100, 1101, 1110, 1111.

Коли

відбувається збій лічильника і сигнал

приходить на одне із заборонених станів,

лічильник автоматично переходить в

робочий стан 0000, для того щоб робота

лічильника не зупинялась і була

правильна.(Таблиця 10)

Коли

відбувається збій лічильника і сигнал

приходить на одне із заборонених станів,

лічильник автоматично переходить в

робочий стан 0000, для того щоб робота

лічильника не зупинялась і була

правильна.(Таблиця 10)

Таблиця 10 – функціональна таблиця переходу із заборонених станів в робочий стан 0000

-

y(t)

y(t+1)

Тр.1

Тр.2

Тр.3

Тр.4

y1

y2

y3

y4

y1

y2

y3

y4

J1

K1

J2

K2

J3

K3

J4

K4

1

0

1

0

0

0

0

0

~

1

0

~

~

1

0

~

1

0

1

1

0

0

0

0

~

1

0

~

~

1

~

1

1

1

0

0

0

0

0

0

~

1

~

1

0

~

0

~

1

1

0

1

0

0

0

0

~

1

~

1

0

~

~

1

1

1

1

0

0

0

0

0

~

1

~

1

~

1

0

~

1

1

1

1

0

0

0

0

~

1

~

1

~

1

~

1

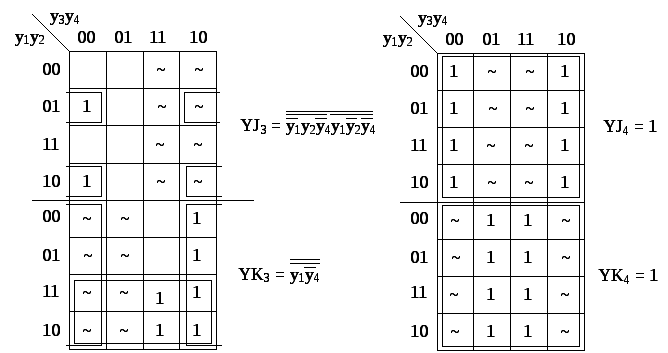

Будую карти Карно та одержую функції для кожного входу кожного тригера.

Перший тригер:

Другий

тригер:

Другий

тригер:

Третій та четвертий тригери:

Схема

двійкового лічильника зворотнього

рахунку з М = 10 зображена на рисунку 8.

Схема

двійкового лічильника зворотнього

рахунку з М = 10 зображена на рисунку 8.

Рисунок 8 – Схема двійкового лічильника зворотнього рахунку з М = 10

2.3 Суматор послідовної дії для чотирьохрозрядних двійкових чисел, без знаку (АП3)

Суматор - пристрій, який виконує операції арифметичного складання над двійковими числами.

Залежно

від способу обробки чисел розрізняють

послідовні і паралельні суматори.

Послідовні суматори будуються на основі

однорозрядної схеми, що підсумовує. У

таких пристроях складання двох чисел

проводиться порозрядно, послідовно в

часі .

.

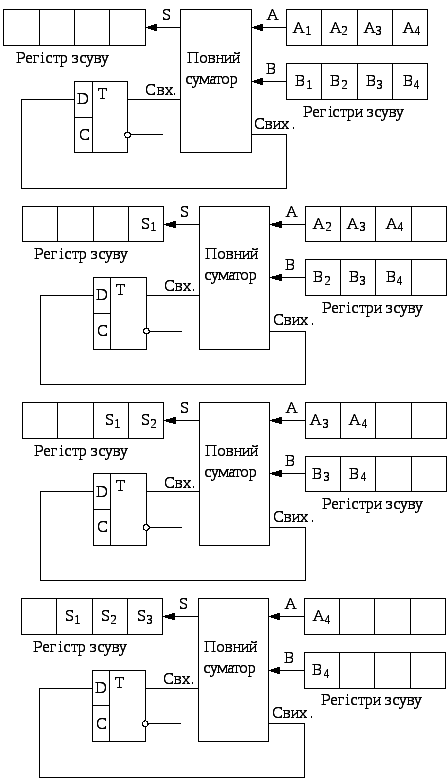

В послідовному способі складання використовується тільки один повний суматор. (Рисунок 9)

Рисунок 9 – умовне позначення повного суматор

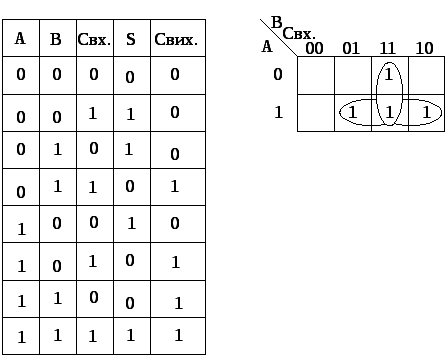

Для складання найменш значимих цифр, потрібен напівсуматор, а для складання всіх інших цифр – повний суматор. Я ми бачимо на рисунку 9, схема повного суматора містить три входи: два з них відповідають двійковим кодам А і В, а третій – переносу із попереднього розряду Свх. Крім того схема має два виходи: суму S і переніс в наступний розряд Свих.

Таблиця 11 – таблиця істинності повного суматора

При

використанні повного суматора спільно

з регістрами зсуву сумарний пристрій

послідовної дії умовно виглядає так,

як зображено на рисунку 10.

При

використанні повного суматора спільно

з регістрами зсуву сумарний пристрій

послідовної дії умовно виглядає так,

як зображено на рисунку 10.

Продовження рисунку 10

Рисунок 10 – умовне зображення принципу дії та вигляду суматора послідовної дії

В схемі

є два ідентичних регістра зсуву (А і В

) ,

які пов’язані з входами А та В єдиного

повного суматора. Ці регістри розглянуті

в курсовому проекті в розділі 2.1 Вихідна

сума накопичується в регістрі суми

(зображен з ліва).

,

які пов’язані з входами А та В єдиного

повного суматора. Ці регістри розглянуті

в курсовому проекті в розділі 2.1 Вихідна

сума накопичується в регістрі суми

(зображен з ліва).

На першій діаграмі регістри А і В заповнені двійковими числами А1А2А3А4 і В1В2В3В4.

На першому тактовому імпульсі сумуються значення розряда N = 23 (А1 і В1); сума (S1) з’являється в регістрі суми.

На другому тактовому імпульсі сумуються значення розряду N = 22 (А2 і В2) і перенос, який поступає на вхід Свх. суматора від тригера – затримки. Результат (S2) вводиться в регістр суми. Попередня сума (S1) зсувається вліво.

На третьому тактовому імпульсі сумуються А3, В3 і новий переніс на вході Свх. Результат (S3) розміщується в регістрі суми.

На четвертому (і останнєму) тактовому імпульсі сумуються А4, В4 і переніс на вході Свх. Ця кінцева сума (S4) відправляється в регістр суми – і задача вирішена.

Після чотирьох тактових імпульсів в регістрі суми знаходиться двійкове число S1S2S3S4.

Явно,

що в даній системі тактові входи всіх

трьох регістрів зсуву і тригера з

затримкою пов’язані між собою. Відмітимо

також, що в кожний момент часу сумуються

тільки два біта. Біти – які сумуються

послідовно подаються в повний суматор

з регістрів зсуву. Саме з цього дана

система називається послідовним

суматором.

Явно,

що в даній системі тактові входи всіх

трьох регістрів зсуву і тригера з

затримкою пов’язані між собою. Відмітимо

також, що в кожний момент часу сумуються

тільки два біта. Біти – які сумуються

послідовно подаються в повний суматор

з регістрів зсуву. Саме з цього дана

система називається послідовним

суматором.

Подача більшої кількості імпульсів призведе до зсуву бітів кожного розряду з вірних позицій в регістрі суми, і на індикаторі ми побачимо невірний результат.

2.4 Вичитач чотирьохрозрядних двійкових чисел зі знаком на базі суматора паралельної дії (КС3)

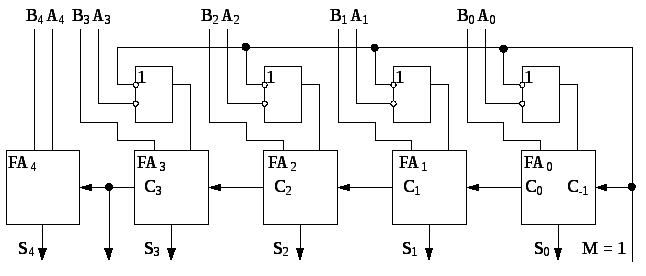

На рисунку 11 зображено вичитач чотирьохрозрядних двійкових чисел зі знаком на базі суматора паралельної дії. Для складання чисел в паралельному суматорі використовуються двійкові числа в прямому коді, а для вичитач чотирьохрозрядних двійкових чисел зі знаком, від’ємник повинен бути в допоміжному коді. Для цього в схемі використовуються управляємі інвертори, які служать для інвертування цифр В1В2В3В4 в тому випадку коли М = 1. Сигнал М також подається на вхід, формуючи функцію переносу суматора для найменших значимих розрядів чисел. Коли М = 1, С-1 = 1 і ця одиниця додається к найменшому значимому розряду оберненого коду числа, тим самим формується допоміжний код.

Для реалізації схеми необхідно мати п’ять повних суматорів, причому суматор FA4 використовується для складання знакових розрядів А4 і В4.

Рисунок

11 – Вичитач чотирьохрозрядних двійкових

чисел зі знаком на базі суматора

паралельної дії (КС3)

Рисунок

11 – Вичитач чотирьохрозрядних двійкових

чисел зі знаком на базі суматора

паралельної дії (КС3)