- •Опорний конспект лекцій по курсу "аналогові та цифрові вимірювальні прилади" (Частина №1)

- •Магнітоелектричні прилади Магнітоелектричний вимірювальний перетворювач

- •Магнітоелектричні амперметри

- •Магнітоелектричні вольтметри

- •Магнітоелектричні омметри

- •Електромагнітні прилади Електромагнітний вимірювальний перетворювач

- •Електромагнітні амперметри та вольтметри

- •Електродинамічні прилади Електродинамічний вимірювальний перетворювач

- •Амперметри, вольтметри і ватметри електродинамічної системи

- •Феродинамічний вимірювальний перетворювач

- •Електростатичні прилади

- •В момент часу напруга на конденсаторі с досягне такого значення

- •Розглянемо даний алгоритм на прикладі переведення чисел із десяткової в двійкову системи числення.

- •Аналого-цифровим перетворювачем називають засіб вимірювання, в якому створюється кодовий сигнал вимірювальної інформації.

- •Параметри ацп

- •Виділяють такі параметри ацп, що характеризують їхню динамічну точність.

Аналого-цифровим перетворювачем називають засіб вимірювання, в якому створюється кодовий сигнал вимірювальної інформації.

Суттєвим недоліком вищерозглянутих АЦП (цифрових вимірювальних приладів) є низька завадостійкість. Дійсно, вибірки миттєвих значень складаються з миттєвих значень вимірюваної напруги Uх і завади Uз, яка після цифрової обробки послідовності вибірок може бути зменшена. Але для цього необхідно затратити додатковий час і обчислювальні ресурси. В АЦП, що розглядаються нижче, вхідна напруга інтегрується або неперервно, або на заданому часовому інтервалі, тривалість якого кратна періоду завади. Такий підхід в багатьох випадках дозволяє зменшити вплив завади ще на етапі аналого-цифрового перетворення. Платою за підвищення точності є зменшення швидкодії інтегрувальних АЦП.

АЦП двотактного інтегрування

Структурна схема АЦП, що працює за два основних такти (АЦП двотактного інтегрування), наведена на рис. 4.36. Перший такт – інтегрування, другий такт – лічба.

Рисунок 4.36

Перший такт. На цій стадії АЦП-перетворення ключ S1 замкнено, а ключ S2 розімкнений. Інтегратор І інтегрує вхідну напругу Uх протягом постійного проміжку часу t1. Як таймер, що формує даний часовий інтервал, використовується лічильник СТ з таким коефіцієнтом переліку, що

![]() .

(4.41)

.

(4.41)

В момент завершення операції інтегрування напруга на виході інтегратора складає

.

(4.42)

.

(4.42)

де Uх СР – середнє значення вхідної напруги протягом проміжку часу t1.

Д

Рисунок

4.37

Коли вихідна напруга інтегратора досягає нульового рівня, компаратор перемикається і процес лічби завершується. Часовий інтервал, в якому здійснюється стадія лічби, визначається таким рівнянням

.

(4.43)

.

(4.43)

Підставивши значення з (4.42) для UI(t) в (4.43) та врахувавши те, що

![]() ,

,

отримаємо

![]() , (4.44)

, (4.44)

де N2 – кількість імпульсів тактової частоти fТ, які підрахує лічильник СТ протягом стадії лічби.

З отриманого рівняння перетворення витікає, що відмінною особливістю методу багаторазового інтегрування є та обставина, що ні тактова частота fТ, ні постійна інтегрування RC не вливають на результат вимірювання. Необхідно тільки забезпечити стабільність тактової частоти протягом часового інтервалу t1+t2. Дана вимога забезпечується використанням простого тактового генератора, оскільки суттєві часові або температурні дрейфи частоти відбуваються протягом часу, що значно перевищує час АЦП-перетворення.

Із аналізу отриманого рівняння перетворення видно також, що до остаточного результату входять не миттєві значення вимірюваної напруги, а тільки значення, які усереднено за час t1. Тому змінна напруга послаблюється тим сильніше, чим вища її частота.

Визначимо коефіцієнт передачі завади KЗ для АЦП двотактного інтегрування. Припустимо, що на вхід інтегратора надходить гармонічний сигнал одиничної амплітуди, частотою f та з довільною початковою фазою . Середнє значення цього сигналу за час інтегрування t1 дорівнюватиме

.

(4.45)

.

(4.45)

Дана величина досягає максимуму по модулю при = ± k, k = 0, 1, 2, ... . В цьому випадку

Рисунок

4.38![]()

З

(4.46) видно, що змінна напруга, період

якої в цілу кількість разів менше t1,

суттєво зменшується (рис. 4.38). Тому

доцільно вибирати тактову частоту

такою, щоб добуток

![]() був

рівним або кратним періоду промислової

мережі.

був

рівним або кратним періоду промислової

мережі.

Інтегральні АЦП багаторазового інтегрування виготовляють у вигляді напівпровідникових мікросхем, які поділяються на дві основні групи:

- АЦП з паралельним або послідовним інтерфейсом для спряження з мікропроцесорами і організації вимірювальних каналів;

- АЦП з двійково-десятковими лічильниками та дешифраторами для керування семисегментними індикаторами, в тому числі з мультиплексуванням.

Лекція №15

Сигма-дельта АЦП

АЦП багатотактного інтегрування мають ряд недоліків.

1. Нелінійність перехідної статичної характеристики операційного підсилювача, на якому виконують інтегратор, суттєво впливає на інтегральну нелінійність характеристики перетворення АЦП високої розрізнювальної здатності. Для зменшення впливу цього фактора АЦП виконують багатотактним. Наприклад, тринадцятирозрядний AD7550 виконує перетворення за чотири такти.

2. Інтегрування вхідного сигналу займає в циклі перетворення тільки приблизно третю частину. Дві третини циклу перетворювач не приймає вхідний сигнал. Це погіршує завадостійкі властивості інтегрувального АЦП.

3. Схема АЦП багатотактового інтегрування повинна включати досить багато зовнішніх резисторів і конденсаторів з високоякісним діелектриком, що значно збільшує площу, яку займає перетворювач на платі і, як наслідок, підсилює вплив завад.

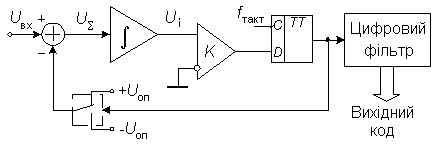

Ці недоліки в переважній більшості усунені в конструкції сигма-дельта АЦП. Своєю назвою ці перетворювачі зобов’язані наявністю в них двох блоків: суматора (позначення операції – ) і інтегратора (позначення операції – ). Один із принципів, закладених в такого роду перетворювачі, що дозволяє зменшити похибку, яка вноситься шумами, і відповідно, збільшити розрізнювальну здатність – це усереднення результатів вимірювання на більшому інтервалі часу. Основні вузли АЦП – це сигма-дельта модулятор і цифровий фільтр. Схема n-розрядного сигма-дельта модулятора першого порядку наведена на рис. 4.39.

Рисунок

4.39

Робота цієї схеми основана на відніманні із вхідного сигналу Uвх(t) величини сигналу на виході ЦАП, що отримана на попередньому такті роботи схеми. Отримана різниця інтегрується, а потім перетворюється в код паралельним АЦП невисокої розрядності. Послідовність кодів надходить на цифровий фільтр нижніх частот.

Порядок модулятора визначається кількістю інтеграторів і суматорів в його схемі. Сигма-дельта модулятори N-го порядку мають N суматорів і N інтеграторів і забезпечують більше співвідношення сигнал/шум при тій же частоті відліків, ніж модулятори першого порядку. Прикладами сигма-дельта модуляторів високого порядку є одноканальний AD7720 сьомого порядку і двоканальний ADMOD79 п’ятого порядку.

Н

Рисунок

4.40

Таблиця 4.3 – Послідовність станів АЦП

|

Uвх = 0,6 В |

Uвх = 0 В | ||||||||

|

N такту |

U, В |

Uі, В |

Uк, біт |

UЦАП, В |

N такту |

U, В |

Uі, В |

Uк, біт |

UЦАП, В |

|

1 |

0,6 |

0,6 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

2 |

-0,4 |

0,2 |

1 |

1 |

2 |

-1 |

0 |

0 |

-1 |

|

3 |

-0,4 |

-0,2 |

0 |

-1 |

3 |

1 |

1 |

1 |

1 |

|

4 |

1,6 |

1,4 |

1 |

1 |

4 |

-1 |

0 |

0 |

-1 |

|

5 |

-0,4 |

1,0 |

1 |

1 |

5 |

1 |

1 |

1 |

1 |

|

6 |

-0,4 |

0,6 |

1 |

1 |

6 |

-1 |

0 |

0 |

-1 |

|

7 |

-0,4 |

0,2 |

1 |

1 |

7 |

1 |

1 |

1 |

1 |

|

8 |

-0,4 |

-0,2 |

0 |

-1 |

8 |

-1 |

0 |

0 |

-1 |

|

9 |

1,6 |

1,4 |

1 |

1 |

9 |

1 |

1 |

1 |

1 |

|

10 |

-0,4 |

1,0 |

1 |

1 |

10 |

-1 |

0 |

0 |

-1 |

|

11 |

-0,4 |

0,6 |

1 |

1 |

11 |

1 |

1 |

1 |

1 |

|

12 |

-0,4 |

0,2 |

1 |

1 |

12 |

-1 |

0 |

0 |

-1 |

|

13 |

-0,4 |

-0,2 |

0 |

-1 |

13 |

1 |

1 |

1 |

1 |

|

14 |

1,6 |

1,4 |

1 |

1 |

14 |

-1 |

0 |

0 |

-1 |

|

15 |

-0,4 |

1,0 |

1 |

1 |

15 |

1 |

1 |

1 |

1 |

|

16 |

-0,4 |

0,6 |

1 |

1 |

16 |

-1 |

0 |

0 |

-1 |

В тактові періоди 2 і 7 стани системи ідентичні, оскільки при незмінному вхідному сигналі Uвх = 0,6 В цикл роботи займає п’ять тактових періодів. Усереднення вихідного сигналу ЦАП за цикл дійсно дає величину напруги 0,6 В:

(1-1+1+1+1)/5=0,6.

Для формування вихідного коду такого перетворювача необхідно якимось чином перетворити послідовність бітів на виході компаратора у вигляді унітарного коду в послідовний або паралельний двійковий код. Це можна зробити за допомогою двійкового лічильника. Візьмемо чотирирозрядний лічильник. Підрахування бітів на виході компаратора за шістнадцятитактний цикл дає число 13. Неважко побачити, що при Uвх = 1 В на виході компаратора завжди буде одиниця, що дає за цикл число 16, тобто переповнення лічильника. Навпаки, при Uвх = -1 В на виході компаратора завжди буде нуль, що дає рівний нулю вміст лічильника в кінці циклу. У випадку, коли Uвх = 0 то, як це видно із табл. 4.2, результат лічби за цикл становитиме 810 або 10002. Це значить, що вихідне число АЦП подається в зміщеному коді. В розглянутому прикладі верхня межа повної шкали становитиме 11112 або +710, а нижня – 00002 або – 810. При Uвх = 0,6 В, як це видно із лівої половини табл. 4.2, вміст лічильника становитиме 1310 в зміщеному коді, що відповідає +5. Враховуючи, що +8 відповідає Uвх = 1 В, знайдемо

5*1/8=0,625 > 0,6 В.

При використанні двійкового лічильника як перетворювача потоку бітів, що надходять з виходу компаратора, необхідно виділити фіксований цикл перетворення, тривалість якого рівна добутку Kрах fтакт. Після його закінчення повинно проводитись зчитування результату, наприклад, за допомогою регістра-засувки і обнулення лічильника. В цьому випадку с точки зору завадопоглинаючих властивостей сигма-дельта АЦП близькі до АЦП багатотактового інтегрування. Більш ефективним, з цієї точки зору, є використання в сигма-дельта АЦП цифрових фільтрів з скінченною тривалістю перехідних процесів.

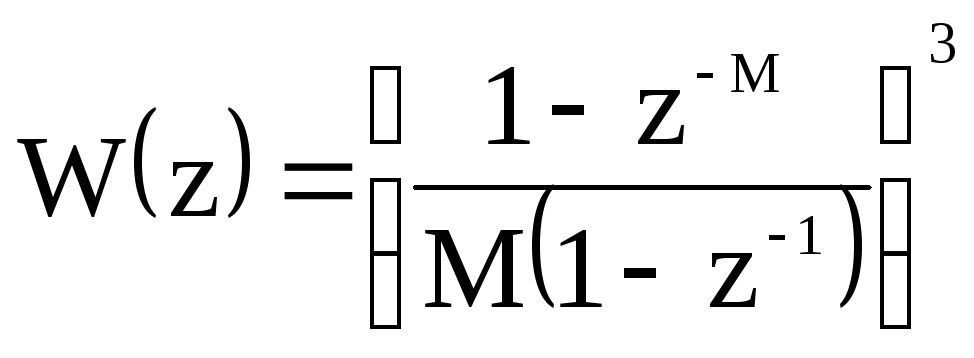

В сигма-дельта АЦП звичайно використовуються цифрові фільтри з амплітудно-частотною характеристикою (АЧХ) виду (sinx/x)3. Передатна функція такого фільтра в z-області визначається за виразом

,

,

де М – ціле число, яке задається програмно і дорівнює відношенню тактової частоти модулятора до частоти відліків фільтра. (Частота відліків – це частота, з якою обновляються дані). Наприклад, для АЦП AD7714 це число може набувати значень від 19 до 4000. В частотній області модуль передатної функції фільтру

. (4.47)

. (4.47)

На рис. 4.41 наведено графік амплітудно-частотної характеристики цифрового фільтра, побудований згідно з виразом (4.47) при fтакт = 38,4 кГц і М = 192, що дає значення частоти відліків, що збігається з першою частотою резекції фільтра АЦП, fвідл=50 Гц. Порівняння цієї АЧХ із АЧХ коефіцієнта поглинання завад АЦП з дворазовим інтегруванням (рис. 4.38) показує значно кращі завадопоглинальні властивості сигма-дельта АЦП.

В

Рисунок

4.41

Лекція №16