- •Опорний конспект лекцій по курсу "аналогові та цифрові вимірювальні прилади" (Частина №1)

- •Магнітоелектричні прилади Магнітоелектричний вимірювальний перетворювач

- •Магнітоелектричні амперметри

- •Магнітоелектричні вольтметри

- •Магнітоелектричні омметри

- •Електромагнітні прилади Електромагнітний вимірювальний перетворювач

- •Електромагнітні амперметри та вольтметри

- •Електродинамічні прилади Електродинамічний вимірювальний перетворювач

- •Амперметри, вольтметри і ватметри електродинамічної системи

- •Феродинамічний вимірювальний перетворювач

- •Електростатичні прилади

- •В момент часу напруга на конденсаторі с досягне такого значення

- •Розглянемо даний алгоритм на прикладі переведення чисел із десяткової в двійкову системи числення.

- •Аналого-цифровим перетворювачем називають засіб вимірювання, в якому створюється кодовий сигнал вимірювальної інформації.

- •Параметри ацп

- •Виділяють такі параметри ацп, що характеризують їхню динамічну точність.

Розглянемо даний алгоритм на прикладі переведення чисел із десяткової в двійкову системи числення.

Для прикладу візьмемо число 4510 і подамо його двійковим кодом, для чого достатньо 6 двійкових розрядів (26 = 64):

25 24 23 22 21 20

32 16 8 4 2 1.

Суть алгоритму полягає в тому, що б із суми ваг двійкових розрядів набрати число 45. Процес починають із старшого розряду.

Запишемо 1 в старший розряд 25 = 32

25 24 23 22 21 20

32 16 8 4 2 1

1

Число 32 45. Тому 1 залишається в старшому розряді. Далі, рухаючись від старшого розряду до молодшого, записуємо одиницю в розряд 24=16

25 24 23 22 21 20

32 16 8 4 2 1

1 1

Отримане число 32+16 45. Тому розряд 24 набуває значення 0, а в розряд 23 записуємо 1.

25 24 23 22 21 20

32 16 8 4 2 1

1 0 1

Оскільки набране число 32 + 0 + 8 = 40 45, то 1 залишається в розряді 23. Далі записуємо 1 в наступний розряд 22

25 24 23 22 21 20

32 16 8 4 2 1

1 0 1 1

і перевіряємо співвідношення між набраною сумою і числом 45. В результаті таких дій отримуємо остаточний результат

25 24 23 22 21 20

32 16 8 4 2 1

1 0 1 1 0 1

32 + 0 + 8 + 4 + 0 + 1 = 45.

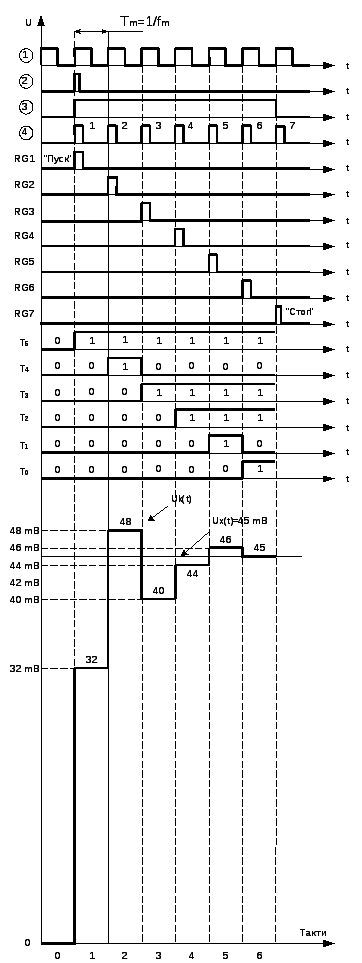

Припустимо, що числа 32, 16, 8, 4, 2, 1 відповідають значенням компенсувальної напруги Uk, а число 45 є значенням вимірюваної напруги UХ. Для цього прикладу процес зрівноваження вимірюваної напруги компенсувальною за алгоритмом порозрядного зрівноваження наведено на рис. 4.33.

Для технічної реалізації цього алгоритму необхідно мати такі компоненти:

- генератор тактових імпульсів;

розподільник імпульсів, який в кожному такті формує один керуючий імпульс в одному розряді, починаючи з старшого;

- регістр, який буде запам’ятовувати двійковий код;

- цифро-аналоговий перетворювач, що перетворює двійковий код в компенсувальну напругу;

- компаратор, який залежно від співвідношення UХ і Uk формує на своєму виході логічні «0» чи «1».

Структурна схема шестирозрядного цифрового вольтметра порозрядного зрівноваження наведена на рис. 4.34.

Рисунок 4.33

Основними елементами цієї схеми є:

- блок пуску, до складу якого входять RS-тригер Т, генератор тактової частоти fm і електронний ключ SW;

- розподільник імпульсів RG зі схемами збігу SW0…SW5;

- шестирозрядний регістр результату, що реалізовано на RS-тригерах Т0...Т5;

- цифро-аналоговий перетворювач ЦАП;

- компаратор, на один із входів якого надходить вимірювана напруга Ux, а на другий компенсувальна – Uk.

Вихідне положення. RS-тригер Т, тригери розподільника імпульсів RG і тригери Т0...Т5 регістра результату знаходяться в стані логічного «0». Рівнем логічного нуля з прямого виходу (точка 3) тригера Т закрита схема SW і імпульси тактової частоти fm не надходять на вхід розподільника імпульсів RG. Тригери регістра результату Т0...Т5 також знаходяться в стані логічного нуля і з їхніх прямих виходів код 00 0000 надходить на цифрові входи цифро-аналогового перетворювача ЦАП (такт 0 в табл. 4.2).

Рисунок 4.34

Цей код (00 0000) в ЦАП перетворюється в нульове значення компенсувальної напруги Uk = 0 В, яка надходить на другий вхід компаратора. Оскільки на першому вході компаратора присутня вимірювана напруга UX = 45 мВ, то на виході компаратора сформовано рівень логічного нуля (Uk < UX). Цим логічним сигналом закриті схеми збігу SW0…SW5. В цьому положенні схема знаходиться до тих пір, поки не з’явиться сигнал «Пуск» на S-вході тригера Т.

Таблиця 4.2 – Такти роботи

|

Такт |

Стан тригерів |

Компенсувальна напруга, мB |

Співвідношення напруг Uk і Ux |

Стан компаратора | |||||

|

T5 |

T4 |

T3 |

T2 |

T1 |

T0 | ||||

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 < 45 |

“0” |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

32 |

32 < 45 |

“0” |

|

2 |

1 |

1 |

0 |

0 |

0 |

0 |

48 |

48 > 45 |

“1” |

|

3 |

1 |

0 |

1 |

0 |

0 |

0 |

40 |

40 < 45 |

“0” |

|

4 |

1 |

0 |

1 |

1 |

0 |

0 |

44 |

44 < 45 |

“0” |

|

5 |

1 |

0 |

1 |

1 |

1 |

0 |

46 |

46 > 45 |

“1” |

|

6 |

1 |

0 |

1 |

1 |

0 |

1 |

45 |

45 = 45 |

“0” |

Лекція №14

Принцип дії ілюструється часовими діаграмами, що наведені на рис. 4.35. Одиничним рівнем сигналу «Пуск», що подано на S-вхід тригера Т (точка 2), на його прямому виході формується одиничний логічний рівень (точка 3). Даний рівень логічного сигналу відкриває раніше закриту схему SW, через яку тактові імпульси з частотою fm надходять на вхід розподільника імпульсів RG.

Розглянемо подальшу роботу даного засобу вимірювання по тактах.

Такт 1. Першим імпульсом тактової частоти fm на першому виході розподільника імпульсів RG1 формується прямокутний керуючий імпульс, який по S-входу встановлює тригер Т5 в одиничний стан і на виходах тригерів Т5...Т0 формується двійковий код 10 0000 (такт 1, табл. 4.1). Ці логічні сигнали в паралельному коді надходять на входи ЦАП, на виході якого формується компенсувальна напруга 32 мВ. Оскільки на входах компаратора Ux = 45 мВ Uk = 32 мВ, то на його виході залишається рівень логічного нуля, яким закриті всі схеми збігу SW0…SW5.

Такт 2. Наступним імпульсом тактової частоти на другому виході розподільника імпульсів RG2 формується керуючий сигнал, який по S-входу встановлює тригер Т4 в стан логічної “1”. В зв’язку з тим, що схеми збігу SW0…SW5 закриті логічним “0” з виходу компаратора, то керуючий сигнал з другого виходу RG не проходить на R-вхід тригера Т5 і він залишається в стані логічної “1”. Тому на виходах тригерів Т5...Т0 формується двійковий код 11 0000 (такт 2, табл. 4.1). Цей паралельний двійковий код надходить на входи ЦАП, який тут перетворюється в компенсувальну напругу 48 мВ. Компенсувальна напруга перевищила вимірювану Uk Uх, на виході компаратора встановлюється рівень логічної “1”, яким відкриваються раніше закриті схеми збігу SW0…SW5.

Такт 3. Третім імпульсом тактової частоти на третьому виході RG3 розподільника імпульсів формується сигнал, який по S-входу встановлює тригер Т3 в стан логічної “1” і через відкриту схему збігу SW4 обнуляє по R-входу тригер Т4. В результаті цих дій на виходах тригерів формується двійковий код 10 1000 (такт 3, табл. 4.1), який ЦАП перетворює в компенсувальну напругу 40 мВ. Uk = 40 мВ Uх = 45 мВ, на виході компаратора встановлюється логічний “0”, що закриває всі схеми збігу SW0…SW5.

Такт 4. Четвертим імпульсом fm на четвертому виході RG4 формується керуючий сигнал, який по S-входу встановлює на виході тригера Т2 рівень логічної “1”. В зв’язку з тим, що всі схеми збігу закриті, то даний керуючий сигнал не проходить на R-вхід тригера Т3.

Рисунок 4.35

Він залишається в стані логічної “1”. На виходах тригерів формується двійковий код 10 1100 (такт 4, табл. 4.1), який ЦАП перетворюється в компенсувальну напругу 44 мВ. Оскільки Uk = 44 мВ Uх = 45 мВ, на виході компаратора залишається раніше встановлений рівень логічного “0”. Всі схеми збігу SW0…SW5 закриті.

Такт 5. П’ятим імпульсом fm на п’ятому виході RG5 формується керувальний сигнал, який по S-входу встановлює на виході тригера Т1 рівень логічної “1”. Тригер також залишається в одиничному стані. Тому на виходах тригерів в цьому такті сформувався такий двійковий код 10 1110 (такт 5, табл. 4.1). Цьому двійковому коду відповідає значення компенсувальної напруги 46 мВ. В даному такті Uk Uх. На виході компаратора формується логічна “1”, яка відкриває раніше закриті схеми збігу.

Такт 6. Шостим імпульсом fm на шостому виході RG6 формується керуючий сигнал, який по S-входу встановлює на виході тригера Т0 рівень логічної “1”, а тригер Т1 в стан логічного “0”. Вихідний код тригерів Т5...Т0 такий (10 1101), якому відповідає значення компенсувальної напруги Uk = 45 мВ, а співідношення між Uх і Uk рівню логічного “0” на виході компаратора. Процес вимірювання (зрівноваження) завершено.

Аналого-цифрові перетворювачі