- •3. Функциональные устройства

- •3.1. Арифметическо-логическое устройство

- •3.1.1. Алу с жесткой структурой

- •3.1.2. Алу с гибкой структурой

- •Устройство управления (уу)

- •3.2.1. Структура команды

- •3.4. Блок формирования управляющих сигналов

- •3.4.1. Блок формирования управляющих сигналов с жесткой структурой

- •3.4.2. Пример построения фрагмента бфус с жесткой структурой для операции «сравнение модулей двух чисел»

- •3.4.3. Блок формирования управляющих сигналов

- •3.4.4. Разработка микропрограммы на примере операции “деление в прямых кодах”

- •0 Такт (тактов должно быть столько же, сколько разрядов)

- •3.5. Запоминающие устройства

- •3.5.1. Оперативные запоминающие устройства

- •3.6. Полупроводниковые запоминающие устройства

- •3.6.1. Ассоциативные запоминающие устройства (азу)

- •Контрольные вопросы

- •4. МикропроцессоРные устройства

- •4.1. Микропроцессорный комплект кр580

- •4.2. Организация управления в микропроцессорной системе

- •4.3. Интерфейсные бис в составе мп – комплекта кр580

- •Системный контроллер кр580вк28. Системный контроллер предназначен для:

- •4.3.2 Программируемый контроллер ввода-вывода кр580вв55

- •4.3.2.1. Формат рус (регистра управляющего слова):

- •4.4. Однокристальные микро эвм серии кр1816

- •4.4.1. Организация памяти программ

- •4.4.2. Организация памяти данных

- •4.4.3. Таймер-счетчик

- •4.4.4. Организация ввода/вывода в контроллере

- •4.4.5. Устройство управления и синхронизации

- •4.4.6. Формирование синхроимпульсов и управляющих сигналов

- •4.4.7. Подключение к микроконтроллеру внешнего устройства

- •4.5. Программируемый таймер км580вм53

- •4.5.1.Режимы работы программируемого таймера.

- •4.5.2. Пример программирования таймера

- •Функционирование мп - системы в режиме прерывания

- •4.6.1. Программируемый контроллер прерываний кр580вн59

- •Функционирование мп – системы в режиме пдп (прямого доступа к памяти)

- •Основные принципы организации режима пдп :

- •Контроллер пдп к580вт57

- •Микропроцессорный комплект км1810

- •Микропроцессор км 1810 вм86

- •На рис. 4.38 представлена структура оперативной памяти, в конструкции которой имеются некоторые особенности .

- •Методы адресации данных

- •Пример кодирования команды

- •Управление и синхронизация в мп- системе

- •Организация управления в многопроцессорной системе

- •Микропроцессоры Intel386 иIntel486

- •Виртуальная память

- •Кэш-память

- •Семейство процессоров Pentium

- •Архитектурные особенности современных мп

- •Основные архитектуры системы команд

- •Основные структуры современных процессоров

- •Контрольные вопросы

- •ЛИтература

3.4. Блок формирования управляющих сигналов

Существуют 2 основные структуры БФУС:

жесткая;

микропрограммная.

3.4.1. Блок формирования управляющих сигналов с жесткой структурой

Отличается тем, что формирование последовательностей управляющих сигналов осуществляется с помощью логических схем.

На рис. 3.7 представлена упрощенная функциональная схема БФУС с жесткой структурой. Основными ФУ являются двоичный счетчик тактов, дешифратор тактов (ДС), триггер управления (ТУ), формирователь управляющих сигналов (УС).

Рис. 3.7. Функциональная схема БФУС с жесткой структурой

На рис.3.7 представлена упрощенная функциональная схема БФУС, в состав которой входят следующие функциональные узлы (ФУ) и логические схемы (ЛС):

ГСИ – генератор синхроимпульсов;

СТ2 тактов - двоичный счетчик, который подсчитывает количество тактов (импульсов), прошедших за время выполнения данной вычислительной или логической операции;

ТУ- триггер управления, который управляет логической схемой (ЛС) на входе счетчика;

ДС тактов - дешифратор, на выходах которого образуется стандартная последовательность управляющих потенциалов (УП), распределенных во времени (по номерам тактов) и в пространстве (по номерам контактов на выходе дешифратора). На рис. 3.8 изображен управляющий потенциал в третьем такте [УП3].

ДС КОП – дешифратор кода операции определяет, какая команда будет выполняться.

Рис. 3.8. Временная диаграмма стандартных сигналов БФУС

РИ – распределитель импульсов, который распределяет синхроимпульсы в пространстве и времени, например, управляющий импульс УИ3 появится на выходе №3 в третьем такте (рис. 3.8).

При включении ЭВМ, или после окончания выполнения очередной команды ТУ:=0 и СТ2:=0.

Если на вход подается сигнал Н.ОП (начало операции) или ПУСК, то ТУ устанавливается в 1, и на счетчик тактов поступают импульсы. При этом, как было показано выше, формируются две стандартных последовательности:

-управляющие потенциалы УП(1:m);

- управляющие импульсы УИ(1:m);

где m - количество тактов, необходимых для выполнения данной операции (команды).

Далее УП(1:m) и УИ(1:m) поступают на формирователь управляющих сигналов (Форм. УС), на выходе которого образуется нужная последовательность УС, реализующая данную операцию на ЭВМ.

Для каждой команды в составе формирователя УС существует своя ЛС для формирования соответствующей последовательности управляющих УС.

Основные этапы проектирования БФУС жесткого типа:

содержательное рассмотрение задачи, т.е. математическая постановка, числовые примеры;

построение обобщенной схемы алгоритма;

разработка структуры АЛУ и списка микроопераций с соответствующими характеристиками;

составление кодированной схемы алгоритма, привязанной к разработанной структуре АЛУ;

построение временной диаграммы управляющих сигналов;

разработка логической схемы БФУС.

3.4.2. Пример построения фрагмента бфус с жесткой структурой для операции «сравнение модулей двух чисел»

Математическая постановка данной операции представлена последовательностью (3.5)

![]() .

Если

.

Если

![]() ,

то │S│=│A│

(3.5)

,

то │S│=│A│

(3.5)

Если

![]() ,

то │S│=

│B│

,

то │S│=

│B│

Вычитание выполняется по алгоритму ПД.

![]()

![]()

![]() .

.

В

результате вычитания может образоваться

перенос из старшего разряда сумматора:

если

![]() ,

то

,

то![]() ,

,![]() ;

;

если

![]() ,

то

,

то![]() ,

,![]() .

.

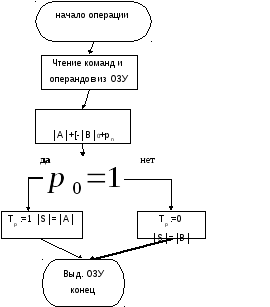

На основе математической постановки задачи составлена, так называемая, обобщенная схема алгоритма для операции «сравнение модулей двух чисел»(рис. 3.9). Это означает, что данный алгоритм может быть реализован на любой структуре АЛУ.

Рис. 3.9. Обобщенная схема алгоритма

Соответствующий фрагмент АЛУ представлен на рис. 3.10. Он состоит из трех регистров, сумматора параллельного действия, триггера и нескольких ЛС.

В РГ1 на вход «Д» поступает из ОЗУ первый операнд «А» (ОП1[0:n]), который будет принят в регистр микрооперацией «ПР РГ1». Соответственно в РГ2 микрооперацией «ПР РГ2» будет принят второй операнд «В» (ОП[0:n]).

Далее микрооперацией «ВЫД SM» на входы сумматора подаются │A│ в прямом коде и │B│ в обратном коде. Кроме того, на третий вход сумматора поступает микрооперация «перенос в младший разряд»- pn .

После этого на выходе сумматора образуются сумма (на рис. 3.8 не обозначена) и перенос из старшего разряда сумматора – p0.

Затем микрооперацией «контр р0» значение переноса «p0» принимается в триггер переноса Тр, находящий в БФУС.

Принимаем, что строим АЛУ параллельного действия с непосредственными связями.

Рис.3.10. Фрагмент АЛУ

Значение Тр является логическим признаком (флагом), который поступает снова в АЛУ и определит передачу в РГ3 либо РГ1[1:n] т.е.│S│=│A│, либо РГ2[1: n ], т.е │S│= │B│.

Момент приема в РГ3 значений │S│ определяется микрооперацией «ПРРГ3». Затем микрооперацией «ВЫД ОЗУ» вычисленное значение │S│ посылается в оперативную память.

Строим кодированную схему алгоритма (рис.3.11), “привязанную” к фрагменту АЛУ на рис. 3.10. Эта схема алгоритма содержит последовательность микроопераций (МО), которые необходимо подать на АЛУ, чтобы выполнить заданную команду.

Напоминаем, что в действительности каждая МО выполняется соответствующим физическим УС.

Рис. 3.11. Кодированная схема алгоритма

Построим ЛС в составе БФУС, которая обеспечит формирование последовательности УС для выполнения рассматриваемой операции.

Принимаем, что у нас одноадресная структура команды.

Тогда получается, что операция «сравнение модулей» реализуется с помощью двух одноадресных команд (табл. 3.5).

Таблица 3.5

|

Чтение А |

A à РГ1 |

|

Сравн. мод. В |

|

Считаем, что операция «вычитание» выполняется по алгоритму ПД. После выполнения 1-й команды операнд «А» уже находится в РГ1 в прямом коде. Составляем фрагмент схемы БФУС для 2-й команды - «сравнение с модулем В».

В таблице 3.6 представлен соответствующий перечень микроопераций с их характеристиками. В 4-й графе таблицы указана длительность микрооперации в тактах, В 5-ой графе приведен номер такта, с которого начинается МО.

Принято, что чтение из ОЗУ происходит за 3 такта.

Микрооперации

«Выдача SM»

и «![]() »

являются потенциальными УС, и их

длительность определяется временем

суммирования. Пусть

»

являются потенциальными УС, и их

длительность определяется временем

суммирования. Пусть![]() такта.

такта.

Таблица 3.6

|

№ МО |

Наименование |

Вид МО |

Длит. (такт) |

№ такта |

Куда направл. | |

|

МО1 |

Чтение ОЗУ |

импульс. |

1 |

1-й |

в ОЗУ | |

|

МО2 |

Чтение ОЗУ |

импульс. |

1 |

4-й |

в ОЗУ | |

|

МО3 |

Прием в РГ2 |

импульс. |

1 |

6-й |

в АЛУ | |

|

МО4 |

Выдача

SM,

|

потенц. |

4 |

7÷10-й |

в АЛУ | |

|

МО5 |

Контроль p0 |

импульс. |

1 |

11-й |

в АЛУ | |

|

МО6 |

Прием РГ3 |

импульс. |

1 |

12-й |

в АЛУ | |

|

МО7 |

Выдача ОЗУ |

импульс. |

1 |

13-й |

в АЛУ | |

|

МО8 |

Конец операции |

импульс. |

1 |

14-й |

в УУ | |

На рис. 3.12 представлен фрагмент логической схемы, которая формирует последовательность УС для реализации операции «сравнение модулей».

Рис. 3.12. Фрагмент БФУС c жесткой структурой

Принцип построения ЛС достаточно прост и основан на характеристиках микроопераций, представленных табл. 3.6.

Например, МО2 относится к импульсному виду, длительность 1 такт, начинается с 4-го такта и существует, когда выполняется операция «ср. мод».

Тогда ее формирование описывается следующим логическим выражением:

МО2:= «ср. мод» & УИ4,

МО4 - потенциальная переменная, существует в тактах (7-11):

МО4:= «ср. мод» & УП7 V УП8 V УП9 V УП10 V УП11.

Логические выражения для остальных МО можно составить самостоятельно. Сформированная таким образом последовательность УС поступает на фрагмент АЛУ (рис.3.8) и обеспечивает выполнение микроопераций МО1-МО7.

Результат операции сравнения соответствует состоянию триггера Тр. Если Тр:=1, то │S│:=РГ1 , если Тр:=0, то │S│:=РГ2.