- •3. Функциональные устройства

- •3.1. Арифметическо-логическое устройство

- •3.1.1. Алу с жесткой структурой

- •3.1.2. Алу с гибкой структурой

- •Устройство управления (уу)

- •3.2.1. Структура команды

- •3.4. Блок формирования управляющих сигналов

- •3.4.1. Блок формирования управляющих сигналов с жесткой структурой

- •3.4.2. Пример построения фрагмента бфус с жесткой структурой для операции «сравнение модулей двух чисел»

- •3.4.3. Блок формирования управляющих сигналов

- •3.4.4. Разработка микропрограммы на примере операции “деление в прямых кодах”

- •0 Такт (тактов должно быть столько же, сколько разрядов)

- •3.5. Запоминающие устройства

- •3.5.1. Оперативные запоминающие устройства

- •3.6. Полупроводниковые запоминающие устройства

- •3.6.1. Ассоциативные запоминающие устройства (азу)

- •Контрольные вопросы

- •4. МикропроцессоРные устройства

- •4.1. Микропроцессорный комплект кр580

- •4.2. Организация управления в микропроцессорной системе

- •4.3. Интерфейсные бис в составе мп – комплекта кр580

- •Системный контроллер кр580вк28. Системный контроллер предназначен для:

- •4.3.2 Программируемый контроллер ввода-вывода кр580вв55

- •4.3.2.1. Формат рус (регистра управляющего слова):

- •4.4. Однокристальные микро эвм серии кр1816

- •4.4.1. Организация памяти программ

- •4.4.2. Организация памяти данных

- •4.4.3. Таймер-счетчик

- •4.4.4. Организация ввода/вывода в контроллере

- •4.4.5. Устройство управления и синхронизации

- •4.4.6. Формирование синхроимпульсов и управляющих сигналов

- •4.4.7. Подключение к микроконтроллеру внешнего устройства

- •4.5. Программируемый таймер км580вм53

- •4.5.1.Режимы работы программируемого таймера.

- •4.5.2. Пример программирования таймера

- •Функционирование мп - системы в режиме прерывания

- •4.6.1. Программируемый контроллер прерываний кр580вн59

- •Функционирование мп – системы в режиме пдп (прямого доступа к памяти)

- •Основные принципы организации режима пдп :

- •Контроллер пдп к580вт57

- •Микропроцессорный комплект км1810

- •Микропроцессор км 1810 вм86

- •На рис. 4.38 представлена структура оперативной памяти, в конструкции которой имеются некоторые особенности .

- •Методы адресации данных

- •Пример кодирования команды

- •Управление и синхронизация в мп- системе

- •Организация управления в многопроцессорной системе

- •Микропроцессоры Intel386 иIntel486

- •Виртуальная память

- •Кэш-память

- •Семейство процессоров Pentium

- •Архитектурные особенности современных мп

- •Основные архитектуры системы команд

- •Основные структуры современных процессоров

- •Контрольные вопросы

- •ЛИтература

Организация управления в многопроцессорной системе

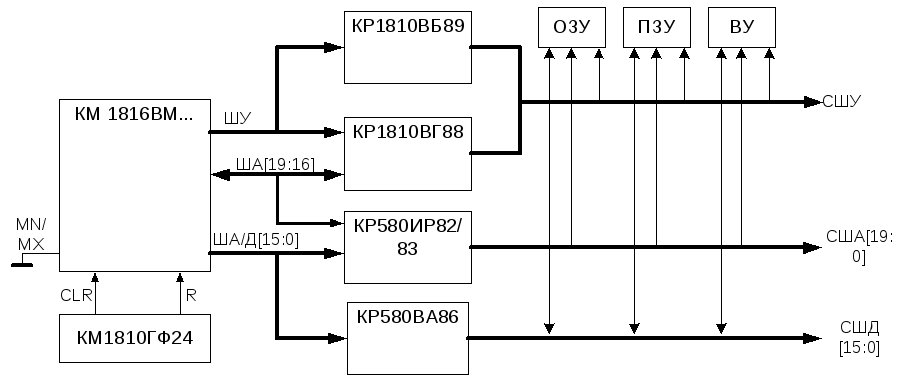

Рис .4 .46. Структура многопроцессорной системы на базе 1810 в режиме максимального включения

На рис. 4.46 изображена типовая структура многопроцессорной системы, состоящая из следующих микросхем (интерфейсных плат):

КР1810ВБ89 – арбитр системных шин, который в т.ч. содержит значения приоритетов микропроцессоров, входящих в состав МПС. В зависимости от запросов и приоритетов предоставляются системные шины тому или иному МП.

КР1810ВГ88 – системный контроллер, который в зависимости от типа машинного цикла формирует ряд управляющих сигналов, поступающих на системную шину управления.

КР580ИР82/83 – буферные регистры, которые хранят коды системной шины адреса (США) и повышают нагрузочную способность шины.

КР580ВА86 – буферная двунаправленная схема, которая формирует системную шину данных (СШД) и повышает нагрузочную способность шины.

Управление в многопроцессорной системе является двух-уровневым, как в МП КР580. В табл.4.12 представлены типы машинных циклов.

Таблица 4.12

|

SA[2:0] |

Тип машинного цикла |

|

000 001 010 100 101 110 |

подтверждение прерывания считывание из ВУ записать во ВУ считывание команд чтение из ОЗУ запись в ОЗУ |

Микропроцессоры Intel386 иIntel486

Это первые 32-х разрядные МП. Они имеют практически одинаковую структуру, но i486 выполнен на СБИС большей степени интеграции и имеет большую производительность.

Основные характеристики:

32-разрядная шина адреса и данных

Тактовая частота 386- 12-40 МНz; 486- 25-120 MHz

Введена виртуальная память с сегментной и страничной организацией

Введен конвейерный режим обработки команд

Введена кэш-память (только в 486)

Сохранилась совместимость с программным обеспечением для более ранних моделей МП (580, 1810, 80286).

На рис. 4.47 представлена структурная схема МП 486.

Рис. 4.47 Структурная схема МП 486

Как и в МП 1810, в структуре выделены две части: устройство обработки (УО) и устройство связи с каналом (УСК).

В целях повышения производительности МП может выполнять обработку текущей команды, а также выбирать новые блоки команд и данных одновременно.

Умн/дел – специальные логические схемы реализуют функции умножения и деления.

Конвейерное выполнение команд – за счет введения дополнительных аппаратных средств. Идея построения конвейера команд состоит в том, что в процессе выполнения каждой команды выделяются некоторые единые (общие) процедуры, для выполнения которых, создаются специальные аппаратные средства в таком количестве, чтобы обеспечить одновременное выполнение 5-6 команд. Допустим, что процесс выполнения одной команды состоит из следующих равных по времени этапов - Тэт

Таблица 4.13

-

Э1

К1

К2

К3

К4

К5

К6

Э2

К1

К2

К3

К4

К5

Э3

К1

К2

К3

К4

Э4

К1

К2

К3

Э5

К1

К2

Э6

К1

Э1 – ДС КОП,

Э2 – вычисление FA операнда

Э3 – выборка операнда

Э4 – выполнение арифметических операций

Э5-вычисление FA результата

Э6-запись результата в ОЗУ

В табл.4.13 схематично представлен процесс конвейерного выполнения команд (К1-К5) с этапами (Э1-Э6).

Одна команда выполняется за Тэт х 6= 6 Тэт

Обычный способ – 6 Тэт х 5 = 30 Тэт

Конвейерный способ: Твып кол = 10 Тэ .

Как следует из этого примера, суммарное время выполнения 5 команд сокращается в 3 раза.

Имеется очередь команд – регистр сдвига, в котором в то время, когда устройство обработки выполняет вычисления, устройство связи с каналом выбирает очередной блок команд из программы.

Основные функции устройства связи с каналом

Обслуживание очереди команд.

Вычисление физических адресов данных и команд при сегментной организации и страничной организации памяти.

Организация связи между внутренними и внешними магистралями (шинами).

Управление кэш-памятью.