- •Министерство образования и науки российской федерации

- •4.2. Центральный процессор.

- •4.2.1. Операционный блок.

- •4.2.2. Микропрограммное устройство управления.

- •4.3. Основная память.

- •4.4. Кэш команд и данных. Преобразователь виртуальных адресов.

- •4.5. Система прерывания программ.

- •4.7. Блок синхронизации.

- •4.8. Таймер.

- •4.9. Периферийные устройства.

- •4.9.1. Клавиатура.

- •4.9.2. Монитор.

- •4. Разработка функциональной схемы взаимодействия основного процессорного элемента и процессорного элемента плавающей точки

- •6. Заключение.

- •7. Список использованных источников.

- •Приложение 1. Структурная схема центрального процессора.

4.9.2. Монитор.

Выходные данные компьютера могут быть представлены в самой разной форме – в виде текста, графики, звука и т.д. Наиболее распространенным и удобным устройством вывода является дисплей (монитор), служащий для визуального представления выходных данных компьютера. Монитор является пассивным и в большинстве случаев аналоговым устройством. Коммутация с системой происходит по средствам видеоадаптера (видеокарты).

На ранних стадиях развития ЭВМ всю работу по подготовке изображения, выводимого на монитор, выполнял ЦП, что существенно снижало коэффициент полезной работы. Со временем требование к качеству изображения, и частоте его обновления необратимо росло, в результате чего ЦП уже не мог справляться с поставленной задачей в одиночку. На помощь ему пришел видео-акселератор, взявший на себя часть работы ЦП (в основном обработку 3D-графики). Следующим шагом стало полное освобождение ЦП от функций формирования изображения, за счет использования видеокарт.

В наше время видеокарта выполняет две основные функции – формирования битовых полей (изображений выводимых на монитор), построение которого происходит по специальным алгоритмам, и преобразование цифрового сигнала в аналоговый, для отображения на мониторе. Видеокарта исполняется в виде отдельной БИС, в состав которой входит видеопроцессор, формирующий битовые поля, быстродействующая оперативная память для вычислений и хранения сформированных изображений и ЦАП, преобразующий цифровое представление в аналоговый сигнал. Помимо аналогового выхода современные видеокарты имеют и цифровой, предназначенный для подключения TFTили плазменных мониторов.

Связь видеокарты с ЦП осуществляется по средствам системной шины. Центральный процессор лишь передает видеокарте базовую информацию, на основе которой она самостоятельно строит готовые изображения и выводит их на монитор.

4. Разработка функциональной схемы взаимодействия основного процессорного элемента и процессорного элемента плавающей точки

Am29С332 (ОПЭ), представляет собой нерасширяемый 32-разрядный центральный процессорный модуль. Поддерживает 80-90 н.с. микроцикл для 32 разрядных устройств. Имеет два входных и один выходной порты данных. Обладает встроенным контролем четности данных. Поддерживает 1-, 2-, 3- и 4-байтовые форматы данных для всех операций и битовые поля переменной длинны для логических операций. Оснащен встроенными схемными средствами выполнения многотактовых операций.

Am29C325 (ПЭПТ), представляет собой нерасширяемый 32-разрядный процессорный модуль для осуществления операций над числами с плавающей точкой. Поддерживает 110-120 н.с. микроцикл для 32-разрядных устройств. Имеет два входных и один выходной порты данных. На выходе формирует дополнительные разряды контроля паритета данных, что обеспечивает совместимость с основным процессорным элементом. Поддерживает операции длинного и короткого сложения и вычитания с нормализацией чисел с плавающей точкой и без неё, короткое умножение. Оснащен встроенными схемными средствами выполнения многотактовых операций.

Регистровый файл отделен от обоих ПЭ и выполнен в виде автономного прибора — Am29С334.

Возможны два варианта организации работы сопроцессора. В первом случае ОПЭ и сопроцессор работают по очереди, выполняя каждый команды из своего набора, во втором случае сопроцессор и основной процессорный элемент работают параллельно. В таком случае существенно увеличиваются аппаратные затраты. Для сопроцессора необходимо собственное устройство управления и регистровый файл. Могут возникнуть задержки в вычислениях, если ОПЭ будет работать с результатом, получаемым с сопроцессора. Ещё один недостаток: Am29C325 работает в полтора раза медленнее, чемAm29С332. В результате будет очень сложно синхронизировать их работу. В практике, достаточно малую долю, от общего числа операций, занимают операции с плавающей точкой.

Поэтому приемлемым является первый вариант взаимодействия ОПЭ с ПЭПТ (Приложение 1). В этом случае достаточно одного, общего, устройства управления, которое, в зависимости от типа операции, приостанавливает один из процессорных элементов. Достаточно присутствие одного регистрового файла. Также становиться возможным использование общего регистра данных.

Так как сопроцессор работает медленнее, необходимо существование дополнительной частоты тактирования. Приемлемым будет, если второй сигнал тактирования будет иметь вдвое больший интервал, чем основной. Тогда простой основного ПЭ будет составлять ровно два микроцикла, что обеспечивает синхронизацию работы процессорных элементов.

Вывод данных из процессорных элементов производиться на локальную шину FB. С которой данные поступают на вход буфера и регистра данных. Буфер предоставляет возможность удержания данных, если они не предназначены для записи в регистровый файл. Из буфера данные поступают на локальную шину данныхEB, откуда они поступают на один из портов регистрового файла. Следует отметить, что адрес является 32-разрядным, а данные 36-разрядными (4-разряда контроль четности). Поэтому 4-разряда четности в КЭШ не передаются. Все внутренние шины 36-разрядные.

Флаги, генерируемые процессорными элементами, поступают на вход «Т» тестирования внешних условий секвенсера микрокоманд.

На процессорные элементы данные поступают из соответствующих трактов регистрового файла. Процессорный элемент плавающей точки не осуществляет контроль паритета (он только формирует контрольные биты на выходе), поэтому дополнительные четыре разряда контроля четности отбрасываются. Данные загружает активный в данный момент ПЭ. Видно, что конфликты не обнаруживаются.

Информация относительно типа операции должна содержаться в коде операции команды.

Управление процессорными элементами производиться микропрограммой. Из микрокоманды поступают соответствующие биты на входы управления ПЭ. Также микрокомандой, в зависимости от типа операции, производиться приостановка одного из процессорных элементов (подача сигнала высокого уровня на вход «HOLD»,not_OE), запрещение/разрешение вывода данных регистрам адреса и данных, и буферу. Микропрограмма управляет работой адресного регистра, разрешает/запрещает запись в таблицу страниц. Также разрешает/запрещает преобразование виртуальных адресов в физические. Данная опция необходима, в случае, когда происходит обращение к периферийному устройству по полученному вектору прерывания. Потому что, после сложения вектора значения прерываний с содержимым базового регистра, получается физический адрес устройства.

В данной реализации было решено использовать операции с плавающей запятой в формате IEEEс одинарной точностью (32 бита). В зависимости от управляющих битов, поступающих из МУУ, выбирается тип операции, в каком виде (целочисленном или плавающей точки) представлены операнды, какой тип округления использовать в случае, если выполняются операции с числами с плавающей точкой.

Число с плавающей запятой состоит из:

Мантиссы (выражающей значение числа без учёта порядка);

Знака мантиссы (указывающего на отрицательность или положительность числа);

3) Порядка (выражающего степень основания числа, на которое умножается мантисса);

4) Знака порядка.

Опишем 32 битный формат IEEE 754:

Число может быть + или - . Поэтому отводится 1 бит для обозначения знака числа: 0-положительное, 1-отрицательное. Этот самый старший бит в 32 битной последовательности.

Далее пойдут биты экспоненты, для этого выделяют 1 байт (8 бит).Экспонента может быть, как и число, со знаком + или -. Для определения знака экспоненты, чтобы не вводить ещё один бит знака, добавляют смещение к экспоненте в половину байта +127(0111 1111). То есть, если наша экспоната = +7 (+111 в двоичной), то смещенная экспонента = 7+127=134. А если бы, наша экспонента была -7 , то смещенная экспонета=127-7 =120. Смещенную экспоненту записывают в отведенные 8 бит. При этом, когда нам будет нужно получить экспоненту двоичного числа, мы просто отнимем 127 от этого байта.

Оставшиеся 23 бита отводят для мантиссы. Но, у нормализованной двоичной мантиссы первый бит всегда равен 1, так как число лежит в диапазоне 1<=M<2. Нет смысла, записывать единицу в отведенные 23 бита, поэтому в отведенные 23 бита записывают остаток от мантиссы.

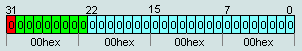

На Рис. 4представлен 32-х битный формат IEEE754.

Рис. 4 – Формат числа с плавающей точкой одинарной точности по стандарту IEEE754

Например, рассмотрим число 155,625. В нормализованном виде: 1.55625*Е+2. Тогда: sign1,biasedexponent1000 0110,fraction001 1011 1010 0000 0000 0000.

В результате десятичное число 155,625 представленное в IEEE 754 c одинарной точностью равно 431BA000 (hex).

Десятичных чисел с плавающей запятой бесконечное множество. Чисел представленных в формате одинарной точности всего 4 294 967 295. Отразить бесконечное множество на конечное без округления не возможно. Поэтому стандарт IEEE754 не может точно представлять все числа. Точность представления числа падает с увеличением его экспоненты.

При представлении чисел с плавающей запятой в стандарт IEEE754 приходится часто округлять числа. Стандарт предусматривает четыре способа округления чисел. Способы округления чисел по стандартуIEEE754:

Округление стремящееся к ближайшему целому.

Округление стремящееся к нулю.

Округление стремящееся к +∞.

Округление стремящееся к -∞.

Исключительные числа стандарта IEEE 754.Из-за невозможности представить 0, ∞ ввели специальные исключения.

число 00 00 00 00 hex считается числом +0

число 80 00 00 00 hex считается числом -0

число 7F 80 00 00hex считается числом +∞

число FF 80 00 00hex считается числом -∞

числа FF (1xxx)X XX XXhex не считается числами (NAN), кроме случая п.3, 4.

числа 7F (1xxx)X XX XXhex не считается числами (NAN), кроме случая п.3,4. Число представленное в битах с 0...22 могут быть любым числом кроме 0 (т.е.+∞ и -∞ ).