- •Министерство образования и науки российской федерации

- •4.2. Центральный процессор.

- •4.2.1. Операционный блок.

- •4.2.2. Микропрограммное устройство управления.

- •4.3. Основная память.

- •4.4. Кэш команд и данных. Преобразователь виртуальных адресов.

- •4.5. Система прерывания программ.

- •4.7. Блок синхронизации.

- •4.8. Таймер.

- •4.9. Периферийные устройства.

- •4.9.1. Клавиатура.

- •4.9.2. Монитор.

- •4. Разработка функциональной схемы взаимодействия основного процессорного элемента и процессорного элемента плавающей точки

- •6. Заключение.

- •7. Список использованных источников.

- •Приложение 1. Структурная схема центрального процессора.

4.2. Центральный процессор.

Центральный процессор предназначен для обработки данных, выполнения вычислений с различными типами данных (целые числа, числа с плавающей точкой, адреса), формирования физического адреса и.т.д. Это все требует значительного времени. Поэтому при разработке необходимо ориентироваться прежде всего на увеличение быстродействия проектируемой ЭВМ. На данном этапе проектирования это возможно путем введения конвейерной обработки исполняемых команд.

При разработке процессора будем опираться на семейство СБИС Am29300, в которое входят следующие микросхемы, необходимые согласно варианту:

Аm29С332 - арифметико-логическое устройство;

Am29С331 - cеквенсор микрокоманд;

Am29С325 – сопроцессор плавающей точки.

Было взято именно это семейство, поскольку микросхемы являются 32-разрядными.

Характерной особенностью архитектуры проектируемой ЭВМ является наличие конвейерной обработки как на уровне команд, так и на уровне микрокоманд. Это достигается тем, что после микропрограммной памяти находится конвейерный регистр микрокоманд. Таким образом, в цикле исполнения i-той микрокоманды можно смело читать из микропрограммной памяти (i+1)-ую, которая будет сохранена в регистре микрокоманд и исполнена в (i+1)-цикле.

МУУ

ОБ

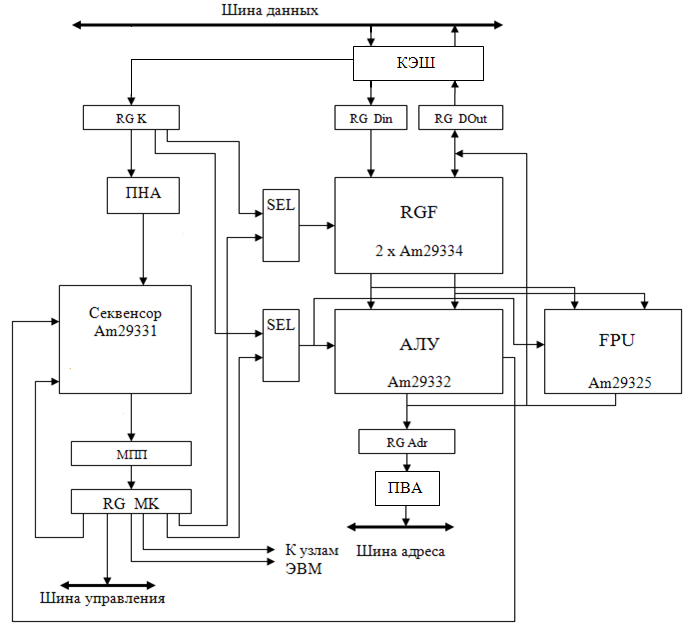

Рис. 2 –Структурная схема процессора

Получаем один конвейер: “ПНА СеквенсорМППРегистр микрокоманд”, реализованный в микропрограммном устройстве управления; и второй: “АЛУВыходной регистр адреса (данных)”, реализованный в операционном блоке.

В состав ЦП входят: операционный блок (ОБ) и микропрограммное устройство управления (МУУ).

МУУ хранит в микропрограммной памяти (МПП) и выбирает управляющие слова (т.е. МК) из МПП, передаёт их в качестве управляющих слов ОБ и другим устройствам (например, блоку синхронизации). Принимая управляющие слова, устройствами выполняются соответствующие инструкции.

Работа с ОП осуществляется через ОБ. ОБ вычисляет адрес ячейки для чтения/записи и принимает/передаёт данные из/в ОП. ОБ может принимать/передавать данные не только из/в ОП, но и с/во внешних устройств.

4.2.1. Операционный блок.

Операционный блок (ОБ) состоит из арифметико-логического устройства (АЛУ), сопроцессора плавающей точки, регистра адреса и буфера входных и выходных данных. Предназначен для выполнения логических, арифметических и сдвиговых операций над поступающими на вход данными и выдачи результата на выходную шину данных АЛУ. Регистры входных и выходных данных/адреса являются интерфейсными. Через них операционный блок обменивается информацией с шиной данных (DB).

АЛУ является полностью комбинационным устройством, выполняющим некоторый набор операций в зависимости от инструкций, поступающих с регистра микрокоманд. Результат операции АЛУ выставляет на выходной шине данных.

4.2.2. Микропрограммное устройство управления.

Основной функцией микропрограммного устройства управления (МУУ) является формирование последовательности микрокоманд, содержащих инструкции для всех узлов ЭВМ, на основе макрокоманд. Для этих целей в состав МУУ входят: Регистр команд (РГ_К), преобразователь начального адреса (ПНА), секвенсор микрокоманд, микропрограммная память (МПП) и регистр микрокоманд (РГ_МК) (См. рис. 2).

Секвенсор работает по следующему принципу:

В МПП хранятся все возможные микрокоманды (максимум ограничен разрядностью секвенсора, для Am29С331- это 16 разрядов, которые позволяют адресовать 64К микрокоманд). В ПНА хранятся адреса МПП, по которым расположены первые микрокоманды из последовательности того или иного алгоритма. Функцией ПНА является формирование начального адреса в МПП по полю КОП регистра команд, задающего конкретную макрооперацию. В каждой микрокоманде задана вся необходимая информация для работы ЭВМ на текущем такте, а также информация, на основе которой можно вычислить адрес следующей микрокоманды (нелинейные алгоритмы) либо непосредственно адрес следующей микрокоманды (линейные алгоритмы). В функции секвенсора входит формирование адреса следующей микрокоманды на основе информации, содержащейся в текущей микрокоманде и сигналов на входе тестирования внешних условий.

Разделяют два режима работы секвенсора: когда адрес следующей микрокоманды строго задан и не зависит от результатов работы ОБ на текущем шаге, и когда адрес следующей микрокоманды зависит от результата работы ОБ на текущем шаге. В первом случае процесс выработки адреса следующей микрокоманды совмещается с выполнением текущей. Во втором же случае начать выработку можно лишь после появления флагов из ОБ, то есть после завершения текущего такта. Из этого следует, что в работе МУУ будут присутствовать холостые такты.

Последовательность работы МУУ следующая:

При запуске или сбросе секвенсор вырабатывает нулевой адрес МПП, по которому расположен алгоритм загрузки системы из ОП.

Конец выполнения каждой макрокоманды связан с чтением следующей из ОП.

Прочитанная макрокоманда загружается в регистр команд. ПНА формирует начальный адрес алгоритма по полю КОП и передает его секвенсору. Секвенсор передает его на МПП, а которой происходит выборка первой микрокоманды алгоритма. В следующем такте микрокоманда с выходов МПП будет загружена в регистр микрокоманд. ОБ станет выполнять инструкции, содержащиеся в микрокоманде, а секвенсор вырабатывать адрес следующей и т.д.

Однако ЭВМ должна уметь обрабатывать события, возникновение которых равновероятно для любого момента времени и не может быть предсказано заранее. Реакцией на такое событие является прерывание выполнения текущей программы, и запуск программы обработчика события, вызвавшего это прерывание.

Разрабатываемая ЭВМ поддерживает прерывания на макроуровне, при которых переход к программе обработчику осуществляется только после завершения текущей макрокоманды прерываемой программы. Такой подход сокращает аппаратные средства, так как сохранению подлежит только адрес возврата из прерывания.

Секвенсор Am29С331имеет стек для хранения адресов возврата глубиной 33, что позволяет обрабатывать вложенные прерывания. Если стек оказался заполнен, все последующие прерывания будут игнорироваться.

Для организации обработки прерываний на макроуровне необходимо:

Секвенсор имеет три вывода, связанных с обработкой прерываний:

INTR– вход запроса на прерывание (активный высокий уровень - 1);

INTА – двунаправленный тристабильный вывод подтверждения прерывания (активный низкий уровень - 0);

INTEN– вход разрешения прерывания (активный высокий уровень - 1).

Пока на входе INTEN=0, все прерывания запрещены. Для управления этим входом предусмотрен бит микрокоманды, который принимает разрешающее значение (1), только в микрокомандах, завершающих алгоритм текущей макрокоманды. Только после загрузки последней микрокоманды, выполняемой команды в РГ_МК, секвенсор получает разрешение на прерывание. Если к этому моменту времени контроллер прерываний сформировал запрос, подав высокий уровень на входINTR, то секвенсор выдаст низкий уровень на выходINTA. Этот сигнал является положительным ответом на запрос и разрешает вывод адреса ОП, по которому расположена программа обработчик прерывания, на шину данных. По завершении текущего такта (по фронту синхросигнала), секвенсор загрузит адрес возврата из прерывания в стек. После этого, независимо от типа прерывания, ЦП производит чтение адреса с шины данных с последующей загрузкой команды, расположенной в ОП по прочитанному адресу. Таким образом, происходит переход к программе обработчику прерывания. По завершению этой программы секвенсор загрузит адрес возврата из стека и продолжит выполнение прерванной программы.