- •Разработать структурную схему гипотетической эвм, функциональную схему и алгоритм работы конкретного блока, входящего в состав этой эвм.

- •Первая часть посвящена разработке структурной схемы гипотетической

- •Исходные данные к курсовому проекту:

- •Разработка структурной схемы эвм.

- •Разработка основных блоков эвм:

- •Центральный процессор.

- •Система прерываний.

- •Кэш данных.

- •Система ввода – вывода.

- •Блок синхронизации.

- •Монитор.

- •Таймер.

- •Клавиатура.

- •Разработка кэша данных.

Министерство высшего и профессиональной образования РФ

НГТУ

Кафедра ВТ

Курсовой проект

по дисциплине «Организация ЭВМ»

Факультет: АВТ

Группа: АМ-79

Студент: Тропин К.Е.

Преподаватель: Гребенников В.Ф.

Новосибирск 2000 год.

Содержание.

Стр.

Задание на курсовой проект 3

Разработка структурной схемы ЭВМ 4

Разработка основных блоков ЭВМ

-

Центральный процессор. 5

-

Система прерываний 8

-

Основная память 10

-

Кэш данных 11

-

Система ввода – вывода 12

-

Блок синхронизации 13

-

Монитор 14

-

Таймер 14

-

Клавиатура 15

Разработка кэша данных 16

Список литературы. 19

Приложение 1 20

Цель курсового проекта:

Углубление и закрепление теоретических знаний, приобретение навыков разработки узлов ЭВМ на структурном, функциональном и алгоритмическом уровнях.

Задание на курсовой проект.

Разработать структурную схему гипотетической эвм, функциональную схему и алгоритм работы конкретного блока, входящего в состав этой эвм.

Курсовой проект состоит из двух частей:

Первая часть посвящена разработке структурной схемы гипотетической

ЭВМ, описанию ее функционирования. В состав ЭВМ входят как общие для всех вариантов блоки, так и дополнительные, определяемые индивидуальным заданием.

Вторая часть проекта посвящена разработке функциональной схемы и алгоритмов работы конкретного блока, входящего в состав ЭВМ, и их детальному описанию.

Исходные данные к курсовому проекту:

В состав ЭВМ должны входить следующие блоки (типовое задание):

-

центральное процессорное устройство (ЦПУ)

-

оперативная память (ОП)

-

система прерывания программ (СПП)

-

система ввода-вывода (СВВ)

-

монитор и клавиатура

-

блок синхронизации (БС)

Индивидуальные исходные данные:

-

архитектура ЭВМ - трех шинная

-

организация ОП – обычная

-

Кэш данных

-

Ввод/Вывод программно-управляемый с отображением в памяти

-

система прерываний – радиальная с обработкой на макро уровне

-

разрабатываемый блок – кэш данных

Разработка структурной схемы эвм.

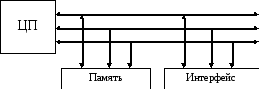

В соответствии с заданием принята трех шинная организация ЭВМ:

-

шина данных (ШД) – обеспечивает обмен данными между всеми основными блоками ЭВМ – 32р.

-

шина адреса (ША) – используется для задания адреса памяти. Им может быть как адрес в ОЗУ, ПЗУ так и адрес видеопамяти контроллера монитора – 32р.

-

шина управления (ШУ) – по этой шине осуществляется передача сигналов управления между блоками ЭВМ.

Такая структура обеспечивает три вида передачи данных:

• процессор <=> память;

• процессор <=> интерфейс;

• память <=> интерфейс.

В первых двух видах передачей данных

управляет процессор. Память и интерфейс

по управляющему сигналу от процессора

осуществляют передачу данных.

первых двух видах передачей данных

управляет процессор. Память и интерфейс

по управляющему сигналу от процессора

осуществляют передачу данных.

Шина данных

Шина адреса

Шина управления

Разработка основных блоков эвм:

-

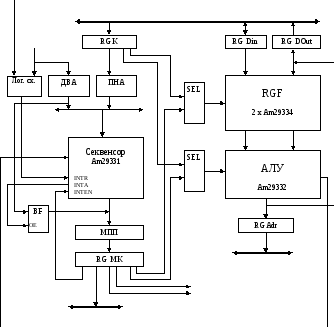

Центральный процессор.

При разработке будем ориентироваться на микросхемы серии Аm29300.

Семейство Am29300 - это набор СБИС служащий для построения высокопроизводительных 32-х разрядных систем на основе принципа микропрограммирования. Потребуются следующие элементы этого семейства:

Am29331 - Секвенсор микрокоманд. Размер адресуемой микро памяти до 64Кслов.

Аm29332 - 32-х разрядное арифметико-логическое устройство.

Am29334 - Регистровый файл. 4-х портовая память с двухсторонним доступом. Организация 64х18 бит. (32х36)

В функции ЦП входят: выполнение команд, хранящихся в ОП, и координирование работы всех узлов ЭВМ.

Работа ЦП основана на принципе микропрограммного управления.

В состав ЦП входят:

-

операционный блок (ОБ), в котором происходит обработка данных.

-

микропрограммное устройство управления, которое управляет порядком обработки команд в ОБ и осуществляет управление всеми узлами ядра ЭВМ.

СБИС Аm29332 представляет собой нерасширяемый 32 – разрядный процессорный модуль. Содержит трехвходовое комбинированное АЛУ, которое позволяет выполнять логические и арифметические операции, а также арифметические операции над числами с плавающей точкой. Внутренний групповой 64-разрядный сдвигатель, позволяет за 1 такт выполнять все виды сдвигов на любое число разрядов.

В структуру Am29332 включен блок Q-регистра (Q—сдвигатель и Q-регистр). Это позволяет поддерживать выполнение: операции умножения двух 32-разрядных чисел по модифицированному алгоритму Бута (в каждом такте сдвиг вправо на 2 разряда), и деления по алгоритму "без восстановления остатка".

БИС Аm29331, используемая в качестве секвенсора микрокоманд поддерживает прерывания реального времени на микро- и макро-уровнях управления с временем реакции, не превышающем длительности микроцикла. Заданием оговаривается система прерываний на макро уровне, поэтому в структуре предусмотрен дешифратор векторного адреса (ДВА).

Имеющийся вход сброса секвенсора RST позволяет производить «сброс» ЦП в исходное состояние при включении питания или в процессе работы путём подачи на него сигнала RESET, имеющего активный низкий уровень (на рисунке он не показан).

Хотя по заданию обработка прерываний должна осуществляться на макро- уровне, на структурной схеме процессора (см. ниже) приведена реализация обработки прерываний как на макро- так и на микро- уровне. Это объясняется тем, что прерывания от некоторых устройств (например клавиатуры или таймера) не могут обрабатываться на макро- уровне, т.к. реакция на них должна быть незамедлительна.

Запрос на

прерывание

Запрос на

прерывание

Шина данных

|

Вектор прерывания |

Шина адреса

К узлам

ЭВМ

Шина управления

Рис. 1 Структурная схема ЦП.