Пособие HCS12 & Elvis II v.7.01

.pdf1.4.3. Логические команды и операции сдвига

Данную группу образуют команды, которые выполняют операции логического И, ИЛИ, Исключающего ИЛИ, различные операции сдвига, операции взятия обратного и дополнительного кода. Следует обратить внимание на специальные команды установки признаков без изменения содержимого тестируемых регистров и ячеек памяти (TST и BIT). Все логические команды модифицируют флаги в регистре кода состояния. Команды данной группы приведены в табл. 1.6 и 1.7.

Табл. 1.6. Логические команды

Мнемокод |

Операция |

|

Выполняемое |

Способ |

Влияние на |

|||

|

|

действие |

адресации |

признаки |

||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

ANDA |

#opr |

Поразрядное логическое |

|

|

|

IMM |

|

|

ANDA |

adr |

И над содержимым |

|

|

|

DIR, EXT |

N,Z = var |

|

ANDA |

opr,r |

аккумулятора А и байтом |

|

A ← (A) & (M) |

IDX, IDX1, IDX2 |

V = 0 |

||

ANDA |

[opr,r] |

данных. Результат |

|

|

|

[IDX2] |

|

|

ANDA |

[D,r] |

поместить в А. |

|

|

|

[D,IDX] |

|

|

ANDB |

#opr |

Поразрядное логическое |

|

|

|

IMM |

|

|

ANDB |

adr |

И над содержимым |

|

|

|

DIR, EXT |

N,Z = var |

|

ANDB |

opr,r |

аккумулятора B и байтом |

|

B ← (B) & (M) |

IDX, IDX1, IDX2 |

V = 0 |

||

ANDB |

[opr,r] |

данных. Результат |

|

|

|

[IDX2] |

|

|

ANDB |

[D,r] |

поместить в B. |

|

|

|

[D,IDX] |

|

|

|

|

Поразрядное логическое |

|

|

|

|

|

|

|

|

И над регистром кода |

|

|

CCR |

|

(CCR) = var, |

|

ANDCC |

#opr |

состояния и байтом |

|

|

|

|||

|

|

← |

IMM |

только |

||||

данных (очистка |

|

|

||||||

|

|

определённых битов в |

|

(CCR) & (M) |

|

1 → 0 |

||

|

|

|

|

|

|

|

||

|

|

CCR). |

|

|

|

|

|

|

ORAA |

#opr |

Поразрядное логическое |

|

|

|

IMM |

|

|

ORAA |

adr |

ИЛИ над содержимым |

|

|

|

DIR, EXT |

N,Z = var |

|

ORAA |

opr,r |

аккумулятора А и байтом |

|

A ← (A) (M) |

IDX, IDX1, IDX2 |

V = 0 |

||

ORAA |

[opr,r] |

данных. Результат |

|

|

|

[IDX2] |

|

|

ORAA |

[D,r] |

поместить в А. |

|

|

|

[D,IDX] |

|

|

ORAB |

#opr |

Поразрядное логическое |

|

|

|

IMM |

|

|

ORAB |

adr |

ИЛИ над содержимым |

|

|

|

DIR, EXT |

N,Z = var |

|

ORAB |

opr,r |

аккумулятора B и байтом |

|

B ← (B) (M) |

IDX, IDX1, IDX2 |

V = 0 |

||

ORAB |

[opr,r] |

данных. Результат |

|

|

|

[IDX2] |

|

|

ORAB |

[D,r] |

поместить в B. |

|

|

|

[D,IDX] |

|

|

|

|

Поразрядное логическое |

|

|

|

|

S,H,I,N,Z,V,C = |

|

|

|

ИЛИ над регистром кода |

|

|

CCR |

|

||

ORCC |

#opr |

состояния и байтом |

|

|

IMM |

var, |

||

|

|

← |

||||||

данных (установка |

|

|

только |

|||||

|

|

определённых битов в |

|

(CCR) (M) |

|

0 → 1 |

||

|

|

CCR). |

|

|

|

|

|

|

EORA |

#opr |

Поразрядное |

|

|

|

IMM |

|

|

исключающее ИЛИ над |

|

|

|

|

||||

EORA |

adr |

содержимым |

|

|

|

DIR, EXT |

N,Z = var |

|

EORA |

opr,r |

аккумулятора А и байтом |

|

A ← (A) (M) |

IDX, IDX1, IDX2 |

V = 0 |

||

EORA |

[opr,r] |

данных. Результат |

|

|

|

[IDX2] |

|

|

EORA |

[D,r] |

поместить в А. |

|

|

|

[D,IDX] |

|

|

EORB |

#opr |

Поразрядное |

|

|

|

IMM |

|

|

исключающее ИЛИ над |

|

|

|

|

||||

EORB |

adr |

содержимым |

|

|

|

DIR, EXT |

N,Z = var |

|

EORB |

opr,r |

аккумулятора B и байтом |

|

B ← (B) (M) |

IDX, IDX1, IDX2 |

V = 0 |

||

EORB |

[opr,r] |

данных. Результат |

|

|

|

[IDX2] |

|

|

EORB |

[D,r] |

поместить в B. |

|

|

|

[D,IDX] |

|

|

COM |

adr |

Получение обратного |

|

|

M |

EXT |

|

|

COM |

opr,r |

кода содержимого |

|

|

← |

IDX, IDX1, IDX2 |

N,Z = var |

|

COM |

[opr,r] |

ячейки памяти М. |

|

|

|

[IDX2] |

V = 0, C = 1 |

|

( M ) = $FF − (M) |

||||||||

COM |

[D,r] |

[D,IDX] |

|

|||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

31 |

|

|

|

|

Получение обратного |

|

|

|

|

|

|

|

|

A |

|

N,Z = var |

||||||||||||

COMA |

|

|

кода содержимого |

|

|

|

|

|

|

|

← |

INH |

||||||||||||||

|

|

|

|

|

|

|

|

|

V = 0, C = 1 |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

аккумулятора А. |

( |

A |

|

) = $FF − (A) |

|

|

|||||||||||||||||

|

|

|

Получение обратного |

|

|

|

|

|

|

|

|

B |

|

N,Z = var |

||||||||||||

COMB |

|

|

кода содержимого |

|

|

|

|

|

|

|

← |

INH |

||||||||||||||

|

|

|

|

|

|

|

|

|

V = 0, C = 1 |

|||||||||||||||||

|

|

|

аккумулятора B. |

( |

B |

|

) = $FF − (B) |

|

|

|||||||||||||||||

NEG |

adr |

|

Получение |

|

|

|

|

|

|

|

|

M |

EXT |

|

||||||||||||

NEG |

opr,r |

|

дополнительного кода |

|

|

|

|

|

|

|

← |

IDX, IDX1, IDX2 |

N,Z,V,C = var |

|||||||||||||

NEG |

[opr,r] |

|

ячейки памяти М. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

|

||||

|

|

−(M) = ( M ) + 1 |

|

|||||||||||||||||||||||

NEG |

[D,r] |

|

|

[D,IDX] |

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Получение |

|

|

|

|

|

|

|

|

A |

|

|

||||||||||||

NEGA |

|

|

дополнительного кода |

|

|

|

|

|

|

|

← |

INH |

N,Z,V,C = var |

|||||||||||||

|

|

содержимого |

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

−(A) = ( A ) + 1 |

|

|

||||||||||||||||||||

|

|

|

аккумулятора А. |

|

|

|

|

|||||||||||||||||||

|

|

|

Получение |

|

|

|

|

|

|

|

|

B |

|

|

||||||||||||

NEGB |

|

|

дополнительного кода |

|

|

|

|

|

|

|

← |

INH |

N,Z,V,C = var |

|||||||||||||

|

|

содержимого |

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

−(B) = ( B ) + 1 |

|

|

||||||||||||||||||||

|

|

|

аккумулятора B. |

|

|

|

|

|||||||||||||||||||

BITA |

#opr |

|

Поразрядное логическое |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IMM |

|

||||

|

И над содержимым |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

BITA |

adr |

|

аккумулятора А и байтом |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIR, EXT |

N,Z = var |

||||

BITA |

opr,r |

|

без изменения |

|

|

|

|

|

|

(A) & (M) |

IDX, IDX1, IDX2 |

V = 0 |

||||||||||||||

BITA [opr,r] |

|

операндов. Результат |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

|

|||||

BITA |

[D,r] |

|

определяется по |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[D,IDX] |

|

||||

|

|

|

признакам N и Z. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

BITB |

#opr |

|

Поразрядное логическое |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IMM |

|

||||

|

И над содержимым |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

BITB |

adr |

|

аккумулятора B и байтом |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIR, EXT |

N,Z = var |

||||

BITB |

opr,r |

|

без изменения |

|

|

|

|

|

|

(B) & (M) |

IDX, IDX1, IDX2 |

V = 0 |

||||||||||||||

BITB [opr,r] |

|

операндов. Результат |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

|

|||||

BITB |

[D,r] |

|

определяется по |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[D,IDX] |

|

||||

|

|

|

признакам N и Z. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

TST |

adr |

|

Проверка знака и |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT |

|

||||

|

равенства 0. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

TST |

opr,r |

|

Устанавливает признаки |

|

|

|

|

|

|

(M) − 0 |

IDX, IDX1, IDX2 |

N,Z = var |

||||||||||||||

TST [opr,r] |

|

N и Z по содержимому |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

V = C = 0 |

|||||

TST |

[D,r] |

|

ячейки памяти М без его |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[D,IDX] |

|

||||

|

|

|

изменения. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Проверка знака и |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

равенства 0. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N,Z = var |

||||

TSTA |

|

|

Устанавливает признаки |

|

|

|

|

|

|

(А) − 0 |

INH |

|||||||||||||||

|

|

N и Z по содержимому |

|

|

|

|

|

|

V = C = 0 |

|||||||||||||||||

|

|

|

аккумулятора А без его |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

изменения. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Проверка знака и |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

равенства 0. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N,Z = var |

||||

TSTB |

|

|

Устанавливает признаки |

|

|

|

|

|

|

(B) − 0 |

INH |

|||||||||||||||

|

|

N и Z по содержимому |

|

|

|

|

|

|

V = C = 0 |

|||||||||||||||||

|

|

|

аккумулятора B без его |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

изменения. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

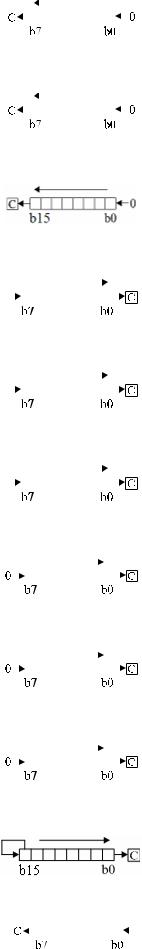

Табл. 1.7. Команды сдвигов |

|

Мнемокод |

|

Операция |

|

|

|

|

Выполняемое |

Способ |

Влияние на |

|||||||||||||||||

|

|

|

|

|

|

|

действие |

адресации |

признаки |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

ASL |

adr |

Сдвиг влево |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT |

|

|

содержимого байта |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

ASL |

opr,r |

памяти М. В бит b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IDX, IDX1, IDX2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

ASL [opr,r] |

загружается 0, бит b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

N,Z,V,C = var |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

ASL |

[D,r] |

загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[D,IDX] |

|

|

(LSL) |

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

Сдвиг влево |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

ASLA |

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

аккумулятора А. В бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

|

(LSLA) |

b0 загружается 0, бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

b7 загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

Сдвиг влево |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

ASLB |

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

аккумулятора B. В бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

||

(LSLB) |

b0 загружается 0, бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

b7 загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

Сдвиг влево |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

ASLD |

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

аккумулятора D. В бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

|||||||||||||||||||||||

(LSLD) |

b0 загружается 0, бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

b15 загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

ASR |

adr |

Сдвиг вправо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

содержимого байта |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT |

|

||||||||||||||||||||||||

ASR |

opr,r |

памяти М. Бит b7 не |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IDX, IDX1, IDX2 |

N,Z,V,C = var |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

ASR [opr,r] |

изменяется, бит b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

|

||||||||||||||||||||

ASR |

[D,r] |

загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[D,IDX] |

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

Сдвиг вправо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

ASRA |

|

аккумулятора А. Бит b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

не изменяется, бит b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

Сдвиг вправо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

ASRB |

|

аккумулятора B. Бит b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

не изменяется, бит b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

LSR |

adr |

Сдвиг вправо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

содержимого байта |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT |

|

||||||||||||||||||||||||

LSR |

opr,r |

памяти М. В бит b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IDX, IDX1, IDX2 |

Z,V,C = var |

LSR [opr,r] |

загружается 0, бит b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

N = 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

LSR |

[D,r] |

загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[D,IDX] |

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

Сдвиг вправо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Z,V,C = var |

||||||||||||||||||||||

LSRA |

|

аккумулятора А. В бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

|

|

b7 загружается 0, бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N = 0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

b0 загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

Сдвиг вправо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Z,V,C = var |

||||||||||||||||||||||

LSRB |

|

аккумулятора В. В бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

|

|

b7 загружается 0, бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N = 0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

b0 загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

Сдвиг вправо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Z,V,C = var |

||||||||||||||||||||||

LSRD |

|

аккумулятора D. В бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

|||||||||||||||||||||||

|

b15 загружается 0, бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N = 0 |

||||||||||||||||||||||||

|

|

b0 загружается в бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

ROL |

adr |

Циклический сдвиг |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT |

|

ROL |

opr,r |

влево содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IDX, IDX1, IDX2 |

N,Z,V,C = var |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

ROL [opr,r] |

байта памяти М через |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

|

|||||||||||||||||||||||

ROL |

[D,r] |

бит переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[D,IDX] |

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

Циклический сдвиг |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROLA |

|

влево содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

|

аккумулятора А через |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

бит переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Циклический сдвиг |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROLB |

|

влево содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

|

аккумулятора B через |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

бит переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROR |

adr |

Циклический сдвиг |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXT |

|

ROR |

opr,r |

вправо содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IDX, IDX1, IDX2 |

N,Z,V,C = var |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

ROR [opr,r] |

байта памяти М через |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[IDX2] |

|

||

ROR |

[D,r] |

бит переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

[D,IDX] |

|

|

|

|

Циклический сдвиг |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RORA |

|

вправо содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

|

аккумулятора А через |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

бит переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Циклический сдвиг |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RORB |

|

вправо содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

N,Z,V,C = var |

|

аккумулятора B через |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

бит переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.4.4. Команды битовых операций

Данную группу образуют команды, представленные в табл. 1.8. Наличие команд битовых операций позволяет существенно сократить управляющие программы по объему кода и времени выполнения. Обратите внимание, что команды BSET и BCLR действуют только на ячейки памяти и не действуют на регистры центрального процессора. Следует правильно указывать операнды в командах BSET и BCLR. В поле операнда команд сначала указывается адрес ячейки памяти, а затем, через запятую, маска – код, содержащий 1 в битах, которые необходимо установить:

BSET $35,4 |

;Установить в 1 бит D3 в ячейке памяти с адресом $35. |

|

||||||

BSET $FF,$81 |

;Установить в 1 биты D7 и D0 в ячейке памяти с адресом $FF. |

|||||||

BCLR ,X,1 |

;Сбросить (установить в 0) бит D0 в ячейке памяти с адресом, |

|||||||

|

|

|

;который хранится в регистре Х. |

|

|

|||

|

|

|

|

|

Табл. 1.8. Команды битовых операций |

|||

|

Мнемокод |

|

Операция |

Выполняемое |

Способ |

Влияние на |

||

|

|

действие |

адресации |

признаки |

||||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Установить в 1 биты, |

|

|

|

|

|

|

|

|

равные 1 в маске m. |

M |

|

|

||

BSET |

adr |

|

Данные располагаются в |

DIR, EXT |

N,Z = var |

|||

|

ячейке ОЗУ. В команде |

← |

||||||

BSET |

opr,r,mask |

|

используется только |

(M) (mask) |

IDX, IDX1, IDX2 |

V = 0 |

||

|

|

|

прямая и индексная |

|

|

|

|

|

|

|

|

адресация. |

|

|

|

|

|

|

|

|

Установить в 0 |

|

|

|

|

|

|

|

|

(очистить) биты, равные |

|

|

|

|

|

BCLR |

adr |

|

1 в маске m. Данные |

M |

|

|

||

|

располагаются в ячейке |

← |

DIR, EXT |

N,Z = var |

||||

BCLR |

opr,r,mask |

|

ОЗУ. В команде |

|

|

|

IDX, IDX1, IDX2 |

V = 0 |

|

(M) & ( mask ) |

|||||||

|

|

|

используется только |

|

|

|||

|

|

|

прямая и индексная |

|

|

|

|

|

|

|

|

адресация. |

|

|

|

|

|

SEC |

|

|

Установить в 1 бит |

C ← 1 |

IMM |

C = 1 |

||

(ORCC #$01) |

|

переноса С. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

CLC |

Сбросить в 0 бит |

C ← 0 |

IMM |

С = 0 |

(ANDCC #$FE) |

переноса С. |

|

|

|

SEV |

Установить в 1 бит |

V ← 1 |

IMM |

V = 1 |

(ORCC #$02) |

переполнения V. |

|

|

|

CLV |

Сбросить в 0 бит |

V ← 0 |

IMM |

V = 0 |

(ANDCC #$FD) |

переполнения V. |

|

|

|

SEI |

Установить в 1 |

|

|

|

глобальную маску |

I ← 1 |

IMM |

I = 1 |

|

(ORCC #$10) |

прерываний I. Запретить |

|

|

|

|

прерывания. |

|

|

|

CLI |

Установить в 0 |

|

|

|

глобальную маску |

I ← 0 |

IMM |

I = 0 |

|

(ANDCC #$EF) |

прерываний I. |

|

|

|

|

Разрешить прерывания. |

|

|

|

1.4.5. Команды ветвления

Инструкции ветвления вызывают изменение исполняемой последовательности команд, если выполняются определённые условия. Т.е. с помощью них можно осуществлять переходы между фрагментами программы, тем самым, пропуская или выполняя дополнительные операции. Ядро CPU12 использует три вида ветвлений: короткие, длинные, по битовым условиям. В отдельную группу также можно выделить команды организации простейших циклов.

Команды ветвления также могут быть разделены по типу условия, которое должно быть удовлетворено, чтобы в программе произошёл переход. Некоторые инструкции относятся к сразу нескольким критериям классификации. Например:

•Команды унарного ветвления исполняются всегда.

•Переходы по командам простого ветвления осуществляются, если определённый бит в регистре кода состояния имеет определённое значение.

•Переходы по командам ветвления без учёта знака выполняются, когда сравнение или тест данных в прямом коде вызывает определённую комбинацию битов регистра кода состояния.

•Переходы по командам ветвления с учётом знака выполняются, когда сравнение или тест данных в прямом и/или дополнительном кодах вызывает определённую комбинацию битов регистра кода состояния.

Короткие ветвления

Операции коротких переходов работают следующим образом: если особые условия выполнены, то к счётчику PC прибавляется 8-битное смещение со знаком. В результате исполнение программы продолжается по новому адресу.

Значения смещений ограничиваются диапазоном $80..$7F (−128..127). Поэтому разница между текущим и конечным адресами не может выходить из него.

Табл. 1.9. Команды короткого ветвления

|

|

Выполняемое |

Способ |

Влияние на |

Мнемокод |

Операция |

адресаци |

||

|

|

действие |

и |

признаки |

|

|

|

|

|

|

Унарное |

ветвление |

|

|

BRA rel |

Безусловный переход по адресу, |

|

REL |

(CCR) = const |

код смещения которого указан во |

PC ← (PC) + 2 + rel |

|||

|

втором байте команды. |

|

|

|

BRN rel |

Перейти к следующей команде. |

|

|

|

Эквивалентна команде NOP |

PC ← (PC) + 2 |

REL |

(CCR) = const |

|

|

длительностью 1 цикл. |

|

|

|

|

|

|

|

35 |

NOP |

Пустая операция. Счетчик команд |

PC ← (PC) + 1 |

INH |

(CCR) = const |

|

PC увеличивается на 1. |

|||||

|

Простое |

ветвление |

|

|

|

BCC rel |

Перейти по метке, если бит |

PC ← (PC) + 2 + rel, |

|

|

|

переноса C сброшен. Иначе перейти |

REL |

(CCR) = const |

|||

если С = 0 |

|||||

|

к следующей команде. |

|

|

|

|

BCS rel |

Перейти по метке, если бит |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

переноса C установлен. Иначе |

|||||

если С = 1 |

|||||

|

перейти к следующей команде. |

|

|

|

|

BEQ rel |

Перейти по метке, если Z = 1 (r = m). |

PC ← (PC) + 2 + rel, |

|

|

|

Иначе перейти к следующей |

REL |

(CCR) = const |

|||

если Z = 1 |

|||||

|

команде. |

|

|

|

|

BMI rel |

Перейти по метке, если N = 1 (r = m). |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

Иначе перейти к следующей |

|||||

если N = 1 |

|||||

|

команде. |

|

|

|

|

BNE rel |

Перейти по метке, если Z = 0 (r ≠ m). |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

Иначе перейти к следующей |

|||||

если Z = 0 |

|||||

|

команде. |

|

|

|

|

BPL rel |

Перейти по метке, если N = 0 (r = m). |

PC ← (PC) + 2 + rel, |

|

|

|

Иначе перейти к следующей |

REL |

(CCR) = const |

|||

если N = 0 |

|||||

|

команде. |

|

|

|

|

BVC rel |

Перейти по метке, если V = 0. Иначе |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

перейти к следующей команде. |

если V = 0 |

||||

BVS rel |

Перейти по метке, если V = 1. Иначе |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

перейти к следующей команде. |

если V = 1 |

||||

|

Ветвление без |

учёта знака |

|

|

|

BHI rel |

Перейти по метке, если r > m (без |

PC ← (PC) + 2 + rel, |

|

|

|

знака). Иначе перейти к следующей |

REL |

(CCR) = const |

|||

|

команде. |

если C Z =0 |

|

|

|

|

|

|

|

||

BHS rel |

Перейти по метке, если r ≥ m (без |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

знака). Иначе перейти к следующей |

|||||

если C = 0 |

|||||

|

команде. |

|

|

|

|

BLO rel |

Перейти по метке, если r < m (без |

PC ← (PC) +2 + rel, |

REL |

(CCR) = const |

|

знака). Иначе перейти к следующей |

|||||

если C = 1 |

|||||

|

команде. |

|

|

|

|

BLS rel |

Перейти по метке, если r ≤ m. Иначе |

PC ← (PC) + 2 + rel |

REL |

(CCR) = const |

|

перейти к следующей команде. |

C Z =1 |

||||

|

Ветвление с |

учётом знака |

|

|

|

BGE rel |

Перейти по метке, если r ≥ m (с |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

учетом знака). Иначе перейти к |

|||||

если (N V) = 0 |

|||||

|

следующей команде. |

|

|

||

|

|

|

|

||

BGT rel |

Перейти по метке, если r > m (с |

PC ← (PC) + 2 + rel, |

|

|

|

учетом знака). Иначе перейти к |

REL |

(CCR) = const |

|||

если Z & (N V) = 0 |

|||||

|

следующей команде. |

|

|

||

|

|

|

|

||

BLE rel |

Перейти по метке, если r ≤ m (с |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

учетом знака). Иначе перейти к |

|||||

если Z (N V) = 1 |

|||||

|

следующей команде. |

|

|

||

|

|

|

|

||

BLT rel |

Перейти по метке, если r < m (с |

PC ← (PC) + 2 + rel, |

REL |

(CCR) = const |

|

учетом знака). Иначе перейти к |

|||||

если (N V) = 1 |

|||||

|

следующей команде. |

|

|

||

|

|

|

|

Длинные ветвления

Операции коротких переходов работают следующим образом: если особые условия выполнены, то к счётчику PC прибавляется 16-битное смещение со знаком. В результате исполнение программы продолжается по новому адресу. Команды длинных ветвлений используются в том случае, если разница в адресах двух фрагментов программы, между которыми осуществляется переход, довольно велика.

36

Значения «длинных» смещений ограничиваются диапазоном $8000..$7FFF (−32768..32767). Таким образом, можно осуществить переход между любыми двумя точками в стандартном адресном пространстве в 64К.

Табл. 1.10. Команды длинного ветвления

Мнемокод |

Операция |

Выполняемое |

Способ |

Влияние на |

||

действие |

адресации |

признаки |

||||

|

|

|

||||

|

|

Унарное ветвление |

|

|

||

JMP |

adr |

Безусловный переход по |

|

EXT |

|

|

JMP |

opr,r |

адресу, указанному в |

PC ← Effective |

IDX, IDX1, IDX2 |

(CCR) = const |

|

JMP [opr,r] |

команде. |

Address |

[IDX2] |

|

||

JMP |

[D,r] |

|

|

[D,IDX] |

|

|

|

|

Безусловный переход по |

|

|

|

|

LBRA rel |

адресу, код смещения |

PC ← (PC) + 4 + rel |

REL |

(CCR) = const |

||

которого указан во втором |

||||||

|

|

байте команды. |

|

|

|

|

|

|

Перейти к следующей |

|

|

|

|

LBRN rel |

команде. Эквивалентна |

PC ← (PC) + 4 |

REL |

(CCR) = const |

||

команде NOP |

||||||

|

|

длительностью 3 цикла. |

|

|

|

|

|

|

Простое ветвление |

|

|

||

|

|

Перейти по метке, если |

|

|

|

|

LBCC rel |

бит переноса C сброшен. |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

||

Иначе перейти к |

если С = 0 |

|||||

|

|

следующей команде. |

|

|

|

|

|

|

Перейти по метке, если |

|

|

|

|

LBCS rel |

бит переноса C |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

||

установлен. Иначе |

||||||

если С = 1 |

||||||

|

|

перейти к следующей |

|

|

|

|

|

|

команде. |

|

|

|

|

LBEQ rel |

Перейти по метке, если Z |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

||

= 1 (r = m). Иначе перейти |

||||||

если Z = 1 |

||||||

|

|

к следующей команде. |

|

|

|

|

LBMI rel |

Перейти по метке, если N |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

||

= 1 (r = m). Иначе перейти |

||||||

если N = 1 |

||||||

|

|

к следующей команде. |

|

|

|

|

LBNE rel |

Перейти по метке, если Z |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

||

= 0 (r ≠ m). Иначе перейти |

||||||

если Z = 0 |

||||||

|

|

к следующей команде. |

|

|

|

|

LBPL rel |

Перейти по метке, если N |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

||

= 0 (r = m). Иначе перейти |

||||||

если N = 0 |

||||||

|

|

к следующей команде. |

|

|

|

|

LBVC rel |

Перейти по метке, если V |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

||

= 0. Иначе перейти к |

||||||

если V = 0 |

||||||

|

|

следующей команде. |

|

|

|

|

LBVS rel |

Перейти по метке, если V |

PC ← (PC) + 4 + rel, |

|

|

||

= 1. Иначе перейти к |

REL |

(CCR) = const |

||||

если V = 1 |

||||||

|

|

следующей команде. |

|

|

|

|

|

|

Ветвление |

без учёта знака |

|

|

|

|

|

Перейти по метке, если r > |

PC ← (PC) + 4 + rel, |

|

|

|

LBHI rel |

m (без знака). Иначе |

REL |

(CCR) = const |

|||

перейти к следующей |

если C Z = 0 |

|||||

|

|

команде. |

|

|

|

|

|

|

Перейти по метке, если r ≥ |

PC ← (PC) + 4 + rel, |

|

|

|

LBHS rel |

m (без знака). Иначе |

REL |

(CCR) = const |

|||

перейти к следующей |

если C = 0 |

|||||

|

|

команде. |

|

|

|

|

|

|

Перейти по метке, если r < |

|

|

|

|

LBLO rel |

m (без знака). Иначе |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

||

перейти к следующей |

если C = 1 |

|||||

|

|

команде. |

|

|

|

|

|

|

|

|

|

37 |

|

LBLS rel |

Перейти по метке, если r ≤ |

PC ← (PC) + 4 + rel |

REL |

(CCR) = const |

m. Иначе перейти к |

C Z = 1 |

|||

|

следующей команде. |

|

|

|

|

|

|

|

|

|

Ветвление |

с учётом знака |

|

|

|

Перейти по метке, если r ≥ |

PC ← (PC) + 4 + rel, |

|

|

LBGE rel |

m (с учетом знака). Иначе |

REL |

(CCR) = const |

|

перейти к следующей |

если (N V) = 0 |

|||

|

команде. |

|

|

|

|

Перейти по метке, если r > |

|

|

|

LBGT rel |

m (с учетом знака). Иначе |

PC ← (PC) + 4 + rel, |

REL |

(CCR) = const |

перейти к следующей |

если Z & (N V) = 0 |

|||

|

команде. |

|

|

|

|

Перейти по метке, если r ≤ |

PC ← (PC) + 4 + rel, |

|

|

LBLE rel |

m (с учетом знака). Иначе |

REL |

(CCR) = const |

|

перейти к следующей |

если Z (N V) = 1 |

|||

|

команде. |

|

|

|

|

Перейти по метке, если r < |

PC ← (PC) + 4 + rel, |

|

|

LBLT rel |

m (с учетом знака). Иначе |

REL |

(CCR) = const |

|

перейти к следующей |

если (N V) = 1 |

|||

|

команде. |

|

|

|

Ветвление по битовому условию

Переходы по битовому условию осуществляются тогда, когда биты в байте памяти находятся в определённом состоянии. Разряды, которые необходимо проверить, указываются с помощью маски. Если все помеченные биты установлены в 1 (команда BRSET) или сброшены в 0 (команда BRCLR), то осуществляется переход.

Значения смещений ограничивается диапазоном $80..$7F (−128..127).

38

Табл. 1.11. Команды ветвления по битовому условию

|

Мнемокод |

|

Операция |

|

|

Выполняемое |

Способ |

|

Влияние на |

||||||

|

|

|

|

действие |

адресации |

|

признаки |

||||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

Перейти по |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

указанному |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

адресу, если |

|

|

|

|

|

|

|

|

|

|

|

|

BRCLR adr,mask,rel |

биты, указанные |

|

|

|

|

|

|

DIR, EXT |

|

|

|

||||

в маске с |

PC ← (PC) + 4 + rel , |

|

(CCR) = const |

||||||||||||

BRCLR opr,r,mask,rel |

помощью 1, |

если (mask) & (M) = 0 |

|

|

|

||||||||||

сброшены в |

IDX, IDX1, IDX2 |

|

|

||||||||||||

|

|

|

байте данных. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Иначе перейти к |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

следующей |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

команде. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Перейти по |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

указанному |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

адресу, если |

|

|

|

|

|

|

|

|

|

|

|

|

BRSET adr,mask,rel |

биты, указанные |

PC ← (PC) + 4 + rel , |

|

|

|

|

|

||||||||

в маске с |

DIR, EXT |

|

|

|

|||||||||||

BRSET opr,r,mask,rel |

помощью 1, |

если ( |

mask |

) & (M) = |

IDX, IDX1, IDX2 |

(CCR) = const |

|||||||||

установлены в |

|

0 |

|

|

|

|

|||||||||

|

|

|

байте данных. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Иначе перейти к |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

следующей |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

команде. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Табл. 1.12. Сравнение коротких команд ветвления |

|||||||||

|

|

Прямой переход |

|

|

|

Обратный переход |

|

Комментарии |

|

||||||

|

Тест |

Мнемоника |

Состояние |

|

|

|

Тест |

|

Мнемоника |

|

|

||||

|

признаков |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

r > m |

BGT |

|

Z + (N V) = 0 |

|

|

r ≤ m |

|

BLE |

|

|

|

|

||

|

r ≥ m |

BGE |

|

N V = 0 |

|

|

|

r < m |

|

BLT |

|

|

с |

|

|

|

r = m |

BEQ |

|

Z = 1 |

|

|

|

r ≠ m |

|

BNE |

|

|

учётом |

|

|

|

r ≤ m |

BLE |

|

Z + (N V) = 1 |

|

|

r > m |

|

BGT |

|

|

знака |

|

||

|

r < m |

BLT |

|

N V = 1 |

|

|

|

r ≥ m |

|

BGE |

|

|

|

|

|

|

r > m |

BHI |

|

С + Z = 0 |

|

|

|

r ≤ m |

|

BLS |

|

|

|

|

|

|

r ≥ m |

BHS / BCC |

C = 0 |

|

|

|

r < m |

|

BLO / BCS |

|

|

без |

|

||

|

r = m |

BEQ |

|

Z = 1 |

|

|

|

r ≠ m |

|

BNE |

|

|

учёта |

|

|

|

r ≤ m |

BLS |

|

C + Z = 1 |

|

|

|

r > m |

|

BHI |

|

|

знака |

|

|

|

r < m |

BLO / BCS |

C = 1 |

|

|

|

r ≥ m |

|

BHS / BCC |

|

|

|

|

||

|

Перенос |

BCS |

|

C = 1 |

|

|

Нет переноса |

|

BCC |

|

|

|

|

||

|

Отриц. рез. |

BMI |

|

N = 1 |

|

|

Полож. рез. |

|

BPL |

|

|

Простые |

|

||

|

Пере- |

BVS |

|

V = 1 |

|

|

Нет пере- |

|

BVC |

|

|

|

|||

|

полнение |

|

|

|

|

полнения |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

BNE |

|

|

|

|

|||

|

Ноль |

BEQ |

|

Z = 1 |

|

|

Не равно 0 |

|

|

|

|

|

|||

|

Всегда |

BRA |

|

– |

|

|

|

Никогда |

|

BRN |

|

Безусловные |

|

||

Для длинных инструкций ветвления можно получить аналогичную таблицу сравнения:

Табл. 1.13. Сравнение длинных команд ветвления

|

Прямой переход |

Обратный переход |

Комментарии |

||

Тест |

Мнемоника |

Состояние |

Тест |

Мнемоника |

|

признаков |

|

||||

|

|

|

|

|

|

r > m |

LBGT |

Z + (N V) = 0 |

r ≤ m |

LBLE |

|

r ≥ m |

LBGE |

N V = 0 |

r < m |

LBLT |

с |

r = m |

LBEQ |

Z = 1 |

r ≠ m |

LBNE |

учётом |

r ≤ m |

LBLE |

Z + (N V) = 1 |

r > m |

LBGT |

знака |

r < m |

LBLT |

N V = 1 |

r ≥ m |

LBGE |

|

r > m |

LBHI |

С + Z = 0 |

r ≤ m |

LBLS |