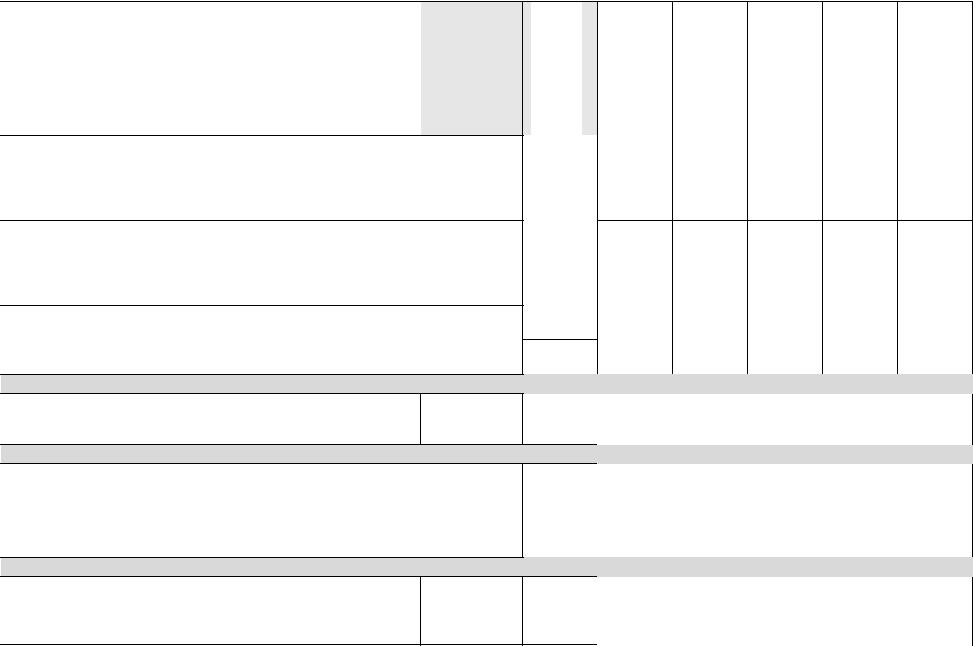

Пособие HCS12 & Elvis II v.7.01

.pdf

|

ПЗУ |

ОЗУ, |

EEPROM, |

Тип МК |

FLASH, |

байт |

байт |

|

байт |

|

|

|

|

|

|

MC9S12DB128 |

131072 |

8192 |

2048 |

|

MC9S12DB128B 131072 8192 2048

MC9S12DG128 131072 8192 2048

MC9S12DG128B

MC9S12DG256B 26144 12288 4096

MC9S12DJ128 131072 8192 2048

MC9S12DJ128B

MC9S12DJ256B 262144 12288 4096

Число линий ввода/вывода |

|

Контроллеры последователь ных интерфейсов |

|

|

|

|

BYTEFLIGH |

|

|

|

T |

912xCAN

2xSCI

2xSPI

|

BYTEFLIGH |

|

91 |

T |

|

CAN |

||

|

2xSCI |

|

|

2xSPI |

|

|

2xCAN |

|

59 |

IIC |

|

2xSCI |

||

91 |

||

SCP |

||

|

||

|

2xSPI |

|

|

2xCAN |

|

91 |

IIC |

|

2xSCI |

||

|

||

|

2xSPI |

|

|

2 CAN |

|

59 |

IIC |

|

J1850 |

||

91 |

||

2xSCI |

||

|

||

|

2xSPI |

|

|

2xCAN |

|

59 |

IIC |

|

J1850 |

||

91 |

||

2xSCI |

||

|

||

|

3xSPI |

ТаймерЧисло , /каналовразрядность

8/16

8/16

7/16

8/16

8/16

7/16

8/16

7/16

8/16

АЦП, Число каналов/ разрядность |

Модуль ШИМ, число каналов/ разрядность |

Специальные модули * |

Частота шины CPU, МГц |

Напряжение Питания, В |

|

|

|

|

|

|

|

16/10 |

8/8 |

EBUS |

25 |

5.0 |

|

|

|

|

|

|

|

16/10 |

8/8 |

EBUS |

25 |

5.0 |

|

|

|

|

|

|

|

16/10 |

8/8 |

EBUS |

25 |

5.0 |

|

|

|||||

|

|

|

|

|

|

16/10 |

4/16 |

EBUS |

25 |

5.0 |

|

8/8 |

LVI |

||||

|

|

|

|||

|

|

|

|

|

|

8/10 |

4/16 |

EBUS |

25 |

5.0 |

|

8/8 |

|||||

|

|

|

|

||

|

|

|

|

|

|

8/10 |

4/16 |

EBUS |

25 |

5,0 |

|

8/8 |

|||||

|

|

|

|

||

|

|

|

|

|

11

|

|

|

|

|

ПЗУ |

|

|

ОЗУ, |

|

|

|

EEPROM, |

|

|

|

линийЧисло вывода/ввода |

|

|

Тип МК |

|

|

|

FLASH, |

|

|

байт |

|

|

|

байт |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

байт |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MC9S12DP256B |

|

262144 |

|

12288 |

|

4096 |

|

|

91 |

|

|||||||

MC9S12DP512 |

|

512000 |

|

12288 |

|

4096 |

|

|

91 |

|

|||||||

MC9S12DT128 |

|

131072 |

|

8192 |

|

2048 |

|

|

91 |

|

|||||||

MC9S12DT128B |

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

MC9S12DT256B |

|

262144 |

|

12288 |

|

4096 |

|

|

91 |

|

|||||||

Серия E |

|

65536 |

|

|

|

|

|

|

нет |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

MC9S12E64 |

|

|

4096 |

|

|

|

|

59 |

|

||||||||

|

|

8192 |

|

|

|

|

|

91 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Серия G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

16000 |

|

2000 |

|

|

|

нет |

|

60 |

|

|||||||

MC9S12GC16 |

|

|

|

|

|

|

|

||||||||||

MC9S12GC32 |

|

32000 |

|

2000 |

|

|

|

нет |

|

60 |

|

||||||

MC9S12GC64 |

|

64000 |

|

4000 |

|

|

|

нет |

|

60 |

|

||||||

MC9S12GC96 |

|

96000 |

|

4000 |

|

|

|

нет |

|

60 |

|

||||||

MC9S12GC128 |

|

128000 |

|

4000 |

|

|

|

нет |

|

60 |

|

||||||

Серия H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

MC9S12H128 |

|

131072 |

|

6000 |

|

|

4096 |

|

|

99 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Контроллеры |

последователь |

ных |

интерфейсов |

5xCAN IIC J1850 2xSCI 3xSPI

5xCAN IIC J1850 2xSCI 3xSPI

3xCAN IIC 2xSCI 2xSPI

IIC 3xSCI SPI

SCI

SPI

2xCAN IIC 2xSCI SPI

Таймер, Число каналов/ разрядность |

|

АЦП, Число каналов/ разрядность |

Модуль ШИМ, число каналов/ разрядность |

Специальные модули * |

Частота шины CPU, МГц |

Напряжение Питания, В |

|

|

|

|

|

|

|

8/16 |

16/10 |

8/8 |

EBUS |

25 |

5,0 |

|

8/16 |

16/10 |

8/8 |

EBUS |

25 |

5,0 |

|

|

|

|

|

|

|

|

8/16 |

8/10 |

4/16 |

EBUS |

25 |

5,0 |

|

8/8 |

||||||

|

|

|

|

|

||

8/16 |

8/10 |

4/16 |

EBUS |

25 |

5,0 |

|

8/8 |

LVI |

|||||

|

|

|

|

|||

|

|

|

|

|

|

|

4/16 |

16/10 |

6/8 |

PWMF |

25 |

5.0 |

|

|

2 DAC |

|||||

|

|

|

|

|

||

8/16 |

|

|

|

|

|

|

|

|

|

|

|

||

8/10 |

6/8 |

LVI |

16/25 |

|

||

8/16 |

8/10 |

6/8 |

LVI |

16/25 |

3.3 |

|

8/16 |

8/10 |

6/8 |

LVI |

25 |

||

5.0 |

||||||

8/16 |

8/10 |

6/8 |

LVI |

25 |

||

|

||||||

8/16 |

8/10 |

6/8 |

LVI |

25 |

|

|

|

|

|

|

|

|

|

|

|

4/16 |

EBUS |

|

|

|

8/16 |

16/10 |

LVI |

16 |

5.0 |

||

8/8 |

LCD 32×4 |

|||||

|

|

|

|

|||

|

|

|

MC 24 |

|

|

12

|

ПЗУ |

ОЗУ, |

EEPROM, |

Тип МК |

FLASH, |

байт |

байт |

|

байт |

|

|

|

|

|

|

MC9S12H256 |

262144 |

12288 |

4096 |

Разные МК |

|

|

|

MC9S12NE64 |

64000 |

8000 |

нет |

MC9S12T64 |

65536 |

2048 |

2048 |

MC9S12UF32 |

32768 |

3584 |

нет |

|

|

|

|

Число линий ввода/вывода |

Контроллеры последователь ных интерфейсов |

|

Таймер, Число каналов/ разрядность |

|

АЦП, Число каналов/ разрядность |

Модуль ШИМ, число каналов/ разрядность |

Специальные модули * |

Частота шины CPU, МГц |

Напряжение Питания, В |

|

|

|

|

|

|

|

|

|

|

99 |

|

8/16 |

|

16/10 |

4/16 |

EBUS |

16 |

5.0 |

|

|

|

8/8 |

LVI |

||||||

|

|

|

|

|

|

|

|

||

|

Ethernet |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

IIC |

4/16 |

|

8/10 |

нет |

RTI |

25 |

3.3 |

|

80 |

2xSCI |

|

5.0 |

||||||

|

|

|

|

|

|

|

|||

|

SPI |

|

|

|

|

|

|

|

|

|

SCI |

8/16 |

|

8/10 |

4/16 |

|

|

5.0 |

|

|

SPI |

|

8/8 |

|

|

||||

|

|

|

|

|

|

|

|

||

75 |

SCI |

8/16 |

|

|

|

|

30 |

5.0 |

|

USB 2.0 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

Примечание:

EBUS – модуль интерфейса внешней магистрали;

LVI – модуль контроля за пониженным напряжением питания; RTI – модуль меток реального времени;

PWMF – модуль специализированного генератора для управления силовыми коммутаторами в электроприводе; DAC – модуль одноканального ЦАП;

LCD 32×4 – контроллер управления ЖКИ дисплеем (4 группы по 32 сегмента);

MC 24 – 24 выхода с повышенной токовой нагрузкой для управления маломощными шаговыми электродвигателями.

13

1.2. Программно-логическая модель процессора HCS12

Центральный процессор МК семейства HCS12 (далее ЦП) выполняет действия над 8-ми или 16-разрядными операндами. Программная модель ЦП (рис. 1.2) содержит семь регистров, которые не входят в объединенное адресное пространство. Поэтому для обращения к ним используются специальные команды.

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Аккумулятор D |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Аккумулятор А |

|

|

|

|

|

Аккумулятор B |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

0 |

|

7 |

|

|

|

|

|

|

0 |

Сброс: |

х |

х |

х |

х |

х |

х |

х |

х |

|

х |

х |

х |

х |

х |

х |

х |

х |

|

|

|

15 |

|

|

|

|

|

|

8 |

7 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Индексный регистр X |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сброс: |

|

x |

x |

x |

x |

x |

x |

x |

x |

|

х |

х |

х |

х |

х |

х |

х |

х |

|

|

15 |

|

|

|

|

|

|

8 |

7 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Индексный регистр Y |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сброс: |

|

x |

x |

x |

x |

x |

x |

x |

x |

|

х |

х |

х |

х |

х |

х |

х |

х |

|

|

15 |

|

|

|

|

|

|

8 |

7 |

|

|

|

|

|

|

0 |

|

Счетчик адреса PC

Сброс: загружается начальным адресом из ячеек памяти вектора сброса

|

|

15 |

|

|

8 |

7 |

|

|

|

|

|

|

|

0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Указатель стека SP |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сброс: |

|

x |

x |

x |

x |

|

x |

|

x |

x |

x |

х |

х |

х |

х |

х |

х |

х |

х |

|

|

|

|

|

|

|

|

|

|

|

|

|

Регистр кода состояния CCR |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

S |

X |

H |

I |

N |

Z |

V |

С |

|

|

|

|

|

|

|

|

|

|

Сброс: |

1 |

|

1 |

x |

1 |

x |

x |

x |

x |

||

Рис.1.2. Программно-логическая модель центрального процессора МК HCS12

Аккумуляторы (А, B; A + B = D – double accumulator) – два 8-разрядных регистра

А и В, которые могут использоваться совместно как 16-разрядный аккумулятор D. В аккумуляторах хранятся операнды и результаты арифметических и логических операций. Сброс не изменяет состояние аккумуляторов.

Индексные регистры (X и Y) – 16-разрядные регистры. Основное назначение индексного регистра – участие в формировании адреса операнда в режимах индексной

14

адресации. Индексный регистр может также использоваться для хранения промежуточных результатов вычислений или как источник одного из операндов в операциях умножения и деления. Система команд ЦП предусматривает загрузку данных в индексный регистр и выполнение операций над ними как в двухбайтовом, так и в однобайтовом форматах. В последнем случае обращение производится только к младшему байту регистра. Стоит отметить, что ядро HCS12 позволяет использовать в качестве индексного любой другой регистр по усмотрению программиста.

Программный счетчик (PC – program counter) – 16-разрядный регистр, содержит адрес текущей команды, либо адрес операнда, используемого в текущей команде. После сброса ЦП программный счетчик автоматически загружается вектором начального запуска, который записан в ячейках памяти резидентного ПЗУ с адресами $FFFE (старший байт) и $FFFF (младший байт). Вектор начального запуска является адресом начала прикладной программы управления.

Указатель стека (SP – stack pointer) – 16-разрядный регистр, содержит адрес верхушки стека. Вызов подпрограммы использует 2 ячейки стека, прерывание – 5 ячеек.

Регистр кода состояния (CCR – condition code register) – 8-разрядный регистр,

содержит 5 флагов условий (признаков): дополнительного переноса (H), знака (N), нулевого результата (Z), переполнения (V), переноса (С) и 3 бита маскирования: маски выполнения команды STOP (S), маски прерывания (X), глобальной маски прерывания (I). Сброс МК не влияет на состояние флагов ЦП.

Краткое описание логики установки флагов ЦП

C – флаг переноса (Carry/Borrow status bit)

Устанавливается в 1, если в результате операции сложения произошло переполнение разрядной сетки аккумулятора или в результате операции вычитания произошел заем. Часть логических операций могут устанавливать, либо сбрасывать флаг переноса C.

Z – флаг нулевого результата (Zero status bit)

Устанавливается в 1, если результат арифметической, логической операции или операции пересылки данных равен 0.

N – флаг отрицательного результата (Negative status bit)

Флаг показывает состояние старшего бита результата выполнения арифметической, логической или операции пересылки данных. Обычно используется в арифметике дополнительных кодов. Если результат команды размещён в аккумуляторе D, то:

N = D15 = 0 – число положительное, N = D15 = 1 – число отрицательное

H – флаг полупереноса (Half-Carry status bit)

Устанавливается в 1 при возникновении переноса между разрядами D3 и D4 аккумулятора при выполнении операций сложения ADD и сложения с переносом ADDC. Этот признак необходим, если при обработке численных значений используют двоично-

десятичное кодирование (BCD – binary-coded decimal).

V – флаг переполнения (Two’s complement overflow status bit)

Устанавливается в 1, если при выполнении арифметической операции получается результат, выходящий за пределы диапазона чисел, представленных с использованием арифметики дополнительных кодов. Теория систем счисления устанавливает следующее правило формирования флага переполнения: при сложении переполнение происходит только в том случае, если слагаемые имеют одинаковые знаки, а знак суммы (старший бит результата) отличается от знака слагаемых. Этот признак используется командами ветвления BGT, BGE, BLE, BLT. Бит переполнения V может быть также изменен командами сдвигов, однако в этом случае результат операции не несёт смысловой нагрузки.

I – глобальная маска прерывания (Maskable interrupt control bit)

Установка маски прерывания в 1 запрещает все прерывания, кроме программного по команде SWI. Если запрос на прерывание появится, когда маска I = 0, то центральный процессор сохранит в стеке содержимое программного счетчика PC, аккумулятора АСС,

15

индексных регистров и регистра признаков, установит бит I в 1 и перейдет на выполнение подпрограммы прерывания. Если запрос на прерывание появится, когда флаг I = 1, то запрос на прерывание будет запомнен. Микроконтроллер начнёт обрабатывать запрос на прерывание сразу, как только бит I будет очищен. Инструкция RTI (возврат из прерывания) сбрасывает бит I в 0 автоматически. CPU12 имеет две специальные команды: CLI – очистить бит маски, SEI – установить бит маски. В состоянии сброса бит I устанавливается в 1, что запрещает аппаратные прерывания. Разрешение аппаратных прерываний (установка I в 0) может быть выполнено только программно командой CLI.

X – маска прерывания (Non-maskable interrupt control bit)

Служит для управления обработкой внешних запросов на прерывание, поступающих

на вход XIRQ микроконтроллера. Единичное значение Х запрещает внешние прерывания.

Бит Х устанавливается при переходе к обработке прерывания или программным путем. Сброс флага возможен только программно при использовании команды ТАР.

S – маска выполнения команды STOP (STOP instruction control bit)

Установка бита S в 1 запрещает операции завершения выполнения программы и перевода МК в режим малого потребления. В этом случае команда STOP эквивалентна пустой операции NOP. Если S = 0, то МК переходит в режим ожидания (ОСТАНОВКА), выйти из которого можно только по прерыванию или аппаратным сбросом. Если прерывания маскированы (Х = 1), то вместо команды STOP выполняется следующая по порядку команда.

1.3. Способы адресации

Для выборки операндов из памяти МК семейства HCS12 используют следующие способы адресации:

•Внутренняя или неявная (INH – Inherent);

•Непосредственная (IMM – Immediate);

•Прямая (DIR – Direct);

•Прямая расширенная (EXT – Extended);

•Относительная (REL – Relative);

•Индексная (IDX – Indexed).

Индексный тип адресации имеет свои подтипы, о которых будет сказано далее.

1.3.1.Внутренняя или неявная адресация INH

Кинструкциям с неявной адресацией относятся команды, которые не требуют для своего выполнения каких либо операндов, например, команда STOP или команда возврата из прерывания RTI.

Неявную адресацию имеют инструкции, которые содержат адрес операнда в коде команды, например, команда установки бита переноса SEC или команда инкремента аккумулятора INCA. Все команды с неявной адресацией имеют длину в 1 байт и состоят только из кода операции.

1.3.2.Непосредственная адресация IMM

Код операции команды с непосредственной адресацией размещается в первом байте. Сразу же за кодом операции следуют байты данных. Эти данные не могут быть изменены

16

в ходе выполнения программы, т. к. они расположены непосредственно в памяти программ, т.е. в ПЗУ. Признаком непосредственного операнда в мнемонике команды служит знак #, после которого записывается операнд – opr:

Примеры:

ADDA |

#opr |

;Запись команды ADDA с непосредственной адресацией в |

ADDA |

#31 |

;общем виде. |

;Сложить содержимое аккумулятора А с числом 31, |

||

ORAA |

#$0A |

;результат записать в А. |

;Выполнить операцию поразрядного логического ИЛИ над |

||

|

|

;содержимым А и шестнадцатеричным числом $0A. |

|

|

;Результат записать в А. |

1.3.3. Прямая адресация DIR

Команды с прямой адресацией имеют длину 2 байта. Первый байт предназначен для кода команды, второй байт содержит адрес ячейки памяти, где хранится операнд. Так как МК семейства HCS12 имеют адресное пространство, превышающее диапазон $00..$FF, то во втором байте команды задается только младший байт адреса, а старший автоматически определяется как $00. Условное обозначение адреса в мнемонике команды – opr.

Примеры: |

|

ADDB opr |

;Запись команды ADDB с прямой адресацией в общем виде. |

ADDB $31 |

;Сложить содержимое аккумулятора B с содержимым ячейки |

ORAA $0A |

;памяти с адресом $0031. Результат поместить в B. |

;Выполнить операцию поразрядного логического ИЛИ над А и |

|

|

;содержимым ячейки памяти с адресом $000A. Результат |

|

;поместить в A. |

1.3.4. Прямая расширенная адресация EXT

Адресное поле команд с прямой расширенной адресацией занимает 2 байта. В поле операнда командной строки указывается полный адрес ячейки памяти, где хранится операнд. Команды с прямой расширенной адресацией позволяют работать со всем адресным пространством МК. Мнемонические обозначения команд с прямой и прямой расширенной адресацией совпадают. При компиляции программ не следует заботиться о том, что инструкции с прямой и расширенной адресациями имеют одинаковый синтаксис. Среда разработки самостоятельно подставит код необходимой операции, проанализировав численное значение адреса opr.

Примеры: |

|

ADDA opr |

;Запись команды ADDA с прямой расширенной адресацией в |

ADDA $01E1 |

;общем виде. |

;Сложить содержимое аккумулятора А с содержимым ячейки |

|

LDX $01E1 |

;памяти с адресом $01E1. Результат поместить в A. |

;Загрузить в индексный регистр X содержимое ячеек памяти |

|

|

;с адресами $01E1 и $01Е2. |

17

1.3.5. Относительная адресация REL

Относительная адресация используется только в командах условных переходов, которые используются для организации ветвления программ. Команды условных переходов имеют двухбайтовый формат. Первый байт содержит код операции, а второй – смещение адреса следующей команды относительно адреса текущей команды в целочисленном формате со знаком. Диапазон возможных кодов смещения: от -128 до

+127.

Если условие, заданное типом используемой команды условного перехода, выполняется, то адрес следующей команды центральный процессор вычисляет путем сложения текущего адреса с кодом смещения. Если условие не выполняется, то МК переходит к выполнению следующей команды.

При написании программ нет необходимости вычислять абсолютные коды смещения для команд условного перехода. Достаточно указать лишь метку, численное значение кода смещения вычислит компонент среды разработки при ассемблировании программы.

Примеры:

BCC |

opr |

;Запись команды BCC (переход на адрес opr, если С = 0) в общем |

виде. |

M1 |

|

BCC |

;Перейти к выполнению команды по адресу метки М1, если С = 0. |

|

BCS |

24 |

;Перейти к выполнению команды, расположенной на 24 адреса |

|

|

;ниже, если C = 1. |

1.3.6.Индексная адресация IDX

Вкомандах с индексной адресацией адрес операнда определяется по содержимому двухбайтового индексного регистра Х или Y, указателя стека SP или программного счётчика PC. Т.е. одна из указанных ячеек ЦП МК используется в качестве указателя. Поле операнда команд делится на две части запятой, которая отделяет код смещения от имени используемого регистра. Смещение может быть как положительным, так и отрицательным. Если оно отсутствует (нулевое), то позиция перед запятой может оставаться пустой. Для вычисления конечного двухбайтового адреса операнда ЦП складывает данные в регистре с кодом смещения. В процессе этой операции содержимое ячейки-указателя остаётся неизменным.

Вкоманду с индексной адресацией могут быть добавлены так называемые расширения. Указываются они после запятой совместно с именем регистра. Расширения – это, по сути, дополнительные инструкции к команде. С их помощью можно выполнять автоматическое изменение указателя.

Дополнительные действия в командах с индексной адресацией можно разделить на предварительные (пре-) и последующие (пост-). Первые осуществляются до выполнения основной инструкции, а вторые – после. Всего существует 4 типа расширений:

•Пре-инкрементирование;

•Пре-декрементирование;

•Пост-инкрементирование;

•Пост-декрементирование.

Инкрементирование – это увеличение содержимого регистра на определённую величину, декрементирование – сходная операция уменьшения. Если в команде указано любое дополнительное действие, то значение в поле смещения автоматически интерпретируется как код величины изменения содержимого регистра. Т.е. при каждом

18

выполнении инструкции значение указателя будет изменяться на запрограммированную величину.

Примеры: |

|

ADDA ,X |

;Сложить содержимое аккумулятора А с содержимым ячейки |

LDAB -4,SP |

;памяти, адрес которой находится в индексном регистре X. |

;Загрузить в аккумулятор B содержимое ячейки памяти, |

|

|

;адресом которой является значение указателя стека SP, |

LDAA 2,Y+ |

;уменьшенное на 4. |

;Загрузить в аккумулятор A содержимое ячейки памяти, адресом |

|

|

;которой является содержимое индексного регистра Y. |

|

;После выполнения действий увеличить значение Y на 2. |

Второй байт |

Исходный |

|

команды |

код |

|

rr0nnnnn |

,r |

|

n,r |

||

|

-n,r |

|

111rr0zs |

n,r |

|

-n,r |

||

|

||

|

|

|

111rr011 |

[n,r] |

|

|

|

|

|

n,-r |

|

rr1pnnnn |

n,+r |

|

n,r- |

||

|

||

|

n,r+ |

|

|

|

|

|

A,r |

|

111rr1aa |

B,r |

|

|

D,r |

|

|

|

|

111rr111 |

[D,r] |

|

|

|

Табл. 1.2. Сравнение различных видов индексной адресации

Комментарии

rr: 00 = X, 01 = Y, 10 = SP, 11 = PC

5-битное смещение n = -16 .. +15

r может означать регистр X, Y, SP или PC

9- или 16-битное смещение

z = 0: 9-битное смещение со знаком в бите s второго байта команды, -256 ≤ n ≤ 255

z = 1: 16-битное смещение, -32768 ≤ n ≤ 65535

если z = s = 1, то это 16-битное смещение с косвенной индексной адресацией (см. ниже)

r может означать регистр X, Y, SP или PC

16-битное смещение с косвенной индексной адресацией r может означать регистр X, Y, SP или PC

Автоматическое изменение регистра-указателя p = 0 – пре-инструкция / 1 – пост-инструкция

n = -8 .. -1, +1 .. +8 +8 = 0111

…

+1 = 0000 -1 = 1111

…

-8 = 1000

r может означать регистр X, Y, SP или PC

Смещение в аккумуляторе (8- или 16-битное без знака)

aa:00 = A

01 = B

10 = D (16 бит)

11 = смещение в аккумуляторе D с косвенной индексной

адресацией (см. ниже)

r может означать регистр X, Y, SP или PC

Смещение в аккумуляторе D с косвенной индексной адресацией r может означать регистр X, Y, SP или PC

При индексном способе адресации во втором байте команды хранится информация о том, какой из регистров будет выступать в роли базового индексного регистра (указателя) и как сформировать, так называемый, эффективный адрес. Существует специальная группа инструкций, с помощью которых можно вычислить и загрузить в индексный регистр эффективный адрес, чтобы выполнить над ним какие-либо операции:

•LEAS – загрузка эффективного адреса в указатель стека;

•LEAX – загрузка эффективного адреса в индексный регистр X;

•LEAY – загрузка эффективного адреса в индексный регистр Y.

19

Индексная адресация IDX со смещением в 5 бит

При данном типе адресации используется пятиразрядный код смещения с учётом знака, который полностью входит в состав второго байта команды. Эта короткая добавка прибавляется к содержимому базового индексного регистра (X, Y, SP, или PC), как и было сказано ранее, для получения адреса операнда. Значение смещения при этом может варьироваться от -16 до +15. Хотя другие способы индексной адресации позволяют использовать 9- и 16-битные коды смещения, но для них требуются дополнительные байты, на чтение из памяти которых CPU12 затрачивает определённое время. Поэтому в критичных в плане быстродействия задачах целесообразно использовать короткие пятибайтовые смещения.

Примеры:

STAB opr5,r ;Запись команды STAB с индексной адресацией со ;смещением в 5 бит общем виде.

ADDA ,X ;Сложить содержимое аккумулятора А с данными в ячейке ;памяти, адрес которой равен содержимому регистра X плюс 0.

STAB -10,Y ;Сохранить содержимое аккумулятора B в ячейку памяти, ;адрес которой равен содержимому регистра Y минус 10.

;Примечание. При ассемблировании исходного кода среда разработки ;автоматически преобразует число -10 в дополнительный код.

Индексная адресация IDX1 со смещением в 9 бит

Девятибитные смещения в индексном способе адресации дают диапазон возможных значений от -256 до +255. При этом старший бит числа (бит знака) включается непосредственно во второй байт команды. Остальные же 8 бит смещения размещаются в дополнительный третий байт. При данной адресации в качестве индексных могут использоваться регистры X, Y, SP, или PC.

Примеры:

ADDA opr9,r ;Запись команды ADDA с индексной адресацией со ;смещением в 9 бит в общем виде.

LDAA $FF,X ;Загрузить в аккумулятор А содержимое ячейки ;памяти, адрес которой равен (X) + 255.

LDAB -60,Y ;Загрузить в аккумулятор B содержимое ячейки памяти, ;адрес которой равен (Y) − 60.

Индексная адресация IDX2 со смещением в 16 бит

В этом типе индексной адресации используются 16-разрядные смещения, которые прибавляются к значению базового индексного регистра (X, Y, SP, или PC), тем самым, формируя адрес нужной ячейки. Таким способом можно обратиться к любой ячейке памяти во всём 64 КБ адресном пространстве ($0000..$FFFF). Так как разрядности адресной шины и смещения в этом случае совпадают и равны 16-ти, то не имеет значения, какой знак имеет смещение, если старший бит равен 1 (т.е., например, $FFFF можно расценивать как +65535, так и -1).

Шестнадцатибитное смещение представляется в памяти МК как два дополнительных байта в команде (третий и четвёртый).

Примеры:

20