Universal Serial Bus Specification Revision 2.0

Host |

|

|

Hub |

|

|

(SS: start sp. status |

(data toggle) |

|

|

|

|

CS: comp. sp. status) |

|

|

|

0 |

|

|

SS:Free/x |

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

IN |

st2 |

|

|

|

|

|

|

SS:Pending/x |

uFrame M+1 |

|

|

|

|

|

|

|

CS:Ready/lastdata |

uFrame M+2 |

ct1 |

CSPLIT |

|

|

|

ct2 |

IN |

|

|

|

|

|

|

Hub ignores this |

|

|

|

|

IN.( no match |

|

TRANS_ERR |

|

the Address field) |

|

|

|

|

ce1->ce8 |

|

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

|

ct1 |

|

|

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

|

ch7 |

DATA0 |

cd1 |

CS:Old/lastdata |

|

|

|

|

1 |

|

|

|

|

uFrame M+3 Host does not issue 2nd CSPLIT, |

CS:Free/x |

|

because host already receives |

|

|

DATA0 on previous microframe. |

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

|

because host already receives |

|

|

DATA0 on previous microframe. |

|

uFrame M+5

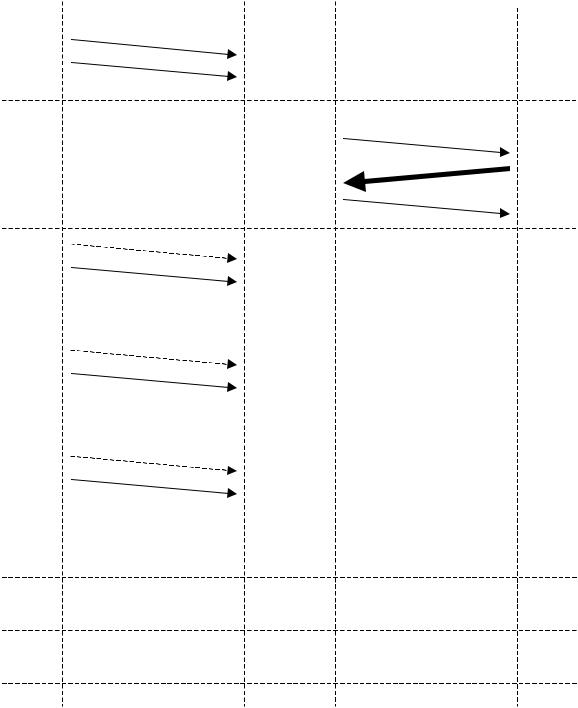

Figure A-66. Normal HS CSPLIT Smash

FS/LS device

(data toggle) 0

(data toggle) 0

IN

DATA0

ACK

1

Universal Serial Bus Specification Revision 2.0

Host |

|

|

Hub |

|

|

(SS: start sp. status |

(data toggle) |

|

|

|

|

CS: comp. sp. status) |

|

|

|

0 |

|

|

SS:Free/x |

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

IN |

st2 |

|

|

|

|

|

|

SS:Pending/x |

uFrame M+1 |

|

|

|

|

|

|

CS:Ready/lastdata |

uFrame M+2 |

ct1 |

CSPLIT |

|

|

ct2 |

IN |

|

|

TRANS_ERR |

|

|

ce1->ce8 |

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

ct2 |

IN |

|

|

TRANS_ERR |

|

|

ce1->ce8 |

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

ct2 |

IN |

|

|

TRANS_ERR |

|

|

ce1->ce7 |

|

|

|

ENDPOINT HALT |

|

uFrame M+3 Host does not issue 2nd CSPLIT, |

CS:Free/x |

|

because this endpoint is already |

|

|

ENDPOINT HALT. |

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

|

because this endpoint is already |

|

|

ENDPOINT HALT. |

|

uFrame M+5

FS/LS device

(data toggle) 0

(data toggle) 0

IN

DATA0

ACK

1

Figure A-67. Normal HS CSPLIT 3 Strikes Smash

Universal Serial Bus Specification Revision 2.0

Host |

|

|

Hub |

|

|

(SS: start sp. status |

(data toggle) |

|

|

|

|

CS: comp. sp. status) |

|

|

|

0 |

|

|

SS:Free/x |

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

IN |

st2 |

|

|

|

|

|

|

SS:Pending/x |

uFrame M+1 |

|

|

|

|

|

|

CS:Ready/lastdata |

uFrame M+2 |

CSPLIT |

|

|

ct1 |

ct1 |

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

DATA0 |

cd1 |

CS:Old/lastdata |

TRANS_ERR |

|

|

ce1->ce8 |

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

ct1 |

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

ch7 |

DATA0 |

cd1 |

|

|

|

|

1 |

|

|

|

uFrame M+3 Host does not issue 2nd CSPLIT, |

CS:Free/x |

because host already receives |

|

DATA0 on previous microframe. |

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

because host already receives |

|

DATA0 on previous microframe. |

|

uFrame M+5

Figure A-68. Normal HS DATA0/1 Smash

FS/LS device

(data toggle) 0

(data toggle) 0

IN

DATA0

ACK

1

Universal Serial Bus Specification Revision 2.0

Host |

|

|

Hub |

|

|

(SS: start sp. status |

(data toggle) |

|

|

|

|

CS: comp. sp. status) |

|

|

|

0 |

|

|

SS:Free/x |

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

IN |

st2 |

|

|

|

|

|

|

SS:Pending/x |

uFrame M+1 |

|

|

|

|

|

|

CS:Ready/lastdata |

uFrame M+2 |

CSPLIT |

|

|

ct1 |

ct1 |

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

DATA0 |

cd1 |

CS:Old/lastdata |

TRANS_ERR |

|

|

ce1->ce8 |

CSPLIT(retry imm.) |

|

ct1 |

|

|

ct1 |

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

DATA0 |

cd1 |

|

TRANS_ERR |

|

|

ce1->ce8 |

CSPLIT(retry imm.) |

|

ct1 |

|

|

ct1 |

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

DATA0 |

cd1 |

|

TRANS_ERR |

|

|

ce1->ce7 |

|

|

|

ENDPOINT HALT |

|

|

uFrame M+3 Host does not issue 2nd CSPLIT, |

CS:Free/x |

because this endpoint is already |

|

ENDPOINT HALT. |

|

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

because this endpoint is already |

|

ENDPOINT HALT. |

|

|

uFrame M+5

FS/LS device

(data toggle) 0

(data toggle) 0

IN

DATA0

ACK

1

Figure A-69. Normal HS DATA0/1 3 Strikes Smash

Universal Serial Bus Specification Revision 2.0

Host |

|

|

Hub |

|

|

(SS: start sp. status |

(data toggle) |

|

|

|

|

CS: comp. sp. status) |

|

|

|

0 |

|

|

SS:Free/x |

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

IN |

st2 |

|

|

|

|

|

|

SS:Pending/x |

uFrame M+1 |

|

|

|

|

|

|

|

CS:Ready/lastdata |

uFrame M+2 |

ct1 |

CSPLIT |

ct1 |

|

|

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

|

ch7 |

DATA0 |

cd1 |

CS:Old/lastdata |

|

|

|

|

1 |

|

|

|

|

uFrame M+3 Host does not issue 2nd CSPLIT, |

CS:Free/x |

|

because host already receives |

|

|

DATA0 on previous microframe. |

|

uFrame M+4

uFrame M+8

uFrame M+9

uFrame M+10

Host does not receive this data. Data toggle is still ‘1’.

Host does not issue 3rd CSPLIT, |

SS:Free/x |

because host already receives |

|

DATA0 on previous microframe. |

|

st1 |

SSPLIT |

st1 |

|

|

st2 |

IN |

st2 |

|

|

|

|

SS:Pending/x |

|

|

|

CS:Ready/lastdata |

ct1 |

CSPLIT |

ct1 |

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

ch7 |

DATA0 |

cd1 |

CS:Old/lastdata |

|

|

|

Figure A-72. Normal FS/LS ACK Smash

FS/LS device

(data toggle) 0

(data toggle) 0

IN

DATA0

ACK

IN

DATA0

ACK

1

Universal Serial Bus Specification Revision 2.0

Host |

|

|

Hub |

|

|

(SS: start sp. status |

(data toggle) |

|

|

|

|

CS: comp. sp. status) |

|

|

|

0 |

|

|

SS:Free/x |

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

IN |

st2 |

|

|

|

|

|

|

SS:Pending/x |

uFrame M+1 |

|

|

|

|

|

|

|

CS:Ready/lastdata |

uFrame M+2 |

ct1 |

CSPLIT |

ct1 |

|

|

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

|

|

|

|

Does not match this |

|

|

|

|

CSPLIT on first |

|

TRANS_ERR |

|

entry of CS.Then |

|

|

HUB does not |

|

ce1->ce8 |

|

|

respond any packet. |

|

ct1 |

CSPLIT(retry imm.) |

|

|

|

ct1 |

|

|

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

|

ch7 |

DATA0 |

cd1 |

CS:Old/lastdata |

|

|

|

|

1 |

|

|

|

|

uFrame M+3 Host does not issue 2nd CSPLIT, |

CS:Free/x |

|

because host already receives |

|

|

DATA0 on previous microframe. |

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

|

because host already receives |

|

|

DATA0 on previous microframe. |

|

uFrame M+5

Figure A-73. Searching No Smash

FS/LS device

(data toggle) 0

(data toggle) 0

IN

DATA0

ACK

1

Universal Serial Bus Specification Revision 2.0

Host |

|

|

Hub |

|

|

(SS: start sp. status |

(data toggle) |

|

|

|

|

CS: comp. sp. status) |

|

|

|

0 |

|

|

SS:Free/x |

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

IN |

st2 |

|

|

|

|

|

|

SS:Pending/x |

uFrame M+1 |

|

|

|

IN

FS/LS device

(data toggle) 0

(data toggle) 0

|

|

|

|

CS1:Ready/moredata |

DATA0 |

uFrame M+2 |

ct1 |

CSPLIT |

ct1 |

|

ACK |

|

|

|

CS2:Ready/lastdata |

|

ct2 |

IN |

|

|

|

ct2 |

|

1 |

|

|

|

|

|

ch5 |

MDATA |

cd2 |

CS1:Old/moredata |

|

|

|

|

|

|

uFrame M+3 |

ct1 |

CSPLIT |

|

CS1:Free/x |

|

|

ct1 |

|

|

|

|

|

|

|

|

ct2 |

IN |

ct2 |

|

|

|

|

|

|

|

|

ch7 |

DATA0 |

cd1 |

CS2:Old/lastdata |

|

|

|

|

|

|

1 |

|

|

|

|

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

|

|

because host already receives |

CS2:Free/x |

|

|

DATA0 on previous microframe. |

|

|

uFrame M+5

Figure A-74. CS Earlier No Smash(HS MDATA and FS/LS Data Packet is on M+1 and M+2)

IN.( no match

IN.( no match  the Address field)

the Address field)

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0