Universal Serial Bus Specification Revision 2.0

Host

(data toggle)

|

0 |

|

|

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

OUT |

st2 |

|

|

|

|

sd1 |

DATA0 |

|

Hub

(SS: start sp. status CS: comp. sp. status)

SS:Free/x

FS/LS device

(data toggle) 0

(data toggle) 0

uFrame M+1 |

|

uFrame M+2 |

ct1 |

|

ct2 |

|

ch6 |

uFrame M+3 |

ct1 |

|

|

ct2 |

|

ch6 |

uFrame M+4 |

ct1 |

|

|

ct2 |

|

ce7 |

|

ce3 |

uFrame M+8 |

|

|

st1 |

|

st2 |

|

sd1 |

uFrame M+9 |

|

uFrame M+10 |

ct1 |

|

ct2 |

|

ch2 |

1 |

|

TRANS_ERR

se1

CSPLIT ct1

OUT

ct2

NYET ch5

CSPLIT ct1

OUT ct2

NYET ch5

CSPLIT ct1

OUT ct2

NYET ch5

SSPLIT(retry)

st1

OUT st2

DATA0 sh1

SS:Pending/x

OUT

DATA0

1

ACK

CS:Ready/ack

CSPLIT

ct1

OUT

ct2

CS:Old/ack

ACK ch2

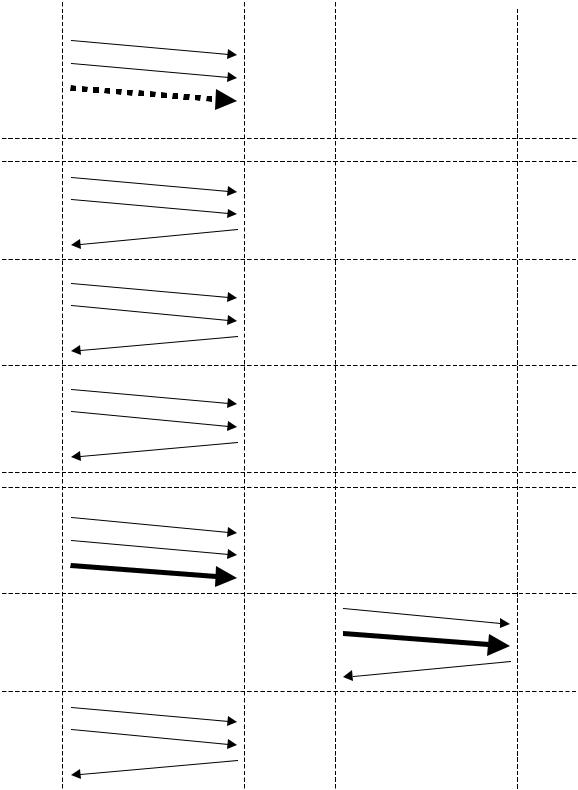

Figure A-48. Normal HS DATA0/1 Smash

Universal Serial Bus Specification Revision 2.0

Host

(data toggle)

|

0 |

|

|

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

OUT |

st2 |

|

|

|

|

sd1 |

DATA0 |

sh1 |

|

|

|

Hub

(SS: start sp. status CS: comp. sp. status)

SS:Free/x

FS/LS device

(data toggle) 0

(data toggle) 0

DATA0

1

ACK

|

|

|

|

CS:Ready/ack |

uFrame M+2 |

ct1 |

CSPLIT |

|

|

|

ct2 |

OUT |

|

|

|

|

|

|

Hub ignores this |

|

|

|

|

OUT because no |

|

TRANS_ERR |

|

match the address |

|

|

|

|

ce1->ce6 |

|

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

|

ct1 |

|

|

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

|

|

ACK |

ch2 |

CS:Old/ack |

|

ch2 |

|

|

|

|

|

1 |

|

|

|

|

uFrame M+3 |

Host does not issue 2nd CSPLIT, |

CS:Free/x |

|

because host already receives ACK |

|

|

on previous microframe. |

|

|

uFrame M+4 |

Host does not issue 3rd CSPLIT, |

SS:Free/x |

|

because host already receives ACK |

|

|

on previous microframe. |

|

|

Figure A-49. Normal HS CSPLIT Smash

Universal Serial Bus Specification Revision 2.0

Host

(data toggle)

|

0 |

|

|

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

OUT |

st2 |

|

|

|

|

sd1 |

DATA0 |

sh1 |

|

|

|

Hub

(SS: start sp. status CS: comp. sp. status)

SS:Free/x

FS/LS device

(data toggle) 0

(data toggle) 0

uFrame M+1

uFrame M+2 |

ct1 |

CSPLIT |

|

ct2 |

OUT |

OUT

DATA0

1

ACK

CS:Ready/ack

Hub ignores this  OUT.( no match

OUT.( no match  the Address field)

the Address field)

TRANS_ERR

ce1->ce6

ct2 OUT

Hub ignores this

OUT.( no match

the Address field)

TRANS_ERR

ce1->ce6

ct2 OUT

TRANS_ERR

ce1->ce5

ENDPOINT HALT

uFrame M+3  Host does not issue 2nd CSPLIT,

Host does not issue 2nd CSPLIT,

because this endpoint is already ENDPOINT HALT.

uFrame M+4  Host does not issue 3rd CSPLIT,

Host does not issue 3rd CSPLIT,

because this endpoint is already ENDPOINT HALT.

Hub ignores this  OUT.( no match

OUT.( no match  the Address field)

the Address field)

CS:Free/x

SS:Free/x

Figure A-50. Normal HS CSPLIT 3 Strikes Smash

Universal Serial Bus Specification Revision 2.0

Host

(data toggle)

|

0 |

|

|

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

OUT |

st2 |

|

|

|

|

sd1 |

DATA0 |

sh1 |

|

|

|

Hub

(SS: start sp. status CS: comp. sp. status)

SS:Free/x

FS/LS device

(data toggle) 0

(data toggle) 0

DATA0

1

ACK

|

|

|

|

CS:Ready/ack |

uFrame M+2 |

ct1 |

CSPLIT |

|

|

|

|

ct1 |

|

|

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

|

|

ACK |

ch2 |

CS:Old/ack |

|

|

|

|

TRANS_ERR |

|

|

|

ce1->ce6 |

|

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

|

ct1 |

|

|

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

|

ch2 |

ACK |

ch2 |

|

|

|

|

|

1 |

|

|

|

|

uFrame M+3 |

Host does not issue 2nd CSPLIT, |

CS:Free/x |

|

because host already receives ACK |

|

|

on previous microframe. |

|

|

uFrame M+4 |

Host does not issue 3rd CSPLIT, |

SS:Free/x |

|

because host already receives ACK |

|

|

on previous microframe. |

|

|

Figure A-51. Normal HS ACK(C) Smash

Universal Serial Bus Specification Revision 2.0

Host

(data toggle)

|

0 |

|

|

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

OUT |

st2 |

|

|

|

|

sd1 |

DATA0 |

sh1 |

|

|

|

Hub

(SS: start sp. status CS: comp. sp. status)

SS:Free/x

FS/LS device

(data toggle) 0

(data toggle) 0

DATA0

1

ACK

CS:Ready/ack

uFrame M+2 |

CSPLIT(retry imm.) |

|

ct1 |

|

ct1 |

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

ACK |

ch2 |

CS:Old/ack |

|

|

TRANS_ERR |

|

|

ce1->ce6 |

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

ct1 |

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

ACK |

ch2 |

|

TRANS_ERR |

|

|

ce1->ce6 |

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

ct1 |

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

ACK |

ch2 |

|

TRANS_ERR |

|

|

ce1->ce5 |

|

|

|

ENDPOINT HALT |

|

|

uFrame M+3 Host does not issue 2nd CSPLIT, |

CS:Free/x |

because this endpoint is already |

|

ENDPOINT HALT. |

|

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

because this endpoint is already |

|

ENDPOINT HALT. |

|

|

Figure A-52. Normal HS ACK(C) 3 Strikes Smash

Universal Serial Bus Specification Revision 2.0

Host

(data toggle)

|

0 |

|

|

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

st2 |

OUT |

st2 |

|

|

|

|

sd1 |

DATA0 |

sh1 |

|

|

|

Hub

(SS: start sp. status CS: comp. sp. status)

SS:Free/x

FS/LS device

(data toggle) 0

(data toggle) 0

DATA0

1

ACK

|

|

|

CS:Ready/ack |

uFrame M+2 |

CSPLIT |

|

|

ct1 |

|

ct1 |

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

|

|

Does not match this |

|

|

|

CSPLIT on first |

|

|

|

entry of CS.Then |

TRANS_ERR |

|

HUB does not |

|

respond any packet. |

ce1->ce6 |

|

|

|

|

|

ct1 |

CSPLIT(retry imm.) |

|

|

ct1 |

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

ch2 |

ACK |

ch2 |

CS:Old/ack |

|

|

|

1 |

|

|

|

uFrame M+3 Host does not issue 2nd CSPLIT, |

CS:Free/x |

because host already receives ACK |

|

on previous microframe. |

|

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

because host already receives ACK |

|

on previous microframe. |

|

|

Figure A-55. Searching No Smash

Universal Serial Bus Specification Revision 2.0

Host |

|

|

Hub |

FS/LS |

(data toggle) |

|

|

(SS: start sp. status |

device |

|

|

CS: comp. sp. status) |

|

|

|

(data toggle) |

0 |

|

|

SS:Free/x |

0 |

uFrame M |

st1 |

SSPLIT |

st1 |

|

|

|

|

|

|

st2 |

OUT |

st2 |

|

|

|

|

|

|

sd1 |

DATA0 |

sh1 |

|

|

|

|

|

|

|

|

SS:Pending/x |

|

uFrame M+1 |

|

|

|

|

OUT

DATA0

1

ACK

ACK

uFrame M+2 |

ct1 |

CSPLIT |

ct1 |

CS:Ready/ack |

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

|

ch6 |

NYET |

ch5 |

|

|

|

|

|

uFrame M+3 |

ct1 |

CSPLIT |

|

|

|

|

ct1 |

|

|

|

|

|

|

ct2 |

OUT |

ct2 |

|

|

|

|

|

|

|

ACK |

ch2 |

CS:Old/ack |

|

ch2 |

|

|

|

|

|

1 |

|

|

|

|

uFrame M+4 Host does not issue 3rd CSPLIT, |

SS:Free/x |

|

because host already receives ACK |

CS:Free/x |

|

on previous microframe. |

|

|

uFrame M+5

Figure A-56. CS Earlier No Smash(HS NYET and FS/LS Handshake Packet is Done by M+2)

Universal Serial Bus Specification Revision 2.0

Host

(data toggle)

0 |

|

|

uFrame M |

st1 |

SSPLIT |

|

st2 |

OUT |

|

sd1 |

DATA0 |

uFrame M+1 |

|

|

uFrame M+2 |

ct1 |

CSPLIT |

|

ct2 |

OUT |

|

ch6 |

NYET |

|

|

uFrame M+3 |

ct1 |

CSPLIT |

|

|

ct2 |

OUT |

|

ch6 |

NYET |

|

|

uFrame M+4 |

ct1 |

CSPLIT |

|

|

ct2 |

OUT |

|

ch2 |

ACK |

|

|

1 |

|

|

uFrame M+5 |

|

|

Hub

(SS: start sp. status CS: comp. sp. status)

SS:Free/x

st1

st2

sh1

SS:Pending/x

ct1

ct2

ch5

OUT

FS/LS device

(data toggle) 0

(data toggle) 0

ct1 |

DATA0 |

ct2 |

1 |

|

ACK |

ch5 |

CS:Ready/ack |

|

|

SS:Free/x |

ct1 |

|

ct2 |

|

ch2 |

CS:Old/ack |

|

|

CS:Free/x |

Figure A-57. CS Earlier No Smash(HS NYET and FS/LS Handshake Packet is Done by M+3)

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0 OUT.( no match

OUT.( no match  the Address field)

the Address field)

Host does not issue 2nd CSPLIT,

Host does not issue 2nd CSPLIT, Host does not issue 3rd CSPLIT,

Host does not issue 3rd CSPLIT, OUT.( no match

OUT.( no match  the Address field)

the Address field)

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

(data toggle) 0

Device does

Device does not receive

not receive this data.

this data. Data toggle

Data toggle  is still ‘1’.

is still ‘1’.

(data toggle) 0

(data toggle) 0

ACK

ACK

(data toggle) 0

(data toggle) 0