timer

.doc32

действиями являются:

вход GATE применяется для разрешения и запрещения входа CLK;

вход GATE вызывает реинициализацию счетчика;

вход GATE прекращает счет и формирует высокий уровень на выходе OUT;

при достижении 0 счетчик выдает сигнал OUT и останавливается;

при достижении 0 счетчик выдает сигнал OUT и автоматически реинициализируеюя из регистра начального счета.

Режимы могут также определяться комбинациями перечисленных возможностей Рассмотрим, например, применение интервального таймера в операционной системе разделением времени. В этом случае на вход CLK подаются сигналы синхронизации, а выход OUT подключается к линии запроса прерывания, возможно, немаскируемого прерывания. Вход GATE здесь не требуется. При включении системы в регистр начального счета загружается значение

начальный счет = частота синхронизации X Т,

где Т - продолжительность каждого временного кванта в секундах. Задается такой режим, что при достижении счетчиком 0 содержимое регистра начального счета вновь загружается в счетчик, а выход OUT становится активным. Поскольку сигнал OUT используется как запрос прерывания, процедура прерывания для переключения программ будет выполняться с интервалом Т секунд.

9 .3.1.

ПРОГРАММИРУЕМЫЙ

ИНТЕРВАЛЬНЫЙ ТАЙМЕР На

рис. 9.26 представлена схема интервального

таймера/счетчика событий 8254 фирмы

Intel.

В нем имеются три одинаковые счетные

схемы со своими входами

CLK

и GATE

и выходом OUT.

Каждая схема имеет регистр управления

и состояния, регистр счетчика (CR)

для приема начального счета, счетного

элемента (СЕ) , который выполняет счет,

но непосредственно процессору

недоступен, и выходного регистра-защелки

(OL)

для фиксации содержимого

СЕ, так что его может считать процессор.

Полагается, что CR,

СЕ

и OL

представляют собой пары 8-битных

регистров. (Реальные схемы несколько

отличаются от приведенных, но для

программиста рисунок абсолютно

точен.)

.3.1.

ПРОГРАММИРУЕМЫЙ

ИНТЕРВАЛЬНЫЙ ТАЙМЕР На

рис. 9.26 представлена схема интервального

таймера/счетчика событий 8254 фирмы

Intel.

В нем имеются три одинаковые счетные

схемы со своими входами

CLK

и GATE

и выходом OUT.

Каждая схема имеет регистр управления

и состояния, регистр счетчика (CR)

для приема начального счета, счетного

элемента (СЕ) , который выполняет счет,

но непосредственно процессору

недоступен, и выходного регистра-защелки

(OL)

для фиксации содержимого

СЕ, так что его может считать процессор.

Полагается, что CR,

СЕ

и OL

представляют собой пары 8-битных

регистров. (Реальные схемы несколько

отличаются от приведенных, но для

программиста рисунок абсолютно

точен.)

Обращения к регистрам производятся в соответствии с табл. 9.3.

Таблица 9.3

Обращения к регистрам таймера/счетчика 8254

Все остальные комбинации приводят к тому, что линии данных переводятся в высокоимпедансное состояние. Когда А1 = АО = 1, выполнение записи в регистр управления или выдачи приказа зависит от старшего бита выводимого байта. В последних трех комбинациях считывание OL или регистра состояния определяет предыдущий приказ.

Имеются два вида приказов. Приказ фиксации счетчика заставляет соответствующий OL зафиксировать содержимое СЕ счетчика, определяемого двумя старшими битами приказа. Приказ обратного считывания фиксирует комбинацию СЕ или "готовит" комбинацию регистров состояния для считывания. Подготовка регистра состояния означает

Рис. 9.26. Схема таймера/счетчика 8254

его считывание, когда в следующей операции считывания осуществляется ввод из счетчика. Состояния 00, 01 и 10 двух старших бит показывают

34

приказ фиксации счетчика, а состояние 11 - приказ обратного считывания. В приказе фиксации биты 5 и 4 должны быть нулевыми, а остальные биты не используются. Приказ обратного считывания имеет следующий формат:

![]()

Если бит COUNT = 0, фиксируются СЕ всех счетчиков, биты CNT которых содержат 1. Если, например, CNTO = CNT2 = 1 и CNT1 = 0, то СЕ в счетчиках 0 и 2 фиксируются, "»в счетчике 1 не фиксируется. Аналогично STAT = 0 вызывает подготовку регистров

Рис 9 27 Регистры управления и состояния счетчиков

состояний счетчиков для ввода. Действия по фиксации и подготовке допускается указывать в одном приказе.

Форматы регистров управления и состояния показаны на рис. 9.27. Если два старших бита равны 1, они задают приказ обратного считывания; в противном случае они определяют счетчик. Если указан счетчик и биты 5-4 содержат нули, то имеет место приказ фиксации, который направляется в регистр управления выбираемого старшими битами счетчика. Когда же комбинация в битах 5-4 отличается от 00, она указывает тип ввода из OL или вывода в CR.

Таймер/счетчик имеет следующие режимы работы (через N обозначен начальный счет)

Режим 0 (прерывания по концу счета). Сигнал GATE = 1 разрешает счет, а GATE = О запрещает счет, причем GATE не влияет на выход OUT. Содержимое CR передается в СЕ по первому импульсу CLK после того, как процессор осуществил запись в CR, независимо от сигнала на входе GATE Импульс, который загружает СЕ, не учитывается при счете. На выходе OUT

35

формируется низкий уровень при записи в регистр управления, который сохраняется до достижения счетчиком 0. Режим 0 предназначен в основном для счета событий.

Режим 1 (аппаратно перезапускаемый одновибратор). После загрузки значения N в CR переход 0 -* 1 на входе GATE вызывает загрузку СЕ, переход 1 -»0 на выходе OUT и запускает счет. Когда счетчик достигает 0, на выходе OUT формируется высокий уровень; таким образом, результатом является отрицательный импульс на выходе OUT с продолжительностью N периодов синхронизации

Режим 2 (периодический интервальный таймер) После загрузки значения N в CR следующий импульс синхронизации осуществляет передачу из CR в СЕ На выходе OUT возникаем переход 1 -^ 0. когда счетчик достигает 0 низкий уровень сохраняется в течение одною импульса CJ-K Затем на выходе OUT появляется высокий уровень, производится повторная загрузка СЕ из CR, в результате на выходе 01JI появляется отрицательный импульс через N тактов синхронизации Сигнал GATE =- 1 разрешает счет, a GATE = 0 запрещает. Переход 0 - 1 на входе GATE вызывает реинициализацию счета следующим импульсом синхронизации. Данный режим применяется для реализации периодического интервального таймера

Режим 3 (генератор прямоугольного сигнала). Аналогичен режиму 2, но на выходе OUT формируется низкий уровень при достижении половины начального счета; этот уровень сохраняется до достижения счетчиком 0. Как и прежде, сигнал GATE разрешает и запрещает счет, а его переход 0-1 реинициализирует счет. Этот режим применяется в генераторах, определяющих скорость передачи в бодах.

Режим 4 (программно-запускаемый строб) . Аналогичен режиму 0, но на выходе OUT в процессе счета действую высокий уровень, а при достижении счетчиком 0 появляется отрицательный импульс с продолжительностью в один такт синхронизации

Режим 5 (аппаратно-запускаемый строб с перезапуском) После загрузки CR переход 0 - 1 на входе GATE вызывает передачу из CR в СЕ следующим импульсом CLK. В процессе счета на выходе OUT действует высокий уровень, а при достижении счетчиком 0 формируется отрицательный импульс с продолжительностью в один период CLK Сигнал GATE может в любой момент времени реинициализировать счет.

Начальное значение счета 0 во всех режимах интерпретируется как 216 или 104 в зависимости от формата счета. Мы привели общие принципы работы микросхемы 8254, а подробное описание содержится в фирменных материалах.

36

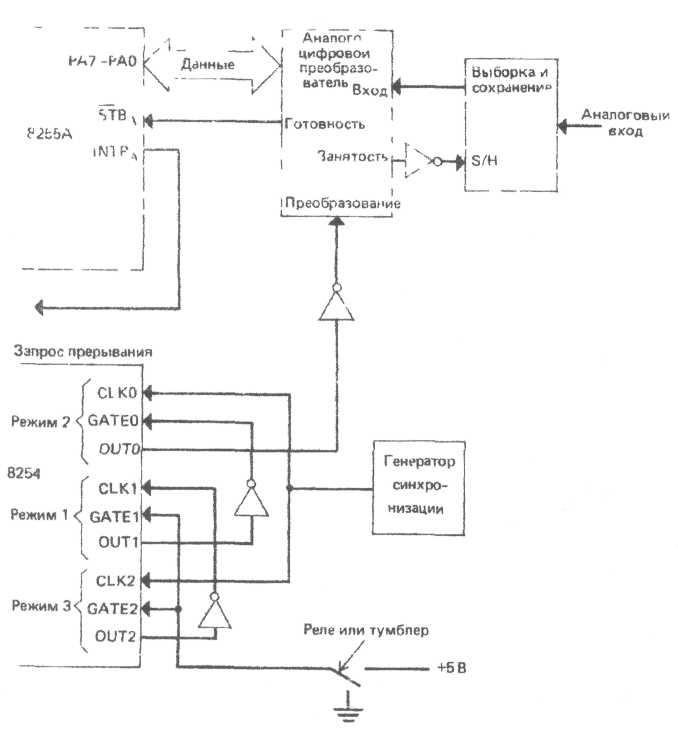

9.3.2. ПРИМЕНЕНИЕ ТАЙМЕРА В АНАЛОГО-ЦИФРОВОЙ ПОДСИСТЕМЕ

Применение микросхемы 8254 в качестве программируемого генератора частоты отсчетов в аналого-цифровой подсистеме представлено на рис. 9 28. Благодаря наличию в ней трех счетчиков можно не только программировать частоту опросов, но и определять временные интервалы, в течение которых берутся отсчеты. Предположим, что счетчик О работает в режиме 2, счетчик 1 - в режиме 1, счетчик 2 - в режиме 3 и что начальные значения для них равны L, М и N. Если F - частота синхронизации, то на входе CLK1 действует частота F/N и на выходе OUT1 формируется импульс с продолжительностью MN/F. Следовательно, в интервале MN/F секунд на выходе OUTO появляются импульсы с частотой F/L. При подключении OUTO на вход "преобразование" аналого-цифрового преобразователя за MN/F секунд будут формироваться отсчеты с частотой F/L после того, как все три счетчика инициализированы и реле или тумблер замыкаются. После передачи в порт А преобразованного отсчета формируется запрос прерывания INTR, и процедура прерывания вводи г отсчет в процессор На рис 9.29 приведена последовательность инициализации системы Предполагается, что таймер/счетчик 8254 имеет адреса 0070-0073; переменные LCNT, MCNT и NCNT содержат L, М и N, L и N меньше 256. Последовательность инициализации задает режимы счетчиков и загружает начальные значения в CR. Начальные значения L и N представлены в двоичном формате, а значение М -в BCD-формате

9.4. КЛАВИАТУРА И ИНДИКАТОР

Пульты управления (или консоли) небольших дешевых систем часто реализуются как устройства ввода и вывода простых клавиатуры и индикатора. С помощью клавиатуры данные, адреса памяти и машинные коды вводятся в удобном 16-ричном формате

37

ввода приказов управления При выводе адреса памяти и данные

отображаются на светодиодных индикаторах.

941 СХЕМА КЛАВИАТУРЫ

В отличие от терминала клавиатура с механическими контактами, клавишные переключатели которой представлены матрицей, не имеют никиких электронных схем. На рис 9. 30 показано подключение 64 клавишной клавиатуры к микрокомпьютеру через два параллельных порта ввода-вывода, например, микросхемы 8255А При нажатии кла

38

Рис 9 30 Организация механической клавиатуры

виши соответствующие строка и столбец замыкаются, образуя соединение. Обнаруживая позиции строки и столбца, в которых произошло замыкание контактов, определяют кодовое слово соответствующее нажатой клавише Данный процесс называется сканированием клавиатуры и реализуется следующим образом. Выходной порт посылает сигнал 0 в строку 0 и сигналы 1 во все остальные строки. Затем считываются и проверяются линии столбцов. Если в строке 0 нет сигнала 0, процесс повторяется для строки I, затем для строки 2 и т д. Когда же фиксируется 0, обнаруживается нажатая клавиша, позиция строки которой известна по выводимой комбинации, а позиция столбца по результату ввода Объединяя, позиции строки и столбца обнаруженного 0, можно образовать однозначное слово, показывающее положение нажатой клавиши.

С клавиатурой связаны две сложности: дребезг контактов и одновременное нажатие нескольких клавиш. Когда клавиша нажимается или отпускается, ее контакт несколько раз перескакивает ("дрожит") из одного состояния в другое до перехода в устойчивое замкнутое или разомкнутое положение. Продолжительность дребезга не постоянна, но обычно меньше 10 мс. Чгобы предотвратить обнаружение ложных срабатываний клавиш, замыкания контактов из-за дребезга необходимо игнорировать - эта операция называется

39

подавлением дребезга. Подавление дребезга осуществляется аппаратно или программно, но программный подход ведет к чрезмерным потерям времени процессора. Наиболее простое решение проблемы одновременного срабатывания нескольких клавиш заключается в том, чтобы сканировать весь массив и вводить замыкания в порядке их обнаружения.

9.4.2. СХЕМА ИНДИКАТОРА

Имеется много разновидностей цифровых и буквенно-цифровых индикаторов. Для индикации 16-ричных цифр обычно применяются семисегментные светодиодные индикаторы (рис. 9.31) . Цифра в семисегментном коде подается на входы a-g и DP (десятичная точка). В зависимости от типа индикатора (с общим анодом или с общим катодом) активные сигналы имеют высокий или низкий уровень. Сегмент начинает светиться, когда соответствующий светодиод смещен в прямом направлении.

Рис. 9.31. Типичный семисегментный светодиодный индикатор (д), индикатор с общим анодом (б) и общим катодом (в)

40

Рис. 9.32. Восьмиразрядный индикатор

На рис. 9.32 показан многоразрядный индикатор, образованный из 8 элементов. Чтобы не применять в каждом элементе регистр-защелку данных, все элементы подключены к двум 8-битным параллельным портам и работают в мультиплексном режиме. Все элементы разделяют общие линии сегментов, а с помощью линий выбора разряда в любой момент времени выбирается только один элемент. Каждый индикатор включается на 1 мс, а после прохождения всех разрядов последовательность операций повторяется, начиная с первого разряда. Таким образом, индикаторы периодически регенерируют, создавая иллюзию непрерывно работающего многоразрядного индикатора.

41

Рис. 9.33. Точечно-матричный 16-ричный индикатор

Так как типичный средний ток включенного сегмента достигает 20 мА и в каждом разряде может светиться несколько сегментов, суммарный ток превышает нагрузочную способность обычного ТТЛ-вентиля. Следовательно, в индикаторе потребуются драйверы разрядов и драйверы сегментов. Если напряжения на базе транзистора драйвера разряда мало, этот транзистор включается и подсоединяет индикатор к источнику +5 В. Если напряжение на базе транзистора драйвера сегмента мало, этот транзистор включается и через сегмент начинает протекать ток. Кроме того, так как падение напряжения на смещенном в прямом направлении диоде сегмента постоянно, для ограничения тока последовательно с каждым сегментом включается резистор, защищающий индикатор и драйвер. Расчетное сопротивление резистора определяется требуемой яркостью свечения.

Еще один тип индикатора 16-ричных цифр показан на рис. 9.33. В этом индикаторе TIL311 применяется точечная матрица из 20 светодиодов. На его вход подается 4-битное двоичное число, которое сам индикатор преобразует в видимое изображение эквивалентной 16-ричной цифры. Благодаря встроенным регистру-защелке и драйверам постоянного тока входы этого индикатора ТТЛ-совместимы. Входной регистр-защелка запоминает данные, и регенерации не требуется.

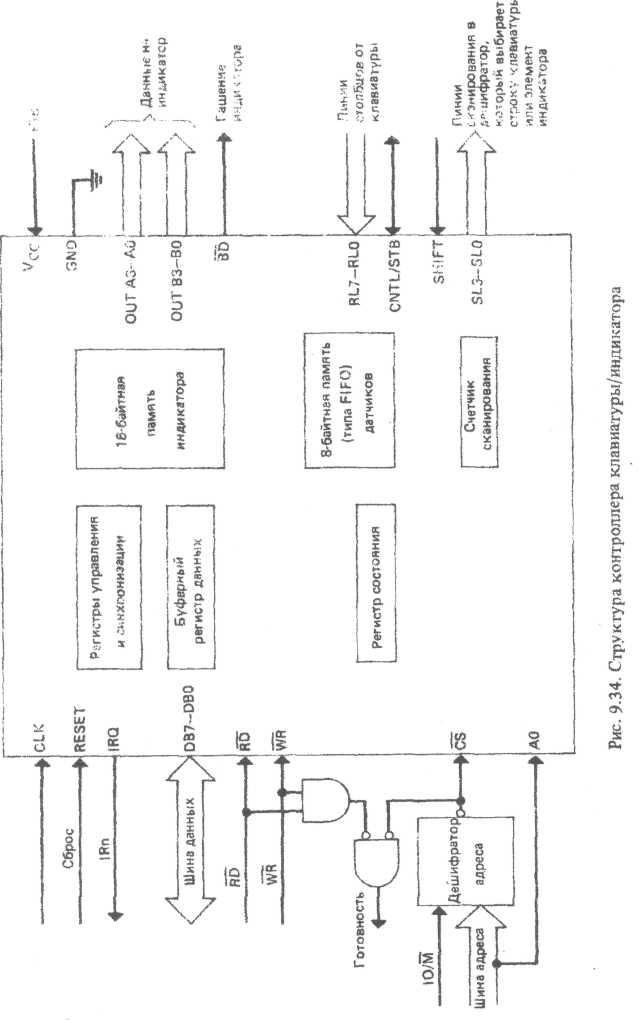

9.4.3. КОНТРОЛЛЕР КЛАВИАТУРЫ/ИНДИКАТОРА

Хотя подключения клавиатуры и многоразрядного индикатора к параллельным портам ввода-вывода в схемном отношении просты, при вводе и выводе процессор должен выполнять процедуры сканирования клавиатуры и регенерации индикатора. Микросхема 8279 контроллера клавиатуры/индикатора освобождает процессор от выполнения длительных операций сканирования и регенерации.

Общая структура контроллера 8279 и его интерфейс с шиной представлены на рис. 9.34. Регистры управления и состояния разделяют нечетный адрес, а

буферный регистр данных имеет четный адрес. Адресация регистров осуществляется в соответствии с табл. 9.4.

Таблица 9.4

Адресация регистров контроллера 8279

44

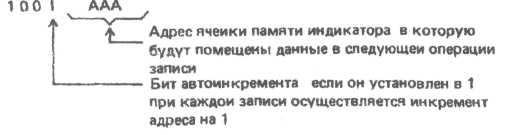

Считывание памяти датчиков (FIFO) Определяет, что считывание из буферного регистра данных будет вводить байт из памяти FIFO, и, если контроллер находится в режиме датчиков, показывает, какая строка считывается Этот приказ необходимо подать до ввода данных из памяти FIFO Формат приказа

Отметим, что, если режим ввода является режимом сканирования клавиатуры, считывание всегда производится из байта, который был помещен в FIFO первым, следовательно, биты I и ААА игнорируются

Запись в память индикатора. Показывает, что запись в буферный регистр данных будет помещать данные в память индикатора. Этот приказ необходимо выдать до того, как процессор будет выводить в контроллер индицируемые символы Формат приказа

Контроллер 8279 предлагает два варианта обработки ситуации, когда примерно в одно и тоже время нажимаются несколько клавиш. Вариант 2 клавишной блокировки: если вторая клавиша нажимается в то же время, когда подавляется дребезг первой, в FIFO будет помещено кодовое слово клавиши, которая освобождается последней.