22

процедура обработки ошибки, которая обычно проверяет отдельные биты ошибок, печатает соответствующее сообщение и сбрасывает биты ошибок.

Ввод символа автоматически сбрасывает бит RxRDY, поэтому если другой символ не принят до начала внутреннего цикла, внутренний цикл должен повторяться до тех пор, пока следующий входной символ не установит RxRDY = 1. Если входные символы имеют меньше 8 бит, неиспользуемые старшие биты в буферном регистре данных всегда возвращаются в состояние 0. Бит паритета не передается в процессор, поэтому контроль ошибок паритета можно осуществить только по состоянию бита ошибки паритета в регистре состояния. Когда при выводе длина символов меньше 8 бит, ненужные старшие биты в буферном регистре выходных данных игнорируются.

9.2. Параллельная связь

Параллельная связь осуществляется одновременной передачей нескольких бит по отдельным линиям. Ее преимущество по сравнению с последовательной связью заключается в том, что для линий с заданной максимальной двоичной скоростью обеспечивается более высокая скорость передачи информации. Недостатком же является, конечно, стоимость дополнительных пиний, и так как расходы увеличиваются с расстоянием, ' параллельная связь применяется на большие расстояния, если только требуется высокая скорость передачи данных.

В отличие от последовательной связи четкие стандарты на параллельную связь отсутствуют. Параллельные передачи выполняются либо простым помещением данных в буферный регистр выходных данных интерфейса или восприятием данных из буферного регистра входных данных интерфейса, либо ими управляют сигналы квитирования и (или) синхронизации. Обычно, одновременно передается один символ (или другая единица информации) и необходимости определения конца символа или начала передачи не возникает. Четко определенный формат синхронной или асинхронной передачи отсутствует, но, если действия устройства и интерфейса координирует сигнал синхронизации, передача считается синхронной. Если же применяются только квитирующие сигналы, передача считается асинхронной.

Интерфейс можно спроектировать только на вывод, только на ввод, на ввод и вывод по отдельным наборам линий, или выполнять ввод-вывод по одному набору двунаправленных линий. Если интерфейс подключен к строчному принтеру, т должен только выводить данные, а если он обслуживает карточный считыватель, интерфейс должен только вводить данные. В интерфейсе, обслуживающем перфоленточные считыватель и перфоратор, потребуются один набор входных линий и один набор выходных линий, но в интерфейсе для устройства, которое не производит одновременные ввод и вывод данных, можно применить один набор двунаправленных линий.

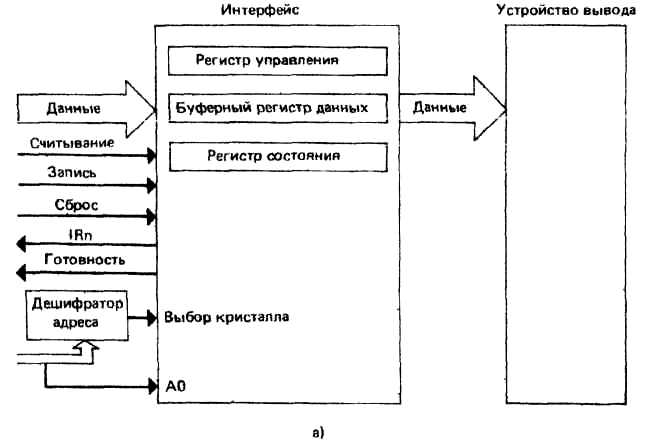

На рис. 9.20, а показан типичный выходной параллельный интерфейс, в котором отсутствуют линии управления. В этом случае содержимое буферного регистра

данных постоянно выдается на линии данных, связывающие интерфейс и устройство вывода. Если устройство вывода состоит из регистра-защелки и управляемого им набора реле, компьютер может управлять этими реле, просто помещая данные в буферный регистр данных. На рис. 9.20, б изображен типичный параллельный интерфейс с линиями квитирования и отдельными подключениями к периферийному устройству для ввода и вывода. В этом случае при вводе данные сначала помещаются на шину данных, а затем на линии готовности входных данных устанавливается 1. Интерфейс должен отреагировать загрузкой данных в буфер входных данных и формированием 1 на пинии подтверждения входных данных.

Рис. 9.20. Типичные интерфейсы параллельной связи: а — только ввод; б — ввод-вывод

При получении подтверждения устройство снимает сигналы данных и готовности. Когда интерфейс принял данные, он устанавливает бит состояния "готовность" и, возможно, посылает сигнал запроса прерывания. После того как процессор вводит данные, интерфейс сбрасывав бит состояния "готовность" и

24

переводит линии данных в высокоимпедансное состояние. Если был сделан запрос прерывания, он обрабатывается обычным образом

При выводе интерфейс устанавливает бит состояния "готовность" и, возможно, формирует запрос прерывания, когда буфер выходных данных освободился- После того как процессор выводит данные, интерфейс сбрасывает бит состояния "готовность", помещает данные на шину выходных данных и сигналичируе устройству по линии готовности выходных данных. Когда устройство готово воспринять данные, оно загружает их в регистр-защелку, а затем возвращает подтверждение. После этого интерфейс снимает сигнал готовности выходных данных и вновь устанавливает бит состояния "готовность".

9.2.1. ПРОГРАММИРУЕМЫЙ ПЕРИФЕРИЙНЫЙ ИНТЕРФЕЙС Примером параллельного интерфейса служит микросхема 8255А программируемого периферийного интерфейса. Как показано на рис. 9.21, она имеет регистр управления и три отдельно адресуемых порта А, 3 и С. Обращение к 825 5А определяет сигнал CS, а направление обращения - сигналы ТШ и WR\ Адресуемый регистр определяют сигналы на входах А1 и АО. Следовательно, младший адрес порта, назначаемый 8255А, должен быть кратным 4. Полная адресация 8 25 5 А содержится в табл 9.2

Таблица 9.2