Каскадирование дешифраторов

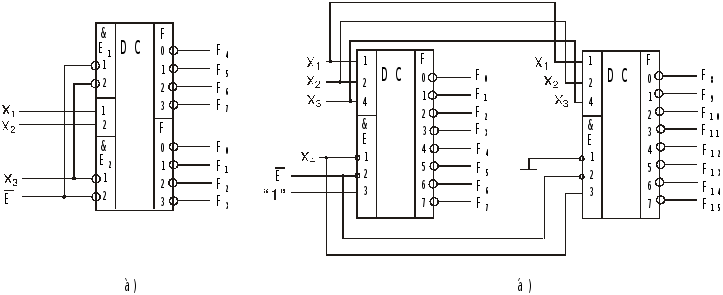

Дешифраторы, имеющие входы разрешения дешифрации, можно соединять для увеличения числа комбинаций. Например, из ИД4, сдвоенного дешифратора 2ґ4, введением дополнительных связей можно получить дешифратор 3ґ8 (рис. 47, а).

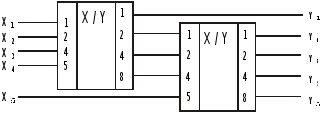

Объединением двух дешифраторов ИД7 (3ґ8) реализуется дешифратор 4ґ16 (рис. 47, б).

Рис. 47

Параллельный регистр с дешифрацией записи в триггеры

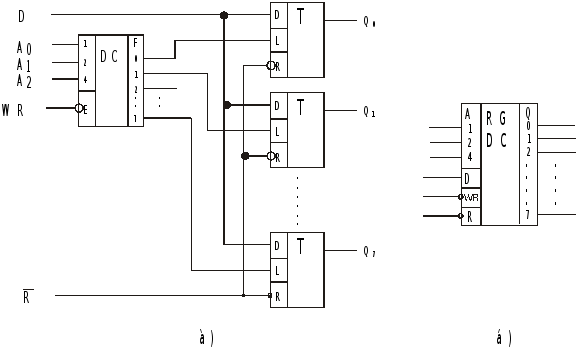

Для расширения функциональных возможностей ИМС усложняют их схемотехнику, объединяя в одном корпусе два или несколько функциональных узлов. Например, ИР30 – 8-разрядный параллельный регистр с дешифрацией выходного адреса. В связи с тем, что в ИМС входят два функциональных узла дешифратор и регистр, то на УГО используются два обозначения. На рис. 48 представлены функциональная схема дешифратора с регистром ИР30 (а) и его УГО (б).

По

сигналу

дешифратор определяет номер триггера,

в который записываются входные данные.

дешифратор определяет номер триггера,

в который записываются входные данные.

Рис. 48

Шифраторы

Шифраторы выполняют обратное дешифраторам преобразование, т.е. на вход шифратора подается унитарный код, а на выходе формируется соответствующий двоичный код. Приведенная таблица описывает шифратор 4ґ2.

Таблица состояний шифратора 4ґ2.

|

F3 |

F2 |

F1 |

F0 |

A1 |

A0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

|

0 |

1 |

|

0 |

1 |

|

|

1 |

0 |

|

1 |

|

|

|

1 |

1 |

Для шифратора должно выполняться условие Fi• Fj=0, при i№j. Если сигналы Fi поступают от независимых источников, то это условие невыполнимо. В этом случае каждому входу необходимо назначить свой приоритет. Принято считать, что чем больше номер входа i, тем выше его приоритет. Шифратор выдает двоичный код числа i, если Fi=1, а на все входы Fj, имеющие больший приоритет, поданы «нули». Такие шифраторы называются приоритетными. Функциональное обозначение шифраторов ИВ ( на УГО ИМС – PRCD – приоритетный шифратор).

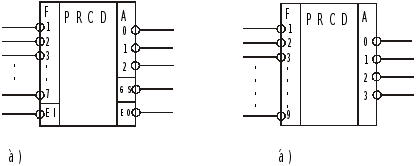

В качестве примера ниже приведены некоторые типы ИМС шифраторов.

ИВ1 – шифратор 8ґ3 (рис. 49, а). ИВ2 аналогичен ИВ1, но имеет выходы с Z-состоянием. EI – выключение шифратора. GS (Group Signal) – выходной сигнал, говорящий о наличии хотя бы одного входного Fi, при включенном шифраторе, т.е. при EI=1 и Fi=1, хотя бы для одного i, GS=1. ЕО – выключение выхода, указывающий на отсутствие сигналов на входе при включенном шифраторе, т.е. при EO=1 и EI=1 Fi=0 для всех i. Выходной двоичный код можно считывать с шифратора только при GS=1. ИВ3 – приоритетный шифратор 10ґ4 (десятая комбинация - на все входы поданы лог. «0», на выходе – активный выход АО)(рис. 49, б).

Рис. 49

Одним из важных приложений шифраторов является построение преобразователей произвольного n-разрядного кода в N-разрядный унитарный код. Например: преобразование 8-разрядного кода, для разрядов которого установлены определенные приоритеты, в 8-разрядный унитарный код (рис. 50). В данной схеме преобразователя

Рис. 50

шифратор преобразует произвольный код в двоичный 3-х разрядный, а дешифратор 3ґ8 преобразует этот код в инверсный унитарный.

Преобразователи кодов

Преобразователи кодов используются для дешифрации и шифрации цифровой информации. Основное отличие преобразователей кодов от стандартных дешифраторов и шифраторов заключается в том, что преобразователи могут иметь произвольное количество входов и выходов, причем соотношение между числом входов и числом выходов может быть любым.

Преобразователи кодов можно подразделить на два типа:

с весовым преобразованием, когда каждый разряд входного цифрового кода имеет свой «вес», т.е. каждый разряд числа определяется его положением;

с невесовым преобразованием, когда код входного числа целиком определяет сигнал на выходе.

К первому типу относятся преобразователи, преобразующие различные цифровые коды, отличные от двоичного.

Ко второму типу относятся в основном преобразователи для систем индикации (семисегментные и аналогичные), в которых символ индикатора формируется отдельными элементами.

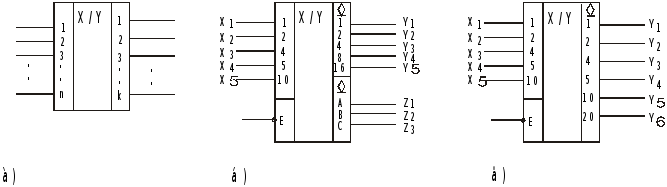

Общее УГО преобразователей кодов представлено на рис. 51, а.

Рис. 51

Все преобразователи реализуются на базе комбинационных схем, которые формируются по заданному алгоритму на программируемых ПЗУ.

В качестве готовых ИМС выпускаются два преобразователя кодов:

ПР6 – преобразователь двоично-десятичного кода в двоичный;

ПР7 – преобразователь двоичного в двоично-десятичный.

На рис. 51, б,в представлены ИМС шифратора ПР6 и ПР7.

Выходы A, B, C используются для формирования дополнения до 9 или 10 по определенному алгоритму.

Функциональная схема ПР6 представлена на рис. 52. Такие преобразователи реализуются на основе масочных ПЗУ. Значения входных кодов Хi (i= 1...5) задают адреса ПЗУ и ячейки, из которых выбирается выходной кодYi.

Рис. 52

Кроме рассмотренных ИМС, выпускаются специализированные ИМС индикации с преобразователями кодов. КМОП ИМС 176ИЕ3, 176ИЕ4 представляют собой счетчики, на выходах которых включены преобразователи двоичного кода в семисегментный.